基于LXI总线的高速高精度数据采集器的研制

唐源

(桂林电子科技大学电子工程与自动化学院 广西壮族自治区桂林市 541004)

LXI(LAN eXtension for instrumentation)总线技术是成熟的以太网技术在测试自动化领域应用的拓展[1]。基于LXI 总线的数据采集设备是一台嵌入式智能设备,通过LXI 网络接口可以接收客户端远程发送的指令,不需要额外的机箱和0 槽即可实现异地远程数据采集,因此基于LXI 总线的数据采集仪器能够应用于快速组建分布式结构的自动测试系统中[2][3][4]。

目前,国内LXI 仪器种类较少、通用性较差且在精度和性能方面,与国际领先水平还有一定差距[5][6]。研制基于LXI 的高速高精度采集器对促进我国自动测试系统领域发展、拉近与国外领先水平距离都有重大的意义[7][8]。

1 系统组成及原理

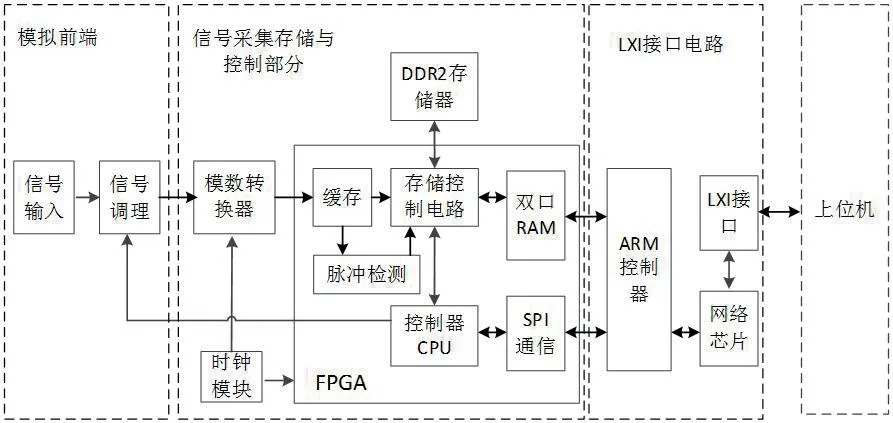

结合国内外相关产品的设计方法,采用目前基于以太网技术的新一代总线LXI 技术,提出LXI 总线的高速高精度数据采集器的研制方案。数据采集器总体设计主要包括模拟前端、信号采集存储与控制、LXI 接口电路三部分。

如图1所示为LXI 总线的数据采集器的组成框图,其中模拟前端主要是对输入信号进行相应的调理,如阻抗的变换、或对小信号适当放大而对大信号进行适当衰减等,最终将输入信号调理至模数转换器ADC(Analog-to-Digital Converter)要求的输入范围;数据的采集与存储控制是数据采集系统的主要组成部分,主要的工作原理为输入的模拟信号经ADC 转换为数字信号,在FPGA(Field-Programmable Gate Array)中对该数字信号进行初步的处理,如数据的拼接与缓存等,之后将数据写入高速存储器DDR2(Double Data Rate 2)中,同时在FPGA 内部配置双口RAM(random access memory)接口,和ARM(Acorn RISC Machine)控制器进行数据交互;LXI 接口电路主要负责海量数据的传输,上位机通过LXI 网络接口可以实现远程访问与控制仪器设备。本系统中采用ARM9 控制器,在ARM 中移植Linux 嵌入式系统,能够较好地提高数据采集系统的稳定性与实时性。

2 系统硬件设计

2.1 LVDS接收器

数据采集系统中采用TI 公司生产的ADC 器件ADS4126 作为采集电路的模数转换器。ADS4126 的主要参数为:位数为12bit,采样率为160MSa/s。ADS4126 为差分输入输出,相比于单端信号,差分信号具有较高的共模噪声抑制能力,极大地提高了系统的信噪比[9][10]。ADS4126 数据输出的速率可通过编程改变,当输出为DDR 模式时,数据输出速率达320M。采用FPGA 接收ADC 的输出数据一般来说有两种方法。方法一:根据ADC 芯片手册中数据输出与锁存时钟的时序要求,在FPGA 中通过编写程序或设计电路实现数据的接收。方法二:直接采用FPGA 自带的功能宏模块LVDS(Low-Voltage Differential Signaling)接收器完成对ADC 输出数据的接收。在数据采样中,由于采样的速度过高,用户设计的功能模块难以满足ADC 的工作时序要求,因此对于ADC 输出数据的接收与存储,采用宏模块LVDS 接收器的方法较为合适。

图1:系统框图

图2:LVDS 接收器

如图2所示为LVDS 接收器与一级缓存电路的设计。时钟芯片产生160MHz 时钟作为ADC 的采样时钟,即图2 中AD1_CLKOUT2 时钟信号。为保证数据在接收与处理过程中的稳定性与准确度,通过串转并对数据传输的时钟进行了降速处理,宏模块LVDS 接收器按照1:8 的比率接收ADC 输出数据,从而接收器输出时钟频率降为采样时钟的1/8,即图2 中rx_outclock 时钟为20MHz。

ADS4126 数据的输出方式是DDR,即在一个采样时钟周期,ADC 实际的数据输出量为AD1_DATA[5..0]的2 倍,为12bit,从而输入端每8 组数据经LVDS 接收器处理后,数据位宽扩展为96bit。LVDS 接收器的输出96bit 的数据如图2 中rx_out[95..0],该数据共由8 个样点数据构成,但由于ADS4126 数据输出格式的问题,rx_out[95..0]的数据存在错位,因此需要对96bit 数据根据格式说明进行进一步的拼接组合,使其低8 位为样点1 数据,次低8 位为样点2 数据,以此类推。因此设计数据缓存单元inst28,对rx_out[95..0]的数据按照格式要求重新拼接修改,ADS4126 数据位数为12bit,考虑到为了能够兼容不同位宽的ADC,在拼接过程中通过高位补零的方式将每个样点位宽扩展为16bit。

2.2 数据存储与传输

在FPGA 中,配置双口RAM 接口,实现与ARM 之间的数据传输与交互。相比于RS232、SPI 等通信接口,双口RAM 具有数据传输速度快的优势,且双口RAM 相比于RAM,拥有两套相互独立的总线,即两端接口具有独立的数据线、地址线和控制线,从而控制器FPGA 和ARM 能够通过独立的总线同时对其进行数据的读写或访问。

系统开始工作时,ADC 样点数据经FPGA 初步接收处理后,被写到高速DDR2 存储器中。当客户端发出数据采集指令时,主控器ARM 端接收并解析相关指令,同时通过SPI 总线将指令参数下发至FPGA 端,FPGA 根据测试指令的要求从高速DDR2 存储器中读取样点数据,将数据不间断地写入双口RAM 中,并同时通过反馈信号en 告知ARM,此时,ARM 通过另一套数据地址总线从双口RAM 中读取数据,完成与FPGA 之间数据的交互。

3 系统测试

数据采集系统选用的ADC 芯片采样率为160MSa/s、位数为12bit。依照奈奎斯特采用定理,采样率必须大于被测信号感兴趣最高频率分量的2 倍,从理论上分析采样之后的数字信号才能够完整地保留原始信号中的信息。然而在实际应用中采样频率为被测信号最高频率的 5 ~10 倍,甚至数10 倍以上才能保证采样系统足以捕获信号细节[10]。因此,根据系统采样率为160MSa/s,选取被测信号的频率为5MHz,系统采样频率为被测信号频率的32 倍。

被测信号通常由任意波形发生器产生,本测试中选取Agilent公司的型号为33250A。设置输入信号频率为5MHZ,幅值为1Vpp。如图3所示,显示界面横坐标每格是0.125us,信号周期大约是1.6 格,0.125*1.6=0.2us,即信号频率测量值为5MHz。如图3所示,波形峰峰值peak to peak 为1.995Vpp,精度为(2-1.995)/2=2.5‰。

4 结束语

本系统以FPGA+ARM 的硬件结构为基础,采用高速高精度的模数转换器以及高速大容量的DDR2,设计并实现了高速高精度的数据采集器,经过实际测试,系统具有较高的采样率以及幅度精度。系统采用了LXI 总线技术,能够用于快速组建分布式自动测试系统中,在航天航空、雷达、声纳等研制、维护及故障自动诊断等领域中具有广泛的应用。