图像压缩系统设计

王 兵 白志富 张修建 印朝辉 张铁犁

(1.北京航天计量测试技术研究所,北京 100076;2.中国运载火箭技术研究院,北京 100076)

1 引 言

图像信息由于具有直观、具体、信息量大等优点,不断被引入航空、航天、无人机等飞行试验状态监控中,并成为故障分析时不可替代的信息类型[1]。但由于视频图像数据量巨大,而飞行试验遥测传输的带宽是极其有限的,因此,需要通过图像压缩器将摄像装置输出的视频图像信号进行采集、压缩编码,形成满足传输带宽要求的码率的数据码流后,再由遥测无线信道发送回地面。

由于飞行试验所用图像压缩器应用场合的特殊性,使其对图像压缩质量、压缩算法、硬件结构体积、功耗、环境适应性、可靠性等均具有较高的要求。因此需要从多方面综合考虑以达到图像压缩系统性能最优。其基本设计要求如下:

(1)图像压缩、切换要求:能对两路输入模拟视频信号按照时序要求进行切换,并对单路模拟视频信号进行采集压缩和传输处理;切换过程中图像不能错帧,切换后不能出现花屏、抖动等异常现象;

(2)图像传输处理要求:能够通过中心程序器提供的移位脉冲将压缩后的数据串行移入中心程序器,并要求按规定的恒定速率传输数据,输出数据稳定、可靠,且不错漏;

(3)图像帧频及尺寸:25帧/s;352×288,彩色视频,格式:4:2:0;

(4)算法及延时:采用自主设计的快速H.264压缩算法,压缩处理延时不大于500ms;

(5)重建图像序列平均PSNR>30dB,无明显失真现象,图像连续流畅播放;

(6)能够满足飞行试验的温度、振动、冲击及电磁兼容等环境条件要求。

本文设计了一种图像压缩系统,在适应飞行试验复杂环境的情况下,实现两路图像视频的分时切换、采集压缩和传输处理等功能。

2 图像压缩系统设计

2.1 图像压缩系统原理

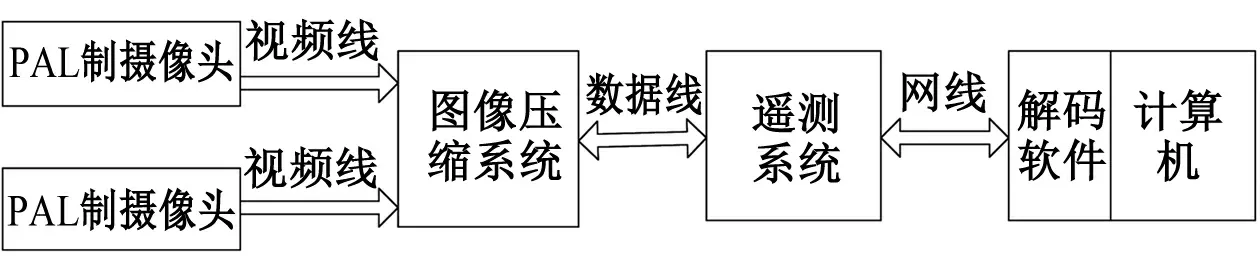

图1为现有图像遥测系统原理框图,通过在现有的遥测系统增加视频监控子系统(含摄像头与图像压缩器)获取飞行状态图像,再通过遥测系统传输至地面,在地面增加了图像实时解码设备,用于图像实时解码及显示。该图像压缩器最主要的特点是要求采用自主设计的快速H.264压缩算法,不可以采用如达芬奇系列DSP内部的H.264编码硬核来实现。这就要求采用通用的硬件架构方案来实现快速H.264压缩算法及传输编码等功能。当前许多研究者对基于FPGA+DSP架构的图像处理平台都有过很多研究[2~6],并形成成熟的案例。因此,本文采用将DSP与FPGA两种处理的结合起来优势互补架构方案,具有更强大的数据处理能力,且更灵活、更通用,同时由于DSP芯片和FPGA芯片均具有较宽的工作温度范围,能够适应复杂飞行环境。

图1 图像遥测系统原理框图Fig.1 Block diagram of image telemetry system

图像压缩系统的工作流程:从摄像头进来的两路模拟视频信号由图像压缩器的两路解码电路完成模数转换,然后输出的数字视频信号,将数字视频信号变换到要求的图像帧格式及尺寸,再经自主设计的H.264压缩编码算法模块进行压缩编码处理,形成码流后进入控制器内的图像缓冲区,再由控制器根据约定的数据帧格式对码流数据进行打包,然后根据与遥测中心程序器的控制时序将图像数据信号以恒定的速率传输给箭上遥测中心程序器,同时控制器还根据系统给出的“起始”信号及约定的切换时序完成视频切换;空中遥测系统通过无线信道将图像数据传输至地面遥测系统,然后通过挑路软件将视频信号挑出后通过以太网与地面解码设备进行连接,由解码设备进行图像重建,显示及播放,本文采用软件解码的方式。

2.2 图像压缩系统组成

图像压缩系统由图像压缩板、电源板、壳体等硬件和DSP压缩模块、FPGA控制模块等软件组成,组成框图如图2所示。

图2 图像压缩系统组成框图Fig.2 Block diagram of the image compression system

图像压缩系统的硬件电路采用模块化设计思想,整机电路由图像压缩板和电源板两个模块组成。图像压缩板主要是实现自主设计的H.264编码算法及码流传输数据帧、视频切换等控制,并最终达到遥测系统有限信道容量要求。电源板主要提供图像压缩处理系统器内部工作的各种电源和前端图像传感器工作的二次电源。图像压缩系统的结构壳体,采用上下分体式结构,通过散热设计、电磁兼容设计等实现图像压缩系统的散热处理和电磁屏蔽。

图像压缩系统的软件主要包括两部分:即DSP图像压缩模块和FPGA控制模块。DSP图像压缩模块主要在DSP中实现自主知识产权的快速H.264算法,将摄像头输出的视频压缩成H.264码流,然后输出到FPGA;FPGA模块,主要是实现图像压缩系统的各种信号的时序控制,包括“起飞”等外部输入信号的接收、两路视频的切换时序控制、输出接口的控制等,最终将压缩好的码流以PCM码格式传送到遥测系统的中心程序器。

2.3 图像压缩系统结构设计

图像压缩系统壳体由上壳体、下壳体、上盖、下盖及减震器组成,采用铝合金材料2A12,三维结构及其剖面示意图如图3所示。其中电源板安装在上壳体中,图像压缩板安装在下壳体中,上下壳体可单独装调好后进行整机装配,便于后续的测试与故障排查。在下壳体侧面加工有地线连接孔,可与箭体地相连,保持整机外壳与箭体良好导通。视频连接器通过转接板、转接板绝缘垫片与下壳体相连,转接板与下壳体连接的沉孔处安装绝缘螺钉套,实现了视频连接器壳体与图像压缩器壳体的绝缘。

在减震方面,采用4个减震器,每个减震器均可提供三个方向的减震功能,保证了图像压缩装置在震动冲击环境下的可靠性。

图3 壳体结构示意图Fig.3 Schematic diagram of the housing structure

在散热设计方面,上盖、下盖内侧加工有散热凸台,通过导热垫与电源模块及压缩模块上的电源芯片及处理芯片进行接触,将芯片散发的热量传导到上、下盖,最终传导到空气中,能够有效的提高散热效果。

在电磁兼容设计方面,所有主体结构均采用导电阳极化处理,并在喷涂时对各安装面进行保护。上壳体、下壳体安装面加工有导电橡胶安装槽,并贴有导电橡胶;各连接器与安装面间贴有导电橡胶垫,确保整机成为一个连续导电的整体。

2.4 图像压缩系统硬件设计

2.4.1 图像压缩板设计

图4为图像压缩板电路原理框图。

图4 图像压缩板电路原理框图Fig.4 Circuit block diagram of the image compression board

图像压缩板电路主要由图像压缩编码器(DSP)、控制器(FPGA)、视频解码器(Video ADC)、程序存储器(FLASH)、数据存储器(SDRAM)、复位电路(Reset)、测试端口(JTAG)等组成。

图像压缩编码器基于DSP来完成,主要完成复合视频信号的解码器的初始化和图像数据的采集及压缩。控制器主要完成时序控制、与中心程序器的通讯。控制器实时监测并接收“起始”信号,若“起始”信号有效则将时标计数器清零,之后的图像时标将按新的时标添加。FLASH用于存储DSP程序代码,SDRAM用于存储原始视频数据、DSP中间运算结果和压缩后的视频数据,JTAG用于图像压缩模块的调试与测试。

DSP主要用于完成复杂的图像压缩算法,采用TI公司生产的TMS320DM642数字信号处理器,该数字信号处理器是一款32位定点DSP芯片,是基于TI开发的第二代高性能、先进Veloci TI技术的VLIW结构,包含一个用数字表达容量的阵列处理器、一个操作灵活的高速处理器、8个独立的功能单元和64个32位字长的通用寄存器。TMS320DM642 具有3个支持多种视频标准(CCIR601,ITU-BT.656, BT.1120,SMPTE125M,260M,274M,296M)的可配置视频端口(VPO、VP1 和 VP2)。通过该端口直接与视频解码器(Video ADC)连接,以ITU-BT.656格式捕获数字视频,简化接口设计,有利于提高产品的可靠性。其工作温度范围可达(-40~+105)℃,能够满足飞行试验环境要求。

FPGA作为控制器,主要用于完成系统的图像切换控制、“起始”信号判读及数据传输时序控制等,采用Xillinx公司的Virtex2系列FPGA,具有高性能、高速度和低功耗的特点,,同时该器件为符合美军标要求的军品级器件,温度范围可达(-55~+125)℃,能够满足飞行试验环境要求。作为DSP的协处理器,负责完成图像的切换控制、数据传输等辅助功能,使得DSP可以专注于压缩算法处理。

2.4.2 图像压缩板的工作流程

(1)DSP首先检测来自控制模块的“起始” 信号,如果“起始” 信号有效,将时标计数器清零(待完成当前场图像编码后,在视频数据中插入新的时标信息);其次进行“切换”信号检测,若“切换”信号无效,不进行视频切换,则直接从SDRAM缓冲区中读取当前摄像装置的图像数据,若“切换”信号有效,进行视频切换,则切换至SDRAM的另一缓冲区读取另一个摄像装置的图像数据;然后,DSP进行当前帧图像数据编码并将编码结果写入数据存储器(SDRAM);此时在DSP中启动另一线程,通过EMIF接口将视频码流的写入FPGA程序中的FIFO中;FPGA根据遥测系统中心程序器发过来的同步移位脉冲信号及帧同步信号将数据串行化后以恒定的速率通过高速光耦发送给中心程序器。

(2)图像压缩板与中心程序器通过高速光耦进行数据通信,图像压缩器中的FPGA通过光耦接收中心程序器的发过来的帧同步信号和移位脉冲信号之后,按照图5所示的接口时序,构建状态机,按时序要求再通过高速光耦向中心程序器送出数码脉冲。移位脉冲的频率为1MHz,FPGA接收到帧同步信号后,等待12us,根据移位脉冲的上升沿,将一个字节的8位数据并串转换后发出,先发低位再发高位,中心程序器在移位脉冲的下降沿取数据。

图5 接口时序Fig.5 Interface timing

2.4.3 电源板设计

如图6所示,电源板在图像压缩处理模块在设计中采用15W功率的隔离DC-DC对系遥测电池+28V转换到+5V,再经过LDO将+5V转换到+3.3V、+1.8V、+1.5V、+1.4V等多种电源,经过DC-DC升压芯片将+5V电源升至+12V,经LC滤波网络滤波隔离后给两路摄像图像压缩板供电。

图像压缩系统的电源板是图像压缩器系统的一个重要组成部分,电源系统的好坏关系着能否输出高质量的图像压缩数据,必须进行电源转换方可满足摄像装置的工作电压要求。为了提高工作可靠性及稳定性,确保装置的工作安全及成像质量,供电系统采取了以下措施:电源输入端加入大功率限流电阻,对装置供电进行过流保护;电源输入端加入双向瞬态电压抑制二极管(TVS),对装置供电进行浪涌和过压保护;电源输入端串入整流二极管,防止电源反接损坏图像压缩系统;输入电压经过直流滤波器滤波后使用,减小系统和装置间的互扰;使用隔离型DC-DC电源模块将源转换到5V,其可承受40V、1min的瞬时过压冲击;对于DSP、FPGA及外围器件供电的3.3V、1.8V、1.5V和1.4V电源采用LDO电源芯片进行二次变换,提高效率,减少电源芯片发热量;对于给摄像装置供电的12V电源,通过DC/DC升压芯片将5V电源升到12V,并采用LC滤波网络抑制摄像装置与图像压缩系统电源之间的电磁干扰。

在电源板电路设计中采用了接地、屏蔽、滤波等抗干扰方法,对辐射型及传导型干扰均具有优良的抑制性能。具体在PCB设计时还应注意增加磁珠、去藕电容合理配置、PCB板走线、数字和模拟分开等方面,使装置的电磁兼容性达到飞行试验要求。

图6 电源板电路原理框图Fig.6 Circuit block diagram of the power board

2.5 图像压缩系统软件设计

图像压缩系统软件由DSP图像压缩模块和FPGA控制模块两个组成部分。

2.5.1 DSP图像压缩模块工作流程

(1)接收到FPGA程序发过来的复位信号后DSP复位;

(2)DSP从FLASH读取程序;

(3)DSP初始化、完成对复合视频解码器设置(图像格式等);

(4)通过VP0A和VP1A端口以BT.656视频流格式捕获摄像装置1、2的图像,并将其每40ms通过EDMA通道写入“缓冲区1”;

(5)启动“编码线程”;

(6)等待“采集完成中断”,若采集完成中断有效,则继续进行“起始”信号检测;

(7)DSP检测“起始”信号(来自控制模块),如果“起始”信号有效,DSP将时标计数器清零;

(8)DSP检测“切换”信号(来自控制模块),如果“切换”信号无效,DSP从“缓冲区1”读取摄像装置1的1帧图像数据;如果“切换”信号有效,DSP从“缓冲区1”读取摄像装置2的1帧图像数据;

(9)完成当前场图像编码,并插入时标信息;

(10)将压缩后的数据写入“缓冲区2”;

(11)返回到等待“采集完成中断”状态,同时启动数据传输线程;

(12)启动数据传输线程后,DSP检测“FIFO_FULL”信号(来自控制模块)。如果“FIFO_FULL”信号无效,从“缓冲区2”读取数据并将数据输出给控制模块中FIFO,直至一帧数据传输完毕;若“FIFO_FULL”信号有效,则等待直至“FIFO_FULL”信号无效,再开始传输数据;

(13)挂起数据传输线程,直到下一帧数据压缩编码完成后再次启动。

2.5.2 FPGA控制模块工作流程

(1)上电后FPGA从PROM中读取程序;

(2)FPGA复位;

(3)FPGA复位后,传输复位信号给DSP和其他器件,使其完成逐一复位;

(4)控制模块同时监测“起始”和“请求脉冲”,并运行视频“切换”控制逻辑,具体工作模式如下:如果控制模块收到“起始”信号,首先判断“起始”信号的有效性,若“起始”有效,向DSP发“起始”信号 (电平为高);否则“起始”信号为低电平;FPGA在接收“取数脉冲”的同时,判断“取数脉冲”的有效性,若“取数脉冲”有效,则继续判断“FIFO_EMPTY”是否有效,若FIFO空,则发送4个字节的无效数据,若FIFO非空,则从FIFO读取数据根据时序由422连续发送512字节的图像数据,等待测量系统“取数脉冲”读数;视频切换时序;起始至停,分为两个时间段,实时测量视频2图像画面,此时向DSP发“切换”信号(电平为高);否则“切换”信号无效,为低电平。

3 试验验证

图像压缩系统样机研制成功后对其进行了各类试验,以验证其对任务需求的满足情况,因此搭建了了试验测试系统,如图7所示。试验测试系统由两台PAL制模拟摄像头、图像压缩系统、测试台、测试电源、测试线缆、测试计算机、以及解码软件等组成。两台摄像头作为图像压缩系统的视频输入,通过视频线与图像压缩系统连接;测试台用于模拟遥测系统的部分功能,即向箭上图像压缩系统发送帧同步及移位脉冲信号,接收箭上图像压缩系统发送的数据脉冲,并转换成字节,每512个字节打包,通过以太网口发送给计算机;计算机从以太网接收到数据后由解码软件进行解码、存储及显示播放等;测试电源为摄像头、图像压缩系统及测试台提供所需的电源。

图7 图像压缩试验测试系统示意图Fig.7 Schematic diagram of the image compression test system

首先对图像压缩系统的各项功能及性能指标进行测试,重点测试了样机的图像切换、压缩功能、图像传输功能、时标、接口、图像尺寸及帧频、处理延时、图像质量以及功耗等。摄像头视频经过箭上图像压缩系统压缩后传输到计算机由解码软件进行解码播放,可以观察到视频播放清晰流程,无明显失真现象,重构后的图像质量较好,如图8所示。功能及性能试验结果如下:基于FPGA+DSP的图像压缩系统能够实现两路输入模拟视频信号按照时序要求进行切换,并对单路模拟视频信号进行采集压缩,并以恒定512kbps速率进行传输处理;切换过程中图像无错帧、花屏、抖动等异常现象;能够以CIF尺寸、25帧/s在地面解码软件中进行实时解码播放显示,重建图像序列平均PSNR始终大于30dB,图像清晰流畅;图像压缩处理总延时经测试优于设计指标,一般情况下保持在200ms以内;功耗为0.26A;图像压缩系统的功能及性能指标满足了设计任务要求。

图8 地面解码重构后的图像Fig.8 Ground decoded reconstructed image

本文设计的图像压缩系统主要是用于飞行试验,其环境适应性试验考核非常重要。为了验证图像压缩系统的环境适应性,对图像压缩系统样机进行了环境试验考核,试验项目、条件及结果如表1所示。试验结果表明,图像压缩系统的环境适应性达到了设计要求,能够满足飞行试验要求。

表1 图像压缩系统环境适应性试验

4 结束语

本文设计的基于FPGA+DSP的图像实时压缩系统,针对飞行试验对系统环境适应性、功耗等要求,从系统硬件电路、软件、结构等方面进行了优化设计,充分发挥了FPGA并行处理及DSP算法处理能力强的特点,提高了系统的灵活性及环境适应性。该系统能够实现在飞行试验环境条件下多路视频的采集、压缩、传输、按时序切换等功能,具有处理延时小、功耗低、环境适应性好、适应数据量大算法复杂的应用场合等特点,并已经得到了试验验证,能够满足飞行试验要求,具有较高的工程应用价值。

该系统硬件平台架构通用,DSP及FPGA程序软件均可扩展,图像压缩率可软件设置,是一个较为通用的图像处理平台,能够根据不同的应用场合进行调整,具有广泛的适应性和推广应用价值。