基于Qsys的时栅信号处理系统设计与实现*

陈自然,赵有祥,田 伟,赵 建,王露露,卜 敬

(重庆理工大学机械检测技术与装备教育部工程研究中心,时栅传感及先进检测技术重庆市重点实验室,重庆 400054)

随着我国由制造大国向制造强国的战略转变,传统制造工业向自动化、智能化发展已成为必然趋势[1]。精密测量作为智能制造的基石,其测量水平的高低将影响制造品质的优劣,故工业自动化生产将对高精度位移传感器的需求越加显著[2-3]。时栅作为一种新型的智能位移传感器,采用时空测量基准转换,将空间位移测量转换为时间差测量,用时间尺度来提高空间尺度测量的分辨力和精度[4-5]。目前时栅传感器分为磁场式、电场式和光场式三种。虽然时栅降低了对机械精密刻线的工艺要求[6],但想进一步提高测量精度,则高精度的时间基准与时间测量方法便显得十分重要。传统时栅信号处理系统采用测量信号频率为1 kHz,采样周期为1ms,原信号处理电路采用频率为80 MHz的时钟脉冲插补,利用上升沿触发计数[7],运用高频时钟插补技术对感应信号与同频参考信号的相位差和周期进行脉冲计数来计算时间间隔,并利用SOPC系统设计软核进行数据处理[8]。

Qsys系统集成工具采用对FPGA优化的芯片网络技术,提供存储器映射和数据通路互联,并使用标准接口。同时与SOPC系统互联架构相比,基于NoC体系结构的Qsys互联能更好提高系统性能[9]。综上,本文设计了一种基于Qsys技术的时栅信号处理系统,利用FPGA嵌入式锁相环倍频产生4路相位依次相差45°、频率均为250 MHz的脉冲信号作为时间测量基准,采用多路并行双边沿计数方法对被测信号进行计数测量,可以实现相当于2 GHz高频时钟脉冲计数的分辨力,利用Qsys系统集成工具设计Nios-II软核进行数据处理,采用傅立叶级数谐波修正技术[10-11]对测量结果进行实时修正,进一步提高时栅信号处理系统的测量精度及动态性能。

1 系统设计原理

1.1 时栅信号处理流程

磁场式时栅传感单元由定子和转子组成,定子上绕两相激励绕组和一相感应绕组[12],行波信号如式(1)所示。

(1)

式中:U1和U2为激励绕组的两路时间正交正弦激励信号,U1′和U2′为感应绕组上根据电磁感应原理获得的两路驻波信号。

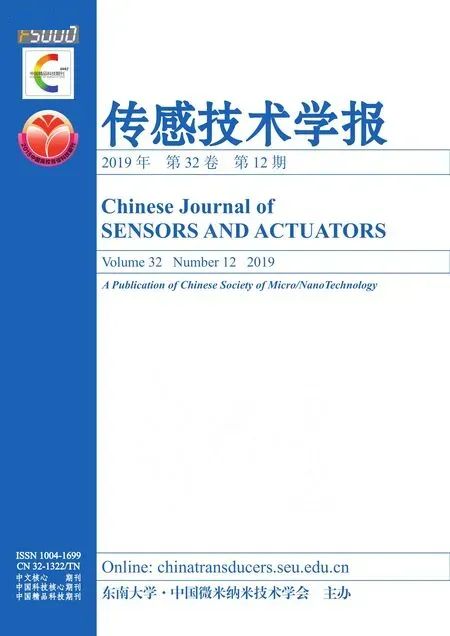

时栅信号处理系统如图1所示。U1=Um×sin(2πt/T),U2=Umcos(2πt/T)。Um为激励信号的幅值,T为激励信号的周期。Km为磁场耦合系数,W为定子极距,φ为转子转动位移量。

图1 时栅信号处理系统

由式(1)可知,当转子相对于定子转动一个极距W,则感应信号Uo的相位变化2π。将同频正弦激励信号Us作为参考信号(下文中参考信号均用Ur表示),并同时将感应信号与参考信号整形为方波信号输入FPGA。通过比较Uo、Ur相位得到含有位移信息的相位时间差ΔT,利用高频时钟脉冲对其进行计数测量,得到转子转动的空间位移量θ,其θ可表示为:

(2)

式中:ΔT为比相后的时间间隔,T为参考信号周期,n为转子相对于定子走过的完整极距数,Tclk为高频脉冲周期,ΔN为时间ΔT内的计数脉冲个数,N为T时间内的脉冲个数。根据式(2)可知,每个时钟脉冲的空间当量,即空间分辨力可表示为:

(3)

由式(3)可知,提高时钟脉冲的频率,则可在一个信号周期内增加脉冲个数,提高空间分辨力与测量精度。

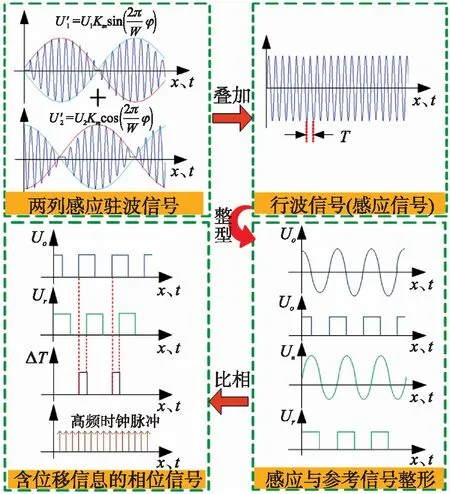

图2 多路并行双边沿计数原理

1.2 多路并行双边沿计数原理

由上文可知,ΔT和T的测量是采用脉冲计数法[13],然后通过相位转换得到测量结果。而脉冲计数法会存在量化误差,即±1误差。为了减小量化误差,本文采用“多路并行双边沿计数法”,其原理如图2所示。

clk1~clk4为4路频率均为fclk(即周期均为Tclk)、相位依次相差45°的高频时钟脉冲,将其均作为测量基准,用于测量信号Tx的高电平时间。当信号Tx为高电平时,clk1~clk4各自的计数器启动。当各路时钟脉冲的上升沿或下降沿来临时,各自的计数器便将计数值累加1。即在一个时钟周期Tclk内,实现了对Tx的8次计数,等效于频率为8倍fclk的时钟脉冲上升沿计数效果。当Tx为低电平后,clk1~clk4各自的计数器关闭,均停止计数。该方法在不提升时钟脉冲频率的情况下,能够提高时钟脉冲对被测信号的分辨力,而且十分简便。

由于在计数期间,Tx的上升沿和下降沿与clk1~clk4的双边沿没有保持同步而存在误差e1和e2,则量化误差e与时钟脉冲周期Tclk关系可表示为:

(4)

由式(4)可见,当钟脉冲周期Tclk越小时,即clk1~clk4的频率越高时,量化误差e会越小。随着超大规模集成电路的集成度和工艺水平不断提高,许多FPGA芯片均可稳定工作在250 MHz的时钟频率。为提高系统的可靠性,利用FPGA内部的嵌入式锁相环模块对50 MHz晶振频率进行倍频产生4路频率为250 MHz、相位依次相差45°的时钟脉冲作为clk1~clk4,采用多路并行双边沿计数方法可以实现相当于2 GHz时钟脉冲的分辨力,且量化误差最大为0.5 ns。

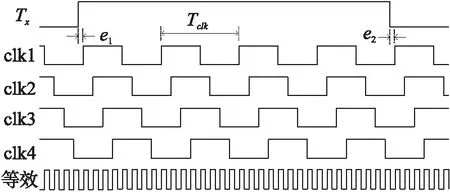

图3 信号处理系统结构框图

2 系统设计

信号处理系统主要由前置信号处理电路和FPGA数据采集与通信两部分组成,系统结构框图如图3所示。传感器输出的感应信号经过仪表放大电路、带通滤波电路进行预处理;再经过零比较电路整形为可兼容FPGA接口电平的方波信号,以便FPGA处理器采集。利用Qsys系统集成工具设计Nios-II软核,以外部中断的方式采集感应信号的相位差计数值和周期计数值。再将测量结果实时修正得到精确的位移量,通过串口通信将结果传输到上位机进行显示与数据存储。

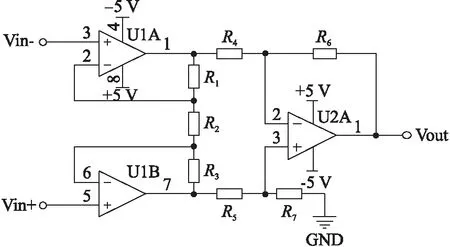

2.1 仪表放大电路

传统磁场式圆时栅输出的感应信号幅值大小为60 mV左右,并会伴随一定的共模电压。考虑到电路需具有良好的共模抑制能力,高输入阻抗,足够大的增益等特点,采用三运放构成的高共模抑制比仪表放大电路,其电路如图4所示。系统采用±5 V电源供电,选用放大器芯片INA141可以减小电路体积,提高电路可靠性。

图4 仪表放大电路

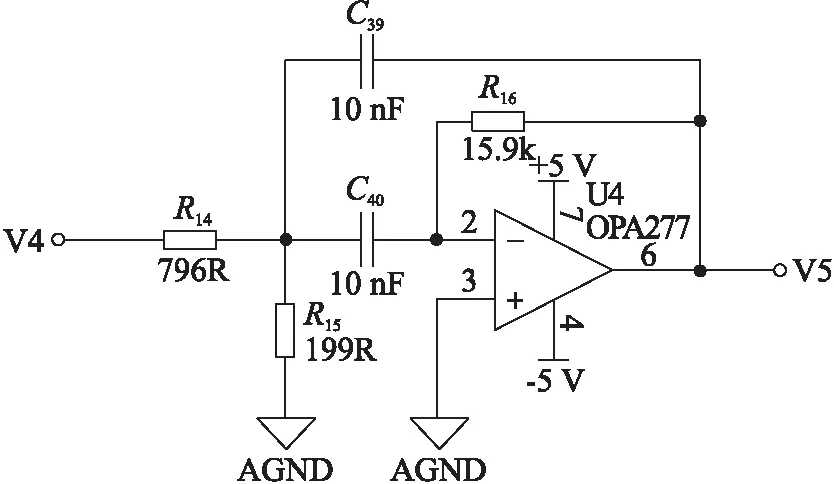

2.2 带通滤波电路

为滤除时栅传感器原始信号中的高频干扰、工频干扰、电路噪声等,以频率为10 kHz的激励信号为例,设计了一种中心频率为10 kHz,带宽为2 kHz,增益为10 dB的带通滤波器,其电路如图5所示。

图5 带通滤波电路

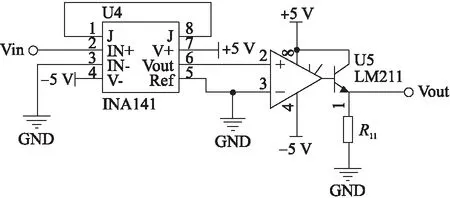

2.3 过零比较电路

采用LM211集成芯片构成的过零比较电路具有信号方波整形与电平兼容功能。为使整形后得到的方波信号的上升时间和衰减时间尽量小,需在过零比较电路前再增加一个高增益放大电路,以提高测量精度。正弦型的感应信号和参考信号经过该高增益放大电路后,正弦信号此时会因增益过大而导致波形幅值失真成为方波,再进入LM211过零比较器转换为低电平为0 V,高电平为3.3 V的方波。高增益放大电路采用仪表放大电路中提及到的集成芯片INA141构建。

整个电路如图6所示。

图6 过零比较电路

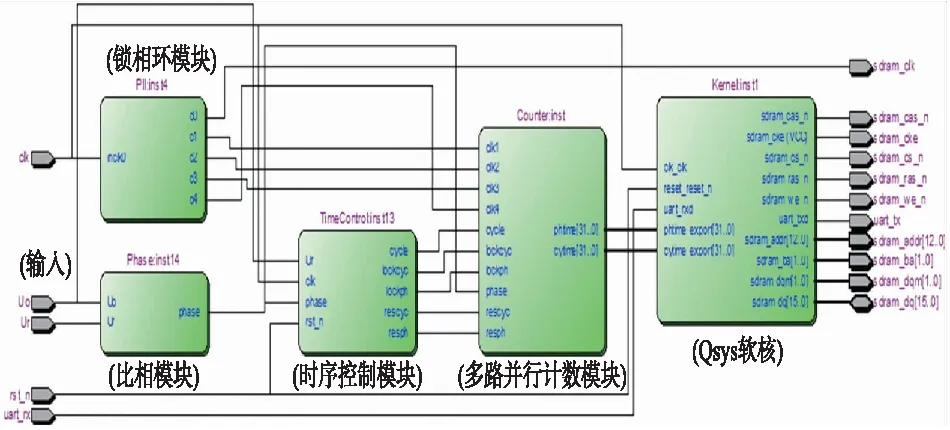

2.4 FPGA模块设计

利用Quartus-II软件开发、设计信号比相、时序控制、多路并行计数等模块,以及基于Qsys软核的系统搭建,其整个工程的顶层程序RTL视图如图7所示。

图7 顶层结构RTL视图

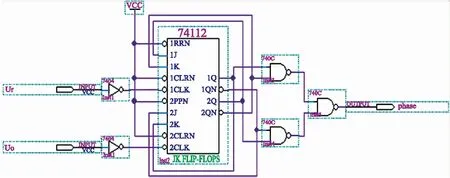

比相模块采用JK触发器、非门及与非门搭建,作用为将感应信号与参考信号的相位差转换成高电平持续时间,具体电路图如图8所示,Ur为参考信号输入端,Uo为感应信号输入端,phase为相位差输出信号。该模块可以实现0~2π的相位检测,即可测量出时栅传感器测头在每一个极距W里的位置信息。便于FPGA采集周期信息,在时序控制模块内将参考信号Ur进行二分频整形作为周期信号cycle,从而将周期信息转换成为周期信号的高电平持续时间。

图8 比相模块

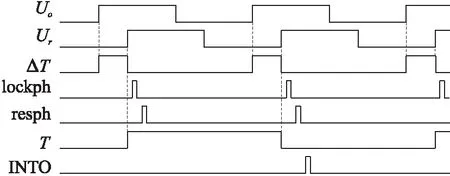

为了更加精确地获取相位差信号与周期信号的计数值,根据多路并行双边沿计数原理设计了多路并行计数模块,利用FPGA内部锁相环IP核模块产生四路频率为250 MHz、相位依次相差45°的时钟脉冲作为时钟信号输入。对相位差和周期信号的测量分别采用8个18位的计数器进行计数。当相位差信号处于高电平期间,各计数器随着相应时钟沿的到来进行计数,高电平结束后,各计数器立即停止计数;并同时利用移位寄存器的原理对相位差信号进行延时处理,依次产生相位差计数的锁存信号lockph、清零信号resph,整个逻辑控制时序如图9所示。当相位差各个计数器停止计数后,等锁存信号lockph到来时,将各计数值相加并放在总线上待软核Kernel读取;利用移位寄存器原理将参考信号Ur的上升沿进行延时,产生一个外部中断信号INTO用于触发软核Kernel读取总线上的数据。

图9 逻辑控制时序图

图10 程序流程图

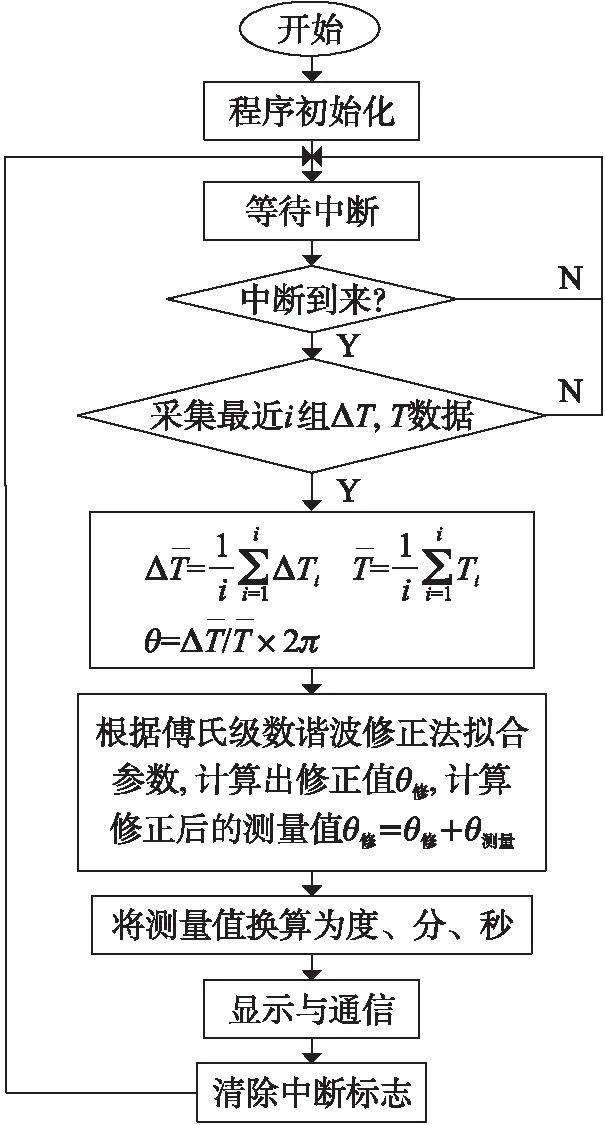

3 软件设计

通过Nios-II Eclipse开发环境对软核Kernel进行设计,软核Kernel主要功能为相位差与周期计数的采集、测量结果计算与误差修正以及与上位机通信,其主程序流程图如图10所示。待外部中断信号到来,软核开始采集相位差和周期的计数值,达到最近i组数据后,利用平均原理先消除随机性干扰;再根据傅立叶级数谐波修正法对测量结果进行实时修正;最后将结果通过串口通信传输到上位机显示与存储,同时清除软核中断标志位,为下次数据采集做准备。

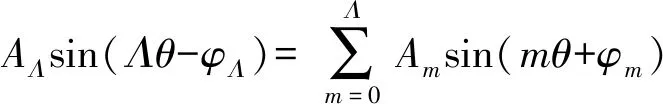

根据圆周封闭原则[14],时栅传感器采用多对极结构可以有效消除绝大部分误差。采用k对极的时栅传感器就能消除整周上除mk(m=1,2,3,…,Λ)次以外的各项周期性误差。利用傅立叶级数谐波修正方法将时栅传感器的整周误差转换为在测量范围内对应的0,1,2,3,4…次谐波误差之和,误差可以表示如式(5):

(5)

通过采样点得到空间离散误差序列X(θ)将其经过离散傅立叶变换得到X(ejw)进而展开可以得到:

X(ejw)=XR(ejw)+jXI(ejw)

(6)

由式(6)即可求得式(5)中各谐波幅值A(m)和相位φ(m),其可分别表示为:

(7)

(8)

将得到的原始误差曲线利用MATLAB进行快速傅立叶变换,可得到各谐波分量的幅值A(m)和相位φ(m),将各谐波分量的幅值和相位代入式(5),可对误差进行修正。

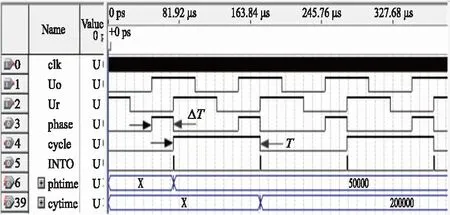

图11 多路并行双边沿计数仿真结果

4 实验验证

4.1 软件仿真

利用Quartus II软件仿真验证所设计的多路并行双边沿计数结果是否正确以及各控制信号时序是否满足要求。设置输入时钟clk为50 MHz,经过嵌入式锁相环模块倍频产生4路频率均为250 MHz、相位依次相差45°的时钟脉冲作为测量基准。同时,设置产生两路频率为10 kHz、相位差90°的方波信号来模拟时栅传感器一个极距里的感应信号U0与参考信号Ur。由于信号周期为100 μs,设置仿真时间为400 μs即可,计数仿真结果如图11所示。phase、cycle分别为相位差信号和周期信号;INTO为外部中断信号;phtime和cytime分别为相位差计数、周期计数输出端口。由于2 GHz的时钟脉冲周期为0.5 ns,对于周期为100 μs的信号,其理论周期计数值为100 μs/0.5 ns=200 000。相位差为90°的时间间隔等同为一个周期的1/4,其理论计数值为50 000。

由图11可知,相位差计数为50 000,周期计数为200 000,计数结果准确。由于仿真时两路信号的相位差固定,所以相位差总线上数值不变。而在实际测量中,感应信号的相位随位移的变化而变化,故其计数值也将变化。同时,当72对极时栅角位移传感器转过一个对极时,转子转动的空间角度为5°,则其计量脉冲数为200 000,则每个脉冲对应的空间当量为0.09″,故采用时间测量空间的方式具有较高分辨力的优势。

4.2 实验分析

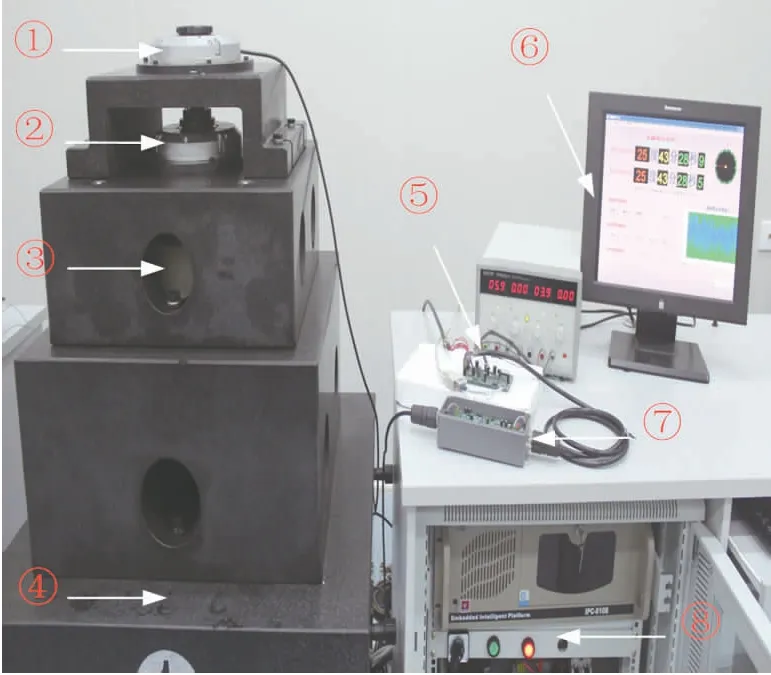

为验证该系统的性能,搭建物理实验平台进行测试,图12为搭建的时栅角位移传感器实验平台。将72对极时栅角位移传感器、HEIDENHAIN圆光栅ROD880(精度为1″)及一个带直驱电机的数控转台利用高弹性联轴器在大理石平台上同轴安装。以可编程多轴控制器作为控制核心,采用Kollmorgen直驱电机以10 °/s的速度带动连轴器驱动转台使时栅角位移传感器与光栅同步运动。

①-时栅角位移传感器;②-光栅;③-数控转台;④-大理石平台;⑤-电源;⑥-上位机;⑦-信号处理系统;⑧-PMAC图12 时栅角位移传感器实验平台

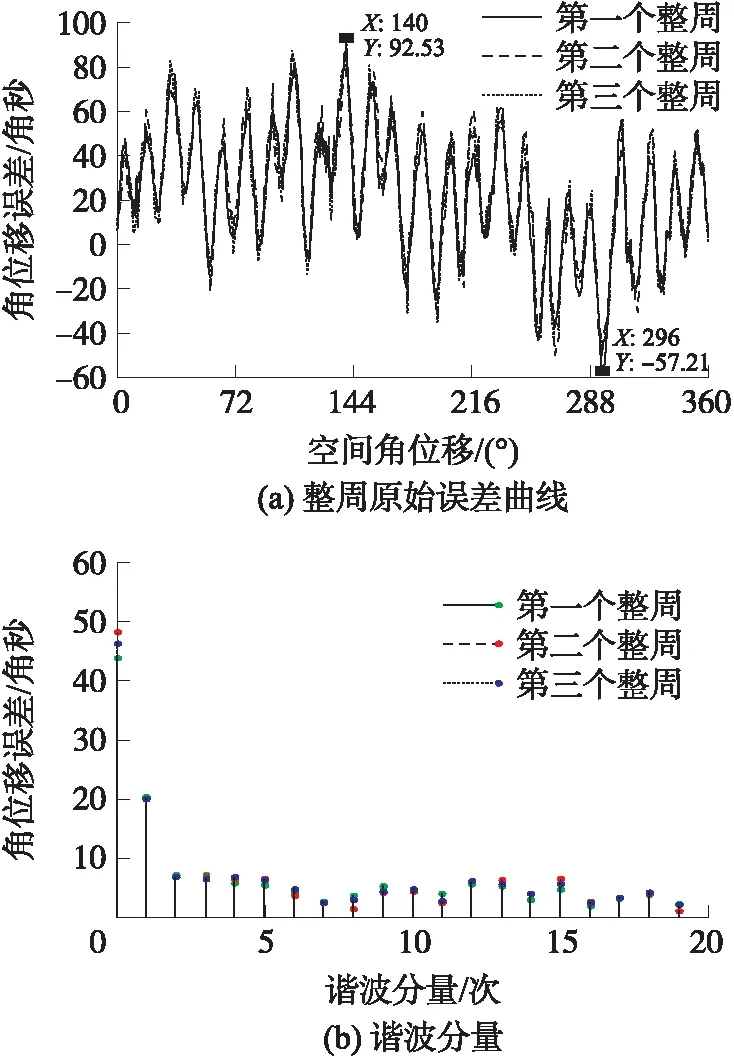

利用本次所设计的信号处理系统对时栅信号数据进行采集,并同时采集光栅值。将光栅输出值作为标准值,时栅输出值作为测量值。将它们的差值作为时栅传感器的误差值,通过上位机计算出时栅误差值并实时绘制误差曲线。测量获得的三个整周原始误差曲线与谐波成分如图13所示,误差范围约为-57.2″~92.5″。

图13 整周原始误差曲线与谐波分量

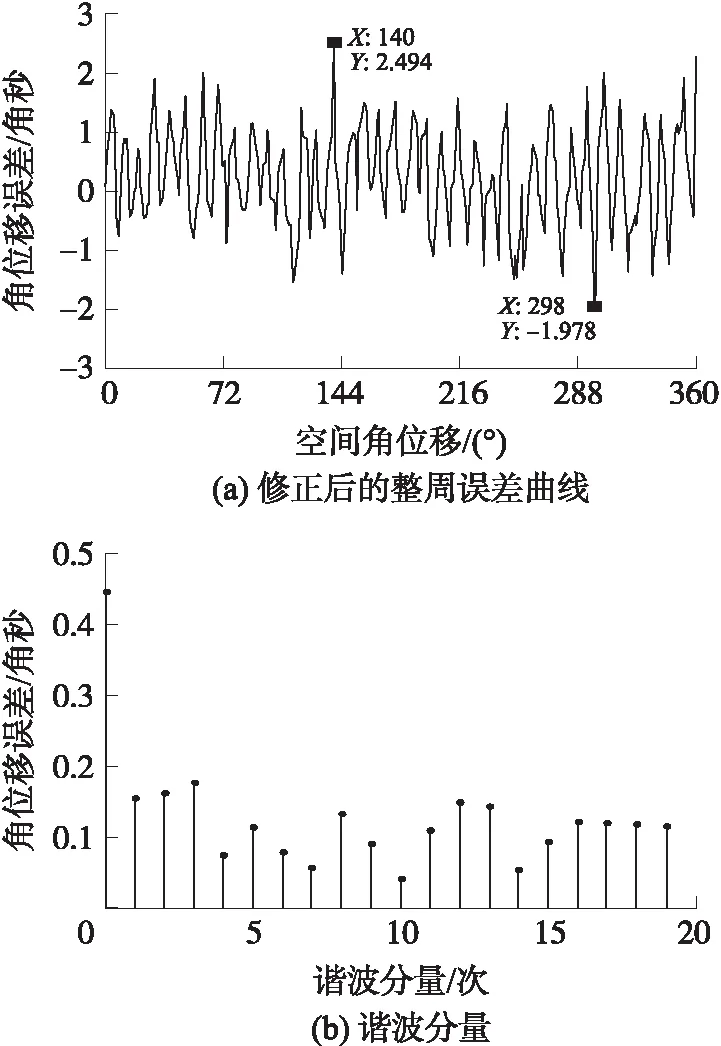

通过傅里叶谐修正法对原始误差曲线进行拟合,得到补偿曲线。将得到的补偿曲线存储在SDRAM数据存储器里,以便测量系统对进行测量结果进行实时修正。再次测量获得修正后的整周测量误差曲线与谐波成分如图14所示,误差范围约为-2.0″~2.5″,各谐波分量幅值也迅速下降,测量精度得到提高。

图14 修正后的整周误差曲线与谐波成分

5 结论

通过对测量结果分析,传感器存在因两相激励信号时间不正交和两列驻波信号空间非正交、幅值不相等的因素产生的测量误差,它们主要导致零次谐波误差和二次谐波误差;绕组的不一致性、存在杂散电容、铁芯材质不均匀等引起的零点残余电压影响导致了一次谐波误差。

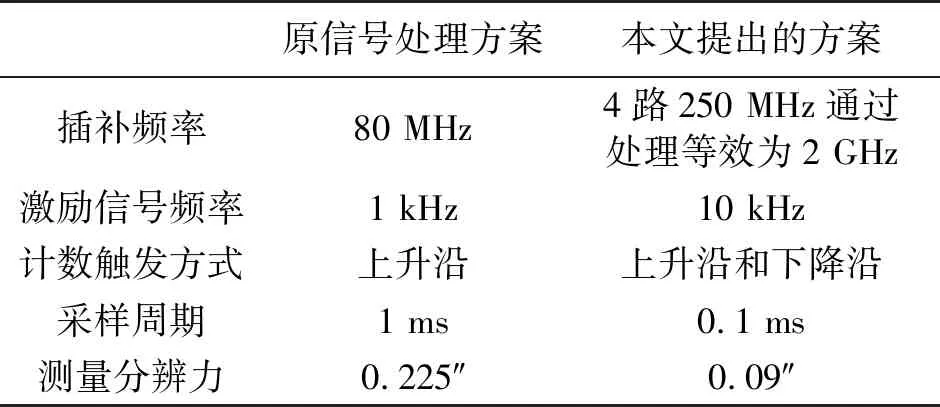

对比原72对极时栅,测量信号频率为1 kHz,采样周期为1 ms,原信号处理电路采用频率为80 MHz的时钟脉冲插补,利用上升沿触发计数,得到测量分辨力为0.225″。而本文将原激励信号频率由1 kHz提高到10 kHz,采样周期缩短到0.1 ms。并且本文提出的基于Qsys的时栅信号处理系统在电路上采用上升沿和下降沿同时触发计数,将4路相差45°的频率为250 MHz的时钟脉冲等效合并为2 GHz频率的插补时钟脉冲,得到的测量分辨力为0.09″。表1对改善前后时栅测量信号处理方案到分辨力参数做了系统对比,从理论上分析基于Qsys的时栅信号处理系统能有效地提高时栅传感器测量分辨力。

表1 改善前后传感器测量分辨力对比

针对时栅位移传感器对测量精度、动态性能、可靠性等提出的高要求,本文设计了一种基于Qsys的时栅信号处理系统,采用集成电路芯片的方式简化电路设计,运用多路并行双边沿计数方法进一步提高时钟基准的分辨力,使用Qsys系统工具设计的软核能更快速的进行数据处理,利用傅立叶谐波修正技术实现对测量结果的实时修正。实验结果表明:经过误差修正后,该系统测量的整周误差从原始-57.2″~92.5″下降到-2.0″~2.5″,提高了时栅传感器的测量精度。基于Qsys的信号处理系统具有设计快速、结构简单、可移植性强等优点,具有一定的工程应用价值。