基于DSP的编码性能优化比较分析

魏国庆,冉明昊,梅 伶

(1.重庆金美通信有限责任公司,重庆400030;2.重庆能源工业技师学院信息中心,重庆400037)

1 引 言

随着行业重心向速度高、延迟低、以数据为中心的移动网络的迁移,OEM 厂商需要在降低成本的前提下,提供更高吞吐量的DSP,以满足日益复杂的基站设计要求。飞思卡尔半导体公司的DSP 凭借其具有的MAPLE-B 基带加速器的优势,在灵活性、功耗、性能等方面都具有一定的产品吸引力,有助于大幅度提高有线和无线基础设施系统中媒体网关、基站以及代码转换应用等的系统密度,同时也有利于设备制造商解决下一代无线标准实现的问题[1-2]。以Freescale MS8156 DSP 为例,对其结构和系统的性能深入分析并加以对比,研究信道编译码的实现方式,包括硬件平台、编译码方式、DSP 实现与数据分析等,以实现对编码性能的优化。

2 平台描述

信道编译码是通信过程中的重要技术之一,其功能实现是由飞思卡尔半导体公司提供的MSC8156系列多核DSP 完成的。该产品基于StarCore 技术和SC3850 内核,是针对第四代移动通信市场推出的高性能高集成的多核DSP 处理器,包含一个具有可编程系统接口的硬件加速器MAPLE-B,其上集成了Turbo 编码器、译码器、CRC 等处理单元。

Turbo 译码器支持3GPP TS 36.212 标准的Turbo 译码及IEEE 802.16-2004TM 标准的WiMAX OFDMA Turbo 译码;支持最大译码长度为4800 比特(WiMAX)[3-4]。

编译开发环境采用飞思卡尔半导体公司提供的CodeWafrior Dvelopment Studio 集成开发环境平台。该环境可以支持对SC3400、SC3850 等多款DSP 芯片的单核仿真支持,主要用于物理层算法的仿真与调试[5]。

3 信道编码

根据信道编码定理,对于任何一个通信信道都存在一定的信道容量C,即为信道的最大极限传输能力,当实际信道传输速率R<C 时,就可以用差错控制码为这个信道设计一个系统使得输出错误概率为任意小。1993 年在瑞士召开的国际通信会议上,两位法国教授首次提出一种Turbo 码编码方案,由于它很好地利用了信道编码理论中的随机性,获得了接近香农极限的编译码性能[6-7]。

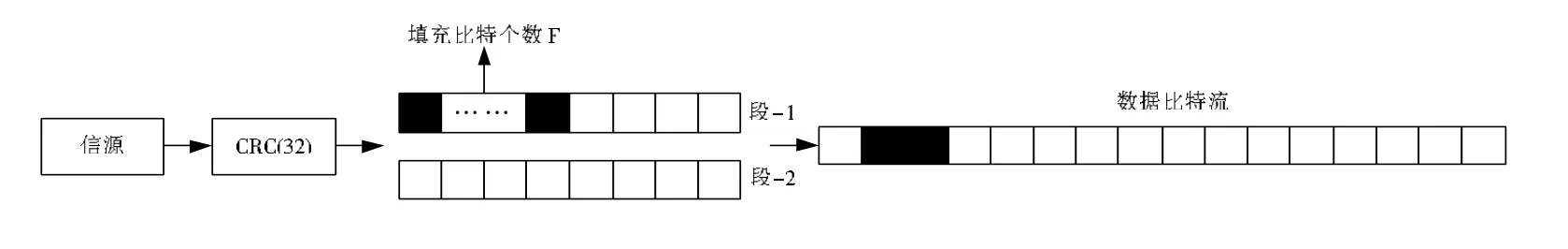

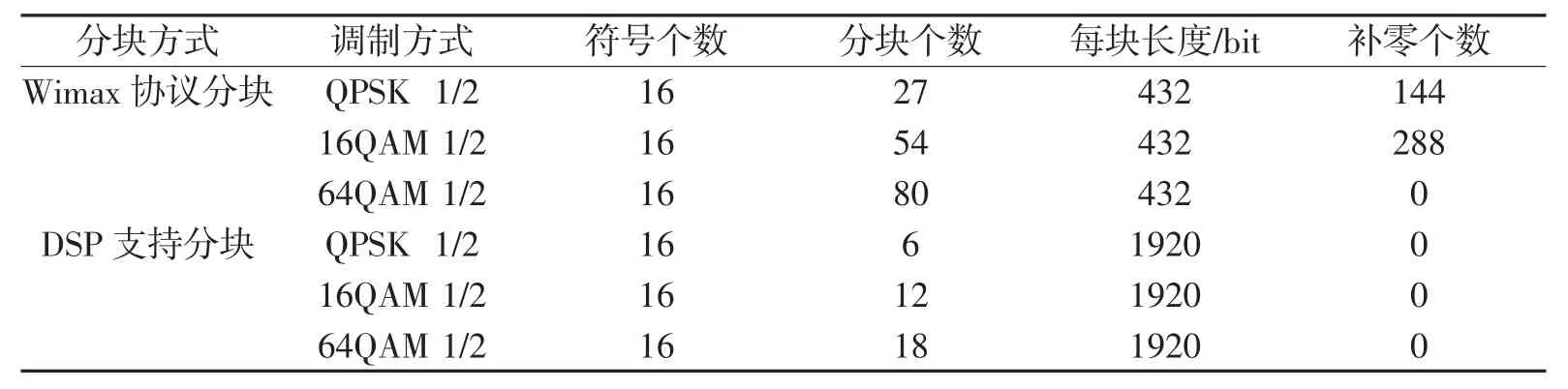

Turbo 码主要由分量码和交织器组成。分量码和交织器对Turbo 码的性能起到决定性的作用,故此研究偏重于分析分量码和交织器的长度选择对系统性能所产生的影响。以WiMAX 协议为例,其Turbo 译码器支持最大译码长度为4800 比特,根据工程实现方案复杂度,可通过不同译码长度来分析、优化系统性能。如图1 所示为编码码块数目为2 时的比特数据流形成过程,具体为:根据数据带宽计算所需信源数据长度;信源经过32 位的CRC 编码之后,进入Turbo 编码器,分2 段进行比特流编码,再组成数据流,进行数据符号调制映射处理。在OFDM复帧信号中,不同调制方式下编码码块数目的差异对比如表1 所示。

图1 编码块数为2 时数据流的形成

表1 单帧信号分块数目比较

从表1 可见,在相同的数据帧长度下,QPSK 调制所传输的数据少,编码数据分块数目少,DSP 资源消耗少;64QAM 传输的数据多,导致64QAM 的分段数目变多,DSP 的资源消耗变大。通过DSP 中Turbo译码器的灵活配置,可以设置编码长度,减少硬件加速器的资源消耗。

4 DSP 的实现

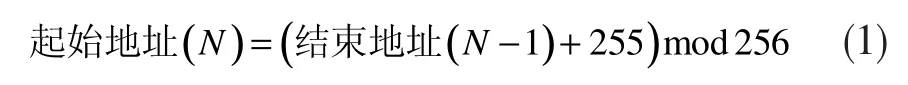

在MSC8156 DSP 系统的地址空间中,Maple 硬件加速器所用的地址为0xC1000000~0xC13FFFFF,共4M 字节,在这段内存中包含系统参数、BD 环配置、加速模块等,也包含编译码硬件加速器的内存空间。Maple 通过管理配置,将使用的单元块在一块共享的内存中统一分配,提高了加速器的灵活性和资料利用效率。BD 环由16k 字节参数配置地址空间,主要有起始地址、结束地址、任务个数、任务长度等。每个使用的加速模块在初始化时,会根据配置使用情况,决定在16k 地址空间中的资源分配。资源分配规则按照初始化顺序,依次分配,具体规则如下[8]:

其中,N 为第N 个初始化的加速模块,N 为0 时起始地址为0xC1004000,按照256 字节对齐的方式进行内存资源分配。

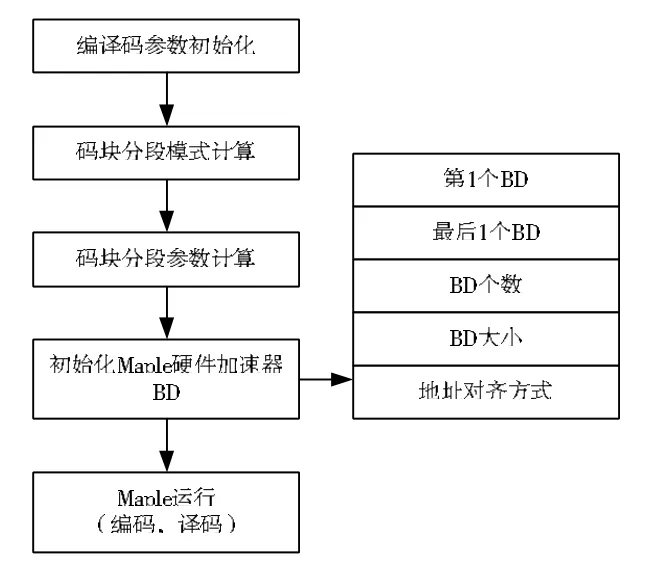

其中,任务个数为加速器初始化时决定,任务长度由每个加速模块决定,每个加速模块都有不同的任务长度。系统编码、译码前DSP 的参数初始化过程如图2 所示。

图2 DSP 参数初始化过程

5 系统性能比较

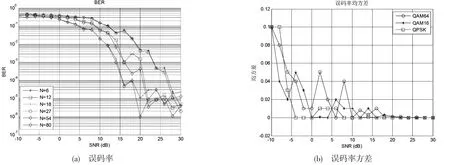

为对比编译码时不同码块分段方式的DSP 实现结果,将仿真方式及参数设置为:单发单收的系统,采样率为11.2 MHz,OFDM 有效子载波数为840,FFT 点数为1 024 点,CP 长度为128 点,帧长为2.5 ms,符号个数为24。不同码块分段方式的误码率仿真结果如图3。

由图3 不同码块分块方式下误码率情况比较可见:在相同的调制方式下,如QPSK 1/2 的码块分块数目多;WiMAX 协议分块方式在译码性能上优于DSP 支持分块方式。占据DSP 系统资源较多,则执行效率较低;分块数目少,则译码性能低,占据DSP系统资源较少,执行效率较高。低信噪比时,WiMAX协议分块方式和DSP 支持分块方式的译码性能对比结果波动较大,这与分块的数目有关:分块数目越高,译码性能越好;高信噪比时,译码性能的结果波动较小,与码块分块方式无关。

图3 不同码块分块方式下的仿真结果

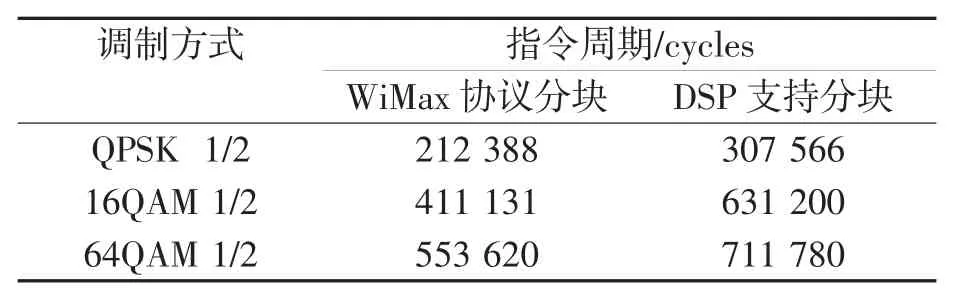

在DSP 平台上使用自带函数osTickTIme()统计每帧信号编码指令的时间开销,比较结果如表2 所示。由表可见基于WiMAX 协议的译码长度与DSP支持的译码长度在译码指令消耗时间上的对比:QPSK 1/2、WiMAX 协议分块比DSP 支持分块方式时间减少44%;16QAM 1/2、WiMAX 协议分块比DSP支持分块方式时间减少53%;64QAM 1/2、WiMAX协议分块比DSP 支持分块方式时间减少28%。

表2 每帧编码指令开销对比

6 结 束 语

MSC8156 DSP 的Maple 硬件加速器的资源有限,合理对资源进行配置,不但可以提高系统的利用效率,还可以提高系统运行的可靠性。在调试过程中,通过相应BD 环参数分析,可以更快、更准确地定位分析问题,提高效率。结果表明:研究信道编译码,依照系统性能要求,从工程实际情况出发,对编译码长度的选择,以内存资源、时间指令消耗、误码率高低等作为判决条件,能够合理地对编码译码做出系统优化。