SVDU的多协处理器并行化方法研究

赵 洋,汪 亨,吴延群,余 波

(中国核动力研究设计院 核反应堆系统设计技术重点实验室,成都 610213)

0 引言

人机界面是人与设备之间进行交互的重要媒介。人通过人机界面对计算机所控制的实际设备进行控制,同时人机界面会将计算机采集的设备信息反馈给用户,以便用户分析并作为决策的重要依据之一。根据不同的调查统计,在核电站中发生的重要事故和故障中,约60%的事故是由操作员的失误造成的[1]。因此,人机界面的功能重要性在核电系统中不断加强。

SVDU 作为安全级DCS 配套的数字化人机界面,其核心功能主要由基于CPU 的软件技术实现。为保证SVDU设备的高可靠性,其相关软件开发往往遵循“单任务运行”“限制中断使用”“固定周期运行”“静态内存分配”等保守性设计原则。这些设计原则使得SVDU 的应用功能开发与技术指标要求呈现矛盾状态,难以兼得。在工程实践中,牺牲功能丰富性和完善性来保证人机响应时间、页面刷新速率等技术指标要求会使SVDU 的功能偏向简单化,有时并不能够完全满足安全级DCS 配套人机界面的某些功能需求。

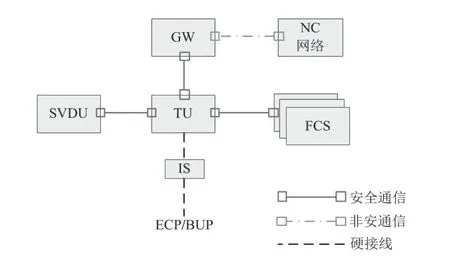

图1 安全级DCS简化连接图Fig.1 Simplified connection diagram of safety DCS

如果能够以新的设计方法来提升SVDU 设备的运行效率,使得功能和性能同时兼顾,又能有效保证可靠性,对于保障核电安全可靠运行具有重要意义。

1 SVDU功能分析

国内外应用于核电厂的SVDU 产品主要包括TXS QDS、MELTEC SVDU、Tricon SVDU 以及NASPIC SVDU。虽然各产品采用的技术不同,但在安全级DCS 中发挥的作用类似。SVDU 作为安全级DCS 配套的人机界面,为操作员提供状态监视、手动干预系统运行的能力。图1 是安全级DCS 中的简化连接图,各模块的功能如下:

GW:网关站(Gate Way),实现安全级DCS 与NC 网络的通信隔离。

TU:传输单元(Transfer Unit),实现SVDU、FCS、TU、GW 之间的数据中转传输,通过TU 能够将各个单一的站点通信互联,构成较大的控制通信网络。

FCS:自动控制单元(Fieldbus Control System),执行数据采集、逻辑运算及输入输出控制。

ECP/BUP:独立于安全级DCS 的应急盘(Emergency Control Panel)和后备盘(Backup Panel)。

SVDU:安全级图形显示单元,通过TU 获取需要监视的网络变量,通过TU 将控制指令发送到FCS 中。

在安全级DCS 中,SVDU 需要完成的功能包括但不限于:

1)反应堆保护系统功能的闭锁及复位。

2)通道旁通状态显示。

3)长时间PAMS 变量记录和趋势显示。

4)T3 定期试验。

5)停堆断路器复位。

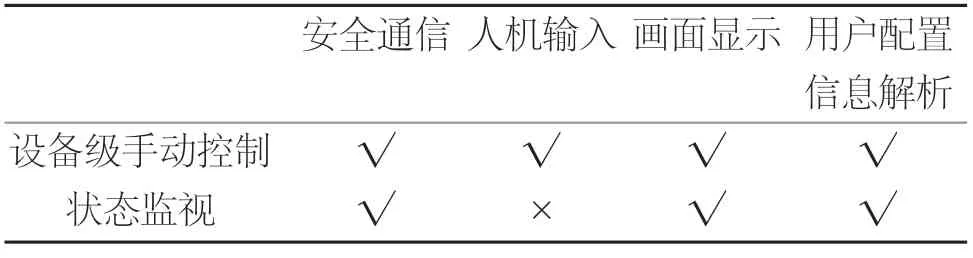

表1 SVDU设备功能与系统功能的关系Table 1 The relationships between SVDU device functions and system functions

在系统运行中,SVDU 的故障可能会导致操作模式由KIC 模式切换到BUP 模式[2]。因此,SVDU 的功能大多可由BUP 代替。总体上,SVDU 发挥着与BUP 相似的功能。在设备级手动控制方面,可以认为SVDU 与BUP 构成了多样化的人机输入手段;在状态监视方面,SVDU 借助自身的大屏幕和多种显示形态的图形控件,能够代替大量BUP 盘面布置的信号状态指示灯、参数监视仪,使得BUP 仅保留必要的信号监视,能够简化BUP 的设计复杂度。

2 SVDU设备底层支撑技术分析

从安全级DCS 整体的角度来看,SVDU 主要执行的系统功能有两个:

1)设备级手动控制。

2)实时状态监视。

为满足以上系统功能,SVDU 需要具备以下设备功能:

① 安全通信:能够与TU 进行双向安全通信。

② 人机输入:具备接收来自用户人机输入指令的能力。

③ 画面显示:以图形、数值、文本、趋势及日志等多种显示形态反映状态监视的实时值和历史值。

④ 用户配置信息解析:SVDU 是一款组态型设备,所有显示画面均在离线组态后下装至设备中。因此,需要具备解析用户组态配置信息的功能。

SVDU 系统功能与设备功能的关系如表1 所示。

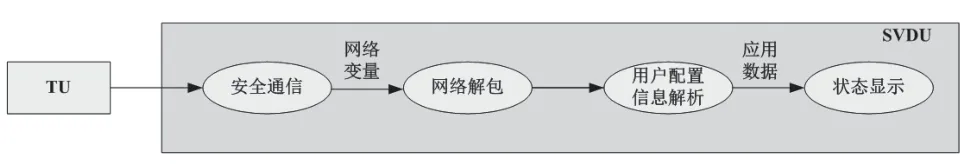

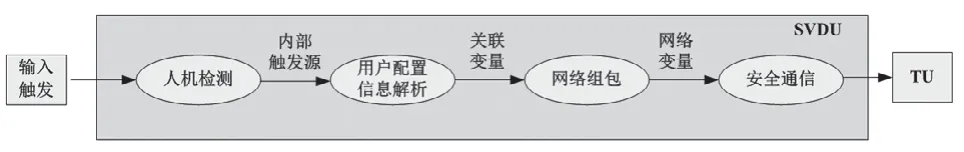

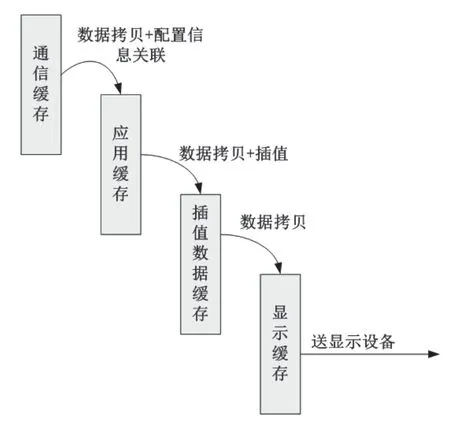

图2、图3 描述了状态监视和设备级手动控制的数据流向及其经过的处理环节。

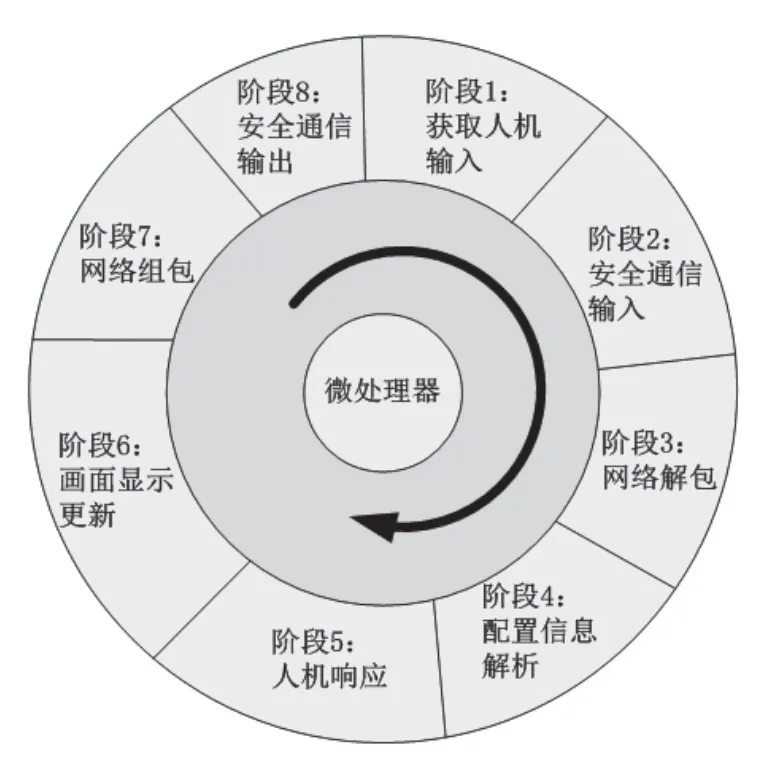

SVDU 软件在满足“单任务运行”“固定周期运行”等设计原则的前提下,在一个固定的运行周期内,将按照图4 所示机制固定地分配时间片段,确定、顺序地执行各项设备功能。

如果SVDU 中某个控件涉及的设备功能过于复杂,图4 中的各个时间片段将增加,进而增加运行周期,降低SVDU 人机响应和数据更新速度。在“限制中断使用”“无人机输入输出缓存”的设计中,系统还有可能丢失人机输入信息,严重影响SVDU 安全功能的可靠性。

图2 状态监视的数据流向Fig.2 The data flow of status monitor

图3 设备级手动控制的数据流向Fig.3 The data flow of device-level manual control

图4 SVDU固定时间片段运行机制Fig.4 SVDU running mechanisms based on fixed time slice

航空和工业控制等诸多领域对计算系统要求越来越高,嵌入式计算机系统日益复杂[3]。因此,不得不引入操作系统来实现任务调度和硬件管理。与此类似,某些SVDU 产品中也使用基于实时性操作系统的多任务处理机制来提升并发数据处理能力。任务管理和调度是操作系统的核心功能之一,而任务调度必然会引入程序指针重赋值的软件或硬件中断,带来严重的不确定性,背离了安全级软件的设计原则;同时会导致软件的确定性评估以及验证确认工作变得复杂且困难。此外,操作系统的引入,使得硬件资源需求提升,硬件复杂度的增大反而会导致SVDU 的可靠性预计指标下降。

3 多协处理器并行化方法在SVDU中的应用

“单任务运行”“固定周期运行”等设计约束本质上是为了保证SVDU 软件的行为简化,有利于可靠性分析。如果能将图4 所示各个时间片的功能聚合为多个独立的协处理器,在统一的时序节拍驱动下,各个协处理器尽可能地同步并发执行,将极大提升对应用功能的处理能力,各个模块的功能复杂度也可以保持在较低水平。

3.1 多协处理器并行化方法的架构

图4 中各个时间片代表的SVDU 各子功能,可以被聚合为以下具备一定独立性的协处理功能:

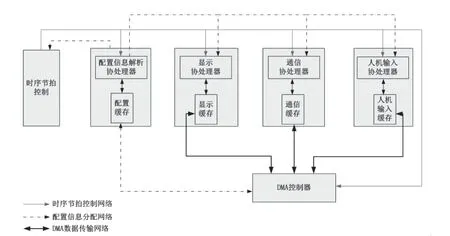

图5 基于多协处理器并行化方法的SVDU技术方案Fig.5 The method of SVDU based on multi-processor

1)用户配置信息解析协处理功能。

2)显示协处理功能。

3)通信协处理功能。

4)人机输入协处理功能。

为了保证各协处理功能有序地运行,需要配备专门的时序节拍控制模块。在执行SVDU 系统功能时,各协处理功能间需要执行数据传输。因此,需要配备专门的DMA 控制模块。

按照以下两个原则可构建起如图5 所示基于多协处理器并行化方法的SVDU 技术方案:

原则1 同步性

各协处理器有统一的时序基准以保证SVDU 行为的确定性。

原则2 并行性

本方法是一个去中心化的设计,除时序节拍控制外,其他协处理器地位等同。任意两个或多个协处理器能够配合实现SVDU 的应用功能。

图5 中各协处理器的功能描述如下:

a)时序节拍控制模块

本模块为SVDU 运行提供时序基准,输出的同步时序节拍定义了SVDU 的运行周期以及各个时间点应该执行的功能。通过本模块来保证SVDU 功能的确定性。

b)配置信息解析协处理器

配置信息定义了SVDU 在不同的输入条件下应当具备的状态和输出行为。本模块在时序节拍的控制下,解析配置信息并将配置信息转换为需要的操作后以并行的方式分发到指定的协处理器中。每个配置信息解析处理器需要配套一个配置缓存,用于暂存配置解析前后的相关信息。

c)显示协处理器

显示协处理器在时序节拍的驱动下,既要实现对显示设备的驱动,又要按照特定的人机输入、配置信息以及通信网络变量实时地生成显示画面数据。每个显示协处理器需要配套一个显示缓存,用于实现显示画面信息的暂存。

d)通信协处理器

通信协处理器在时序节拍的驱动下,要完成多层安全通信协议的封装、解析、接收以及发送控制,又要与应用数据、人机输入数据配置信息关联。每个通信协处理器需要配套一个通信缓存,用于实现通信接收或发送数据的暂存。

e)人机输入协处理器

人机输入协处理器在时序节拍的驱动下,既要完成对实体按键、触摸屏等人机输入设备的驱动控制和坐标数据捕获,又要与配置信息关联以识别其关联的控件、通信网络变量等。每个人机输入协处理器需要配套一个人机输入数据和应用数据缓存,用于人机输入、应用数据关联等信息的暂存,避免人机输入信息的丢失。

f)DMA 控制器

以上各个协处理器中不存在中心节点,协处理器间存在数据传输的需求。DMA 控制器在时序节拍的控制下,按照配置信息的定义,实现协处理器间的数据传输控制。

3.2 多协处理器并行化方法的运行

基于单任务的SVDU 设备在执行“按钮”类设备级手动控制功能时,需要顺序地执行以下5 个动作:

1)捕获人机输入

定期扫描人机输入设备,如果有人机输入则开始准备人机响应,否则在下一个周期继续扫描人机输入设备。

2)人机响应关联

在已捕获到人机输入的前提下,结合配置信息,确定应该执行的具体人机响应内容,如果配置信息未定义人机响应,则放弃人机响应操作,在下一个周期到来时继续扫描人机输入设备。

3)人机响应输出控制

在人机响应关联完毕的前提下,在显示缓存的某一区域内产生人机回馈显示数据,并将该信息输出到显示设备上,提示操作员SVDU 已经捕获到人机输入。

4)网络变量关联

通过配置信息的定义,识别该人机输入是否关联相应的网络变量。如果关联了网络变量,则将对应的网络变量设置为指定数值,否则放弃本次操作。

5)通信输出

将网络变量包通过安全通信发送至TU。

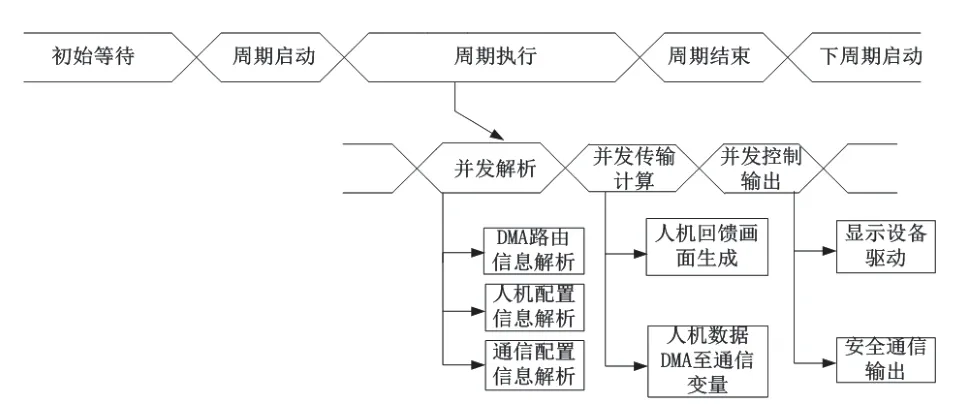

以上顺序动作在多协处理器并行化方法下,将精简为图6 所示的时序。

图6 设备级手动控制时序Fig.6 Device-level manual control timing

图6 中,周期执行阶段的具体操作如下:

a)并行配置信息解析

配置信息解析协处理器解析主体的配置数据,产生DMA 路由控制信息。显示、通信、人机输入协处理器解析自身所需要的配置信息。

b)并行数据处理与传输

显示、通信、人机输入协处理器通过DMA 获取到自身所需数据,按照预定义的时序节拍结合各自解析的配置数据,并行地实现通信、人机、显示数据计算。

c)并行数据输出控制

在上一步的基础上,各协处理器并行执行各自的功能。

在涉及复杂数据传输、数据运算的功能执行时,多协处理器并行化方法将体现出巨大的优势。下面以事故后监测系统(Post Accident Monitor System,简称PAMS)变量趋势显示为例进行说明。其他复杂的状态监视功能与此类似。

基于单任务的SVDU 设备进行PAMS 变量趋势显示时,通常需要顺序地执行以下动作:

① 获取通信数据。

② 通信数据与配置信息关联,转换为应用数据。

③ 应用数据通过插值算法连续化为显示数据。

④ 显示数据输出至显示设备。

以上各个步骤顺序执行过程中牵涉到大量的数据重复搬运工作,如图7 所示。

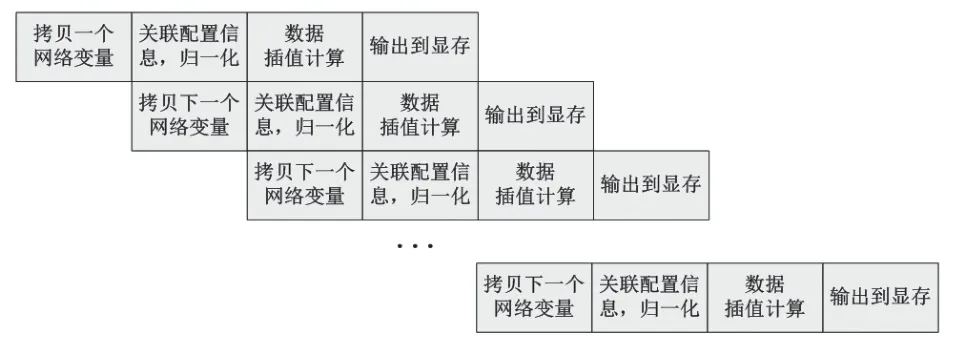

采用多协处理器并行化方法,则PAMS 变量的趋势显示可按照图8 所示的时序执行。

具体地,基于多协处理器并行化方法能够使得PAMS变量的趋势显示实现四级流水线处理,如图9 所示。数据吞吐率提升3 倍,在每个时序节拍可以完成一个PAMS 采样点的数据搬运、数据归一化处理、数据插值计算和输出显示。通过这种方法,一方面可以在单幅SVDU 画面上显示更多的PAMS 变量趋势,另一方面更有利于某些复杂的数据插值和连续化算法的实施。

3.3 多协处理器并行化方法的技术实现

多协处理器并行化方法将SVDU 中的主要功能聚合为独立的协处理器,主要有以下2 种实现方式:

图7 顺序化PAMS变量趋势显示流程Fig.7 Sequential trend display proc

1)基于多个通用微控制器元件的协处理器阵列

各个协处理器使用独立的微控制器,通过板上总线连接,互相配合实现SVDU 的各项功能。这种实现方法存在以下问题:

◇ 元器件增多,可靠性预计指标下降。

◇ 板载通信接口、协议繁杂,限制整体性能提升。

◇ 某些特殊功能无法定制化,例如流水线处理、数据突发访问等。

2)基于FPGA 的SOC

FPGA 的片上逻辑资源、布线资源以及RAM 资源越来越丰富。同时,随着制程工艺的提升,FPGA 在执行相同逻辑功能的功耗与传统的ASIC 器件已经相差不大。这些有利条件使得基于FPGA 的SOC 技术在面向小批量、柔性定制功能的应用中具有明显优势。通过SOC 的方式,不仅能克服通信接口的复杂,还能实现片上系统的集成[4]。

基于FPGA 的协处理器并行化方法具体实施方式如下:

◇ 利用FPGA 片上的逻辑资源、RAM 资源、布线资源来构建各协处理器。

◇ 利用FPGA 上的逻辑资源、布线资源来构建各协处理器间的片上并行通信总线。

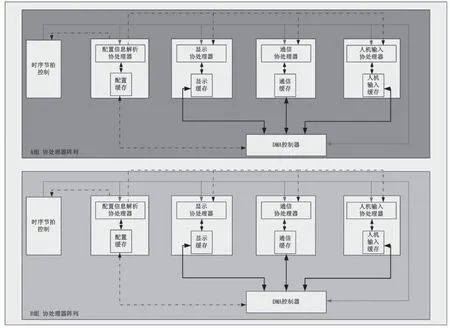

目前,多核处理器按照集成方式不同,可以分为同构多核处理器和异构多核处理器[5]。多协处理器并行化方法的实现需要结合同构和异构的特点。因此,在图5 的基础上,构造了双冗余—混合型架构片上系统,如图10 所示。

图10 中,A 组协处理器阵列和B 组协处理器阵列采用完全相同的设计并执行相同的功能,可视为两个同构的处理器核,用于满足目前核电厂业主对SVDU 越来越高的可靠性要求。通过同构的冗余处理器核,使得即便在硅片上也实现了冗余功能,对于防范由于硅片部分区域损坏带来的安全功能丧失具有重要意义。

图8 PAMS趋势显示时序Fig.8 PAMS trend display timing

图9 四级流水线PAMS变量趋势显示Fig.9 Four-level pipeline methods for trends display of PAMS variables

在A 组或B 组协处理阵列内,各协处理器可视为多个异构处理器核,执行不同的功能。通过异构的处理器核设计,能够有效发挥各协处理器的专业功能,有效提升处理能力。此外,在A 组协处理器阵列和B 组协处理器阵列间还可以增加锁步、互相监督等手段来提升可靠性。

3.4 多协处理器并行化方法的优劣

多协处理器并行化方法具有以下明显优势:

1)不明显增加系统运行的功能复杂度

每个协处理器只执行特定的功能,其运行的复杂度小于单任务模式。在统一的时序节拍驱动下,所有时序流程均是清晰明确的,确定性高,有利于可靠性分析预测。

2)简化测试验证流程

多协处理器并行化方法将显著减小软件测试和验证确认(Verification & Validation,简称V&V)的工作难度。各个协处理器间接口和时序关系明确,测试和V&V 可以按模块逐个开展。

3)改善系统自诊断方法并提高安全性

多协处理器并行化方法可以使得精确和完善的自诊断监视方法的实施更为简单和方便。这也使得SVDU 可以不再依赖特定的具有高安全完整性等级的CPU,有利于进一步提升SVDU 的自主可控能力。

当然,多协处理器并行化方法也有其不足之处:

图10 双冗余-混合型架构Fig.10 Dual redundant hybrid architecture

a)芯片资源需求增加

随着半导体技术进步以及实际设备的低功耗、小型化、智能化的实际需求,多协处理器并行化方法必然是基于片上系统技术,即在单FPGA 或ASIC 上集成多个协处理器核和附属的数据缓存,这又对目标芯片的布线资源、计算资源、存储资源等提出了较高要求。

b)引入了额外的安全风险

节拍控制器定义了SVDU 所有行为的先后关系。准确可靠的节拍控制直接决定了SVDU 运行的正确性。节拍协调控制的引入可能带来潜在的共因故障风险。

c)前期调试工作较为复杂

多协处理器并行化方法是针对特定的需求开发的非标准架构,在前期工作开展中,还需要增加调试工具设计,加重研发工作负荷。

4 结束语

本文通过梳理SVDU 的系统功能和当前设备底层支撑技术的局限性,提出了多协处理器并行化方法,并阐述了该方法的系统架构、运行机制以及技术实现的细节,同时分析了该方法的优劣性。多协处理器并行化方法具有并发执行高效率、功能验证方便等突出优势,对于未来SVDU产品的持续改进升级具有一定的启发意义。