基于STM32的多功能数字存储示波器

蒋江红,张玉梅

(陕西师范大学 计算机科学学院,陕西 西安 710119)

0 引 言

传统数字存储示波器普遍存在体积大、价格昂贵和不方便携带等问题[1-2],主要是在一些有条件的实验室环境下使用,对于一些条件比较恶劣和环境复杂的场合,使用起来往往比较困难。为了解决这些问题,设计了一种FPGA与STM32相结合的便携式数字存储示波器系统。由于示波器的性能、复杂度和成本与数据处理端信号的采样、存储和处理有关[3-4],FPGA与其他微处理器相比,不仅处理速度较快而且接口资源丰富[5-7],因此可以结合FPGA在逻辑控制以及高速信号采集方面的优势来提高数字存储示波器的性能。

FPGA主要包括基准时钟、分频器、门限生成、采样率控制几个功能子模块[8-9]。另外根据μc OS II操作系统和μc GUI图形界面系统在LCD显示的实时性以及执行任务的灵活性[10],采用模块化的设计方法,极大地提高了系统在复杂工作环境下进行信号检测的效率。

1 系统总体方案

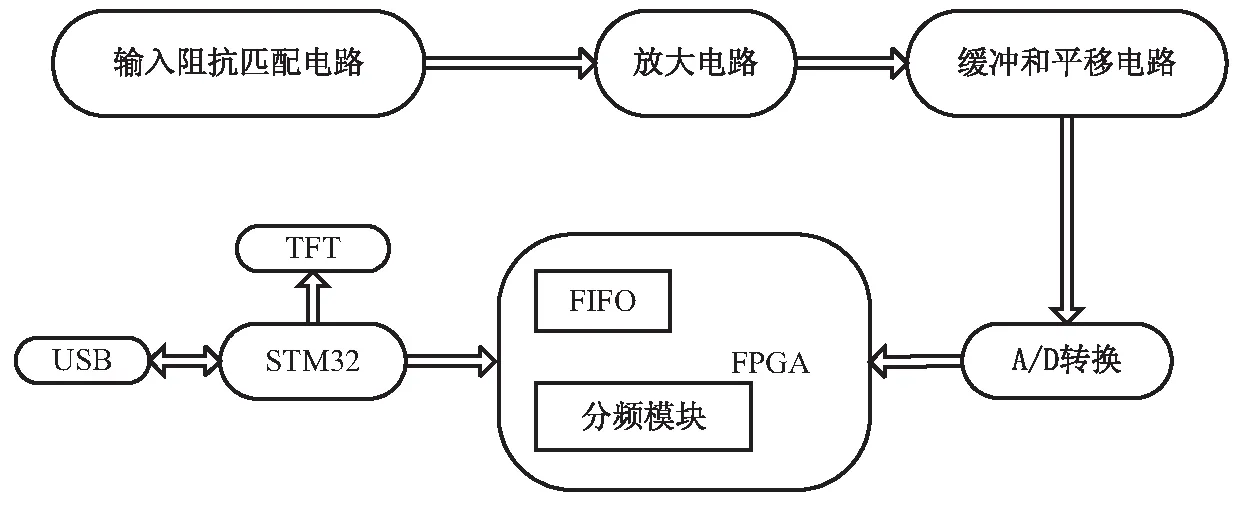

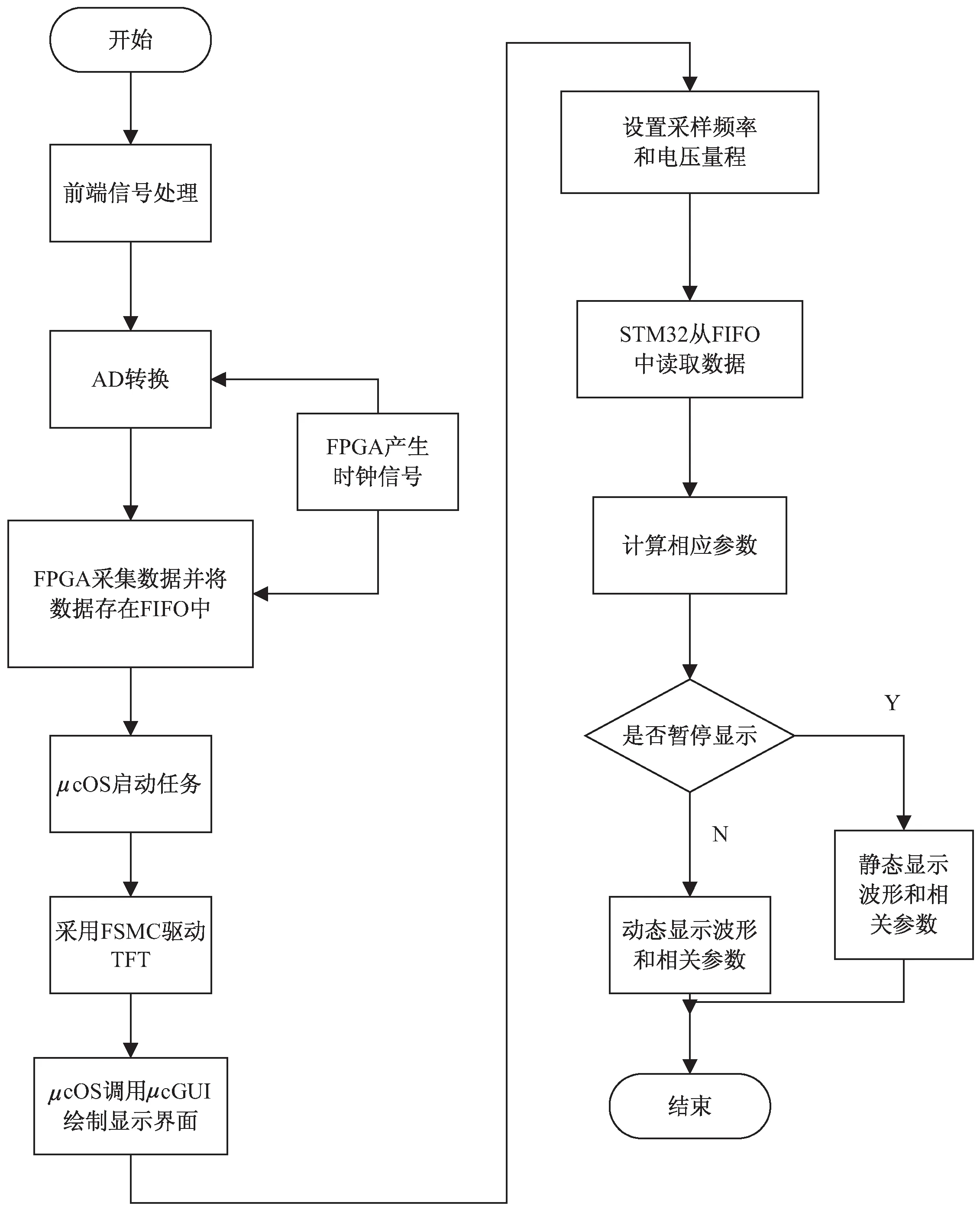

整个系统采用FPGA+STM32相结合的工作方式,STM32作为系统的控制核心[11],主要完成示波器的信号分析、处理、变换,系统功能控制和显示操作等工作;数据信号的采集控制和显示控制等工作由FPGA完成。系统总体框图如图1所示。

图1 系统总体框图

2 系统硬件设计

2.1 前端信号调理电路

系统中前端调理电路的作用主要是为了产生适合于进行高速AD转换的信号[12]。该部分由输入阻抗匹配电路、放大电路、信号缓冲电路和电平平移电路组成,其中输入阻抗匹配电路主要是为了避免由于接上的负载干扰电路的正常工作;放大电路的主要功能是适当调整信号的幅度,以便后续电路对信号的处理;信号缓冲电路和平移电路的主要作用是对传输的信号进行处理,以便产生适合AD转换的信号。

2.2 上升沿触发信号产生电路

比较电路是上升沿触发信号产生电路的关键组成部分,该电路工作的过程是将输入信号与设定的触发电平即门限电平进行比较,当输入信号的幅度大于设定的阈值时,比较器输出上升沿跳变,形成触发信号,为后续显示提供FIFO输出参考[13]。通过引入正反馈来形成迟滞电平,从而完成迟滞比较和消除噪声干扰。

2.3 AD数据采集电路及采样分析

数据采集电路中的AD芯片选用的是双核8位单芯片模数转换器AD9288。该芯片内置片内保持电路,采用100 MSPS转换速率工作,每个通道均可以独立工作。为了简化硬件电路的设计以及消除其他信号的干扰,AD数据采集中的采样时钟由FPGA提供;通过改变采样频率来实现扫描速度的改变。信号的采样分为实时采样和等效采样,为了提高系统的性能,系统将两种方式相结合,当输入信号频率低于20 MHz时,选用实时采样;反之,选用等效采样。

2.4 FPGA电路设计

FPGA电路主要包括时钟分频电路和FIFO电路,通过在FPGA内部设计一个分频电路来选择不同的采样频率,确保数据采集系统具有较大的测量范围,利用程序来实现电路的不同分频比,从而使时钟满足AD采集需求。为了实现对AD采集数据的快速存储,设计大小为4 096 B的FIFO,AD采集电路开启时,FIFO开始存储数据[14-15]。

2.5 中央控制系统的设计

该系统的中央控制器采用的是低功耗的Cortex-M3系列的STM32芯片[16],该芯片的最大工作频率为72 MHz。中央控制器的主要功能是以一定的时钟频率读取FPGA内FIFO中的数据,并对数据进行相应处理,以便重建信号波形;显示部分使用的是具有触摸功能的TFTLCD,分辨率为400*240,通过STM32的FSMC接口来控制该显示器。

3 软件设计及流程图

3.1 FPGA的程序设计

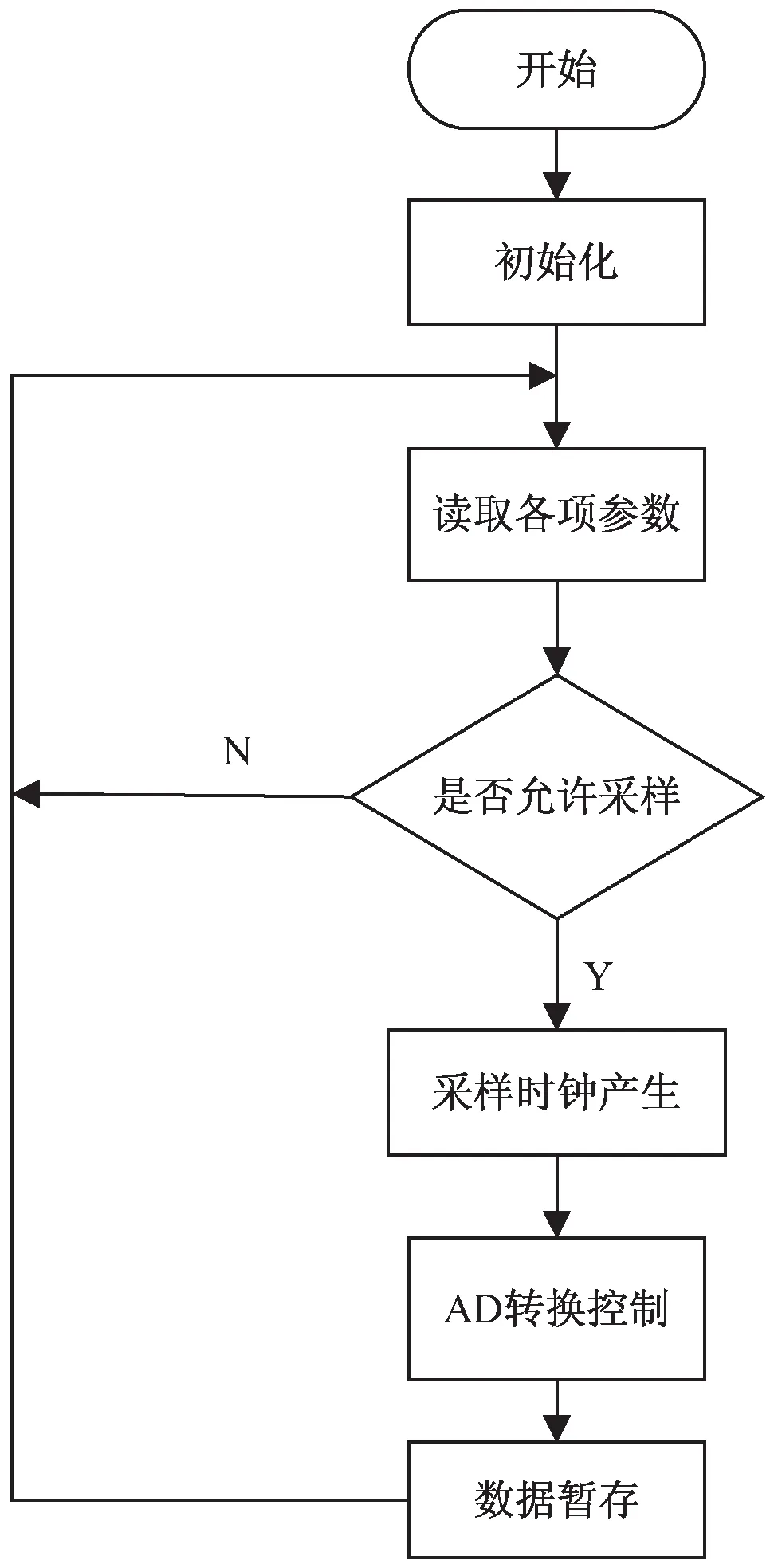

系统通过FPGA进行数据的采集和AD转换控制,分为AD采样控制模块和FIFO读写数据控制模块,其中采样控制模块产生一个时钟信号,控制AD工作,以及将AD转换后的数据写入到异步FIFO中;读写数据控制模块用来控制数据的读和写。FPGA的程序设计流程如图2所示。

图2 FPGA程序设计流程

3.2 示波器参数测量的程序设计

数字存储示波器的参数分为幅度参数和周期时间参数,其中幅度参数是根据各通道的量程来计算,时间参数是依据时基来计算。

根据脉冲参数的定义,在参数测试中只需要知道波形顶值电压、底值电压、10%电压、50%电压、90%电压等几个关键的电压值,就能在此基础上找到对应电压值出现在待测波形数据中的相对位置,从而实现各参数的测试。

3.2.1 频数直方图密度分布众数法

由于波形的顶值和底值可能不是波形的全局最值,为了较精确地获取波形的底线和顶线数据,采用频数直方图密度分布众数法将出现次数比整个显示点数的5%多并且反复出现的点作为最一般常见点,当这种类型的点不存在时,分别将正峰值和负峰值作为波形的顶值和底值。

3.2.2 周期和频率的测量

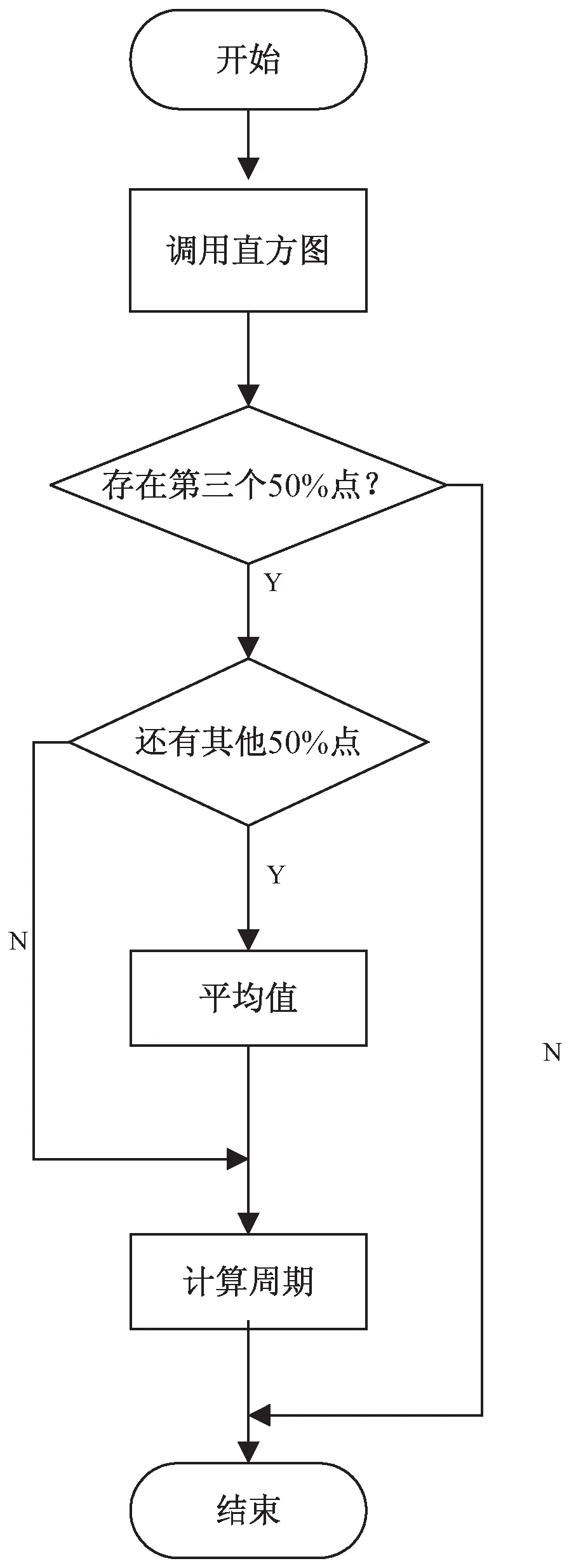

根据定义可知,通过信号周期可以计算频率,因此可以先测出周期,其倒数即为频率,当信号周期不存在,其频率也不存在。定义计算周期的步骤为:

(1)信号的顶值和底值是通过直方图方法来确定;

(2)计算出50%电压值:50%电压值=底值电压+(顶值电压-低值电压)*50%;

(3)对于周期的测量需要找到连续的3个数值和50%电压值相等的点的屏幕坐标;当没有等于50%电压值时,找到与50%电压值最接近的点;

(4)周期=(第三个50%点的坐标-第一个50%点的坐标)*单位时间值。

当时基较小,可以求出所有50%点,通过50%点的平均值的算法提高精确度;当时基较大时,第三个50%点不是第300个点时,由于每屏为300个点,可以继续寻找下一个50%点直到第300个点为止。程序流程如图3所示。

3.3 主控制器的程序设计

主控制器软件系统的主要功能是读取FPGA中采集到的用于波形分析和重建的数据,为了提高系统的实时性和可维护性,系统采用源码公开的UCOS多任务实时操作系统,同时充分利用系统底层CPU寄存器来编写出高效率可靠的实时应用层代码。

在波形的显示上主要采用嵌入式图形软件UCGUI,由于其采用模块化的设计,LCD驱动程序包含了对LCD的全部访问接口,因此适用于任何LCD控制和CPU的任何尺寸的物理和虚拟显示。系统的控制流程如图4所示。

图3 周期测量流程

图4 系统控制流程

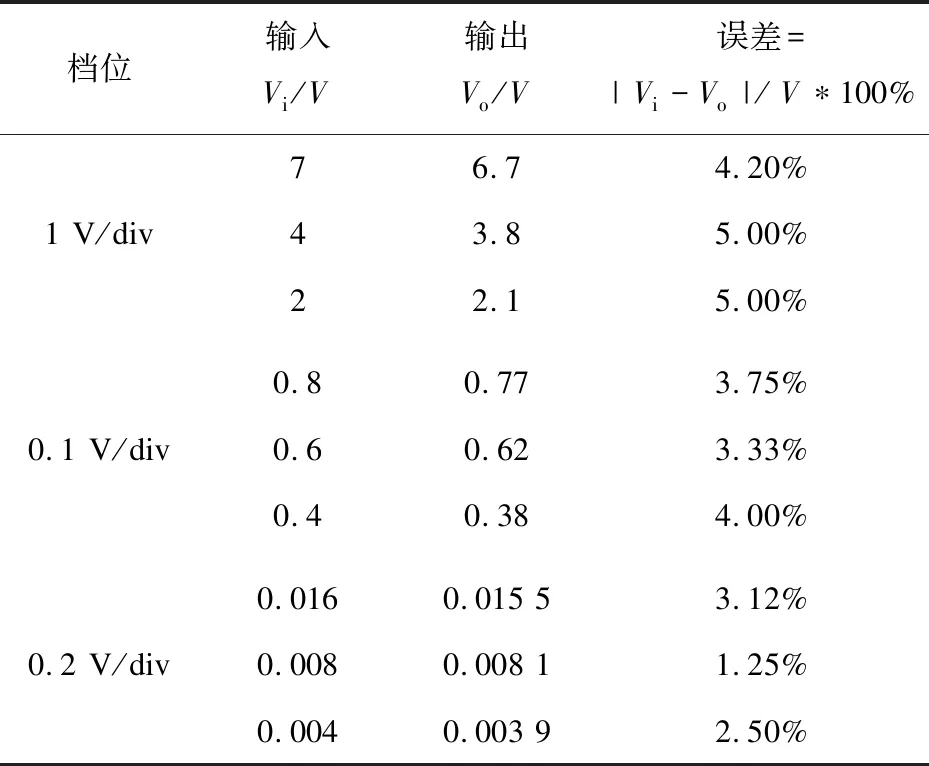

4 系统测试及误差分析

基于以上设计和硬件平台,分别进行了水平分辨率测试和垂直灵敏度测试。系统测试如图5所示,观察示波器产生的扫描电压以及在信号上升沿开始显示波形。通过实际观察能够产生扫描电压,并正常显示波形。在垂直灵敏度测试的正弦信号频率为10 kHz时,测得的数据如表1所示。

档位输入Vi/V输出Vo/V误差=|Vi-Vo|/V∗100%1 V/div76.74.20%43.85.00%22.15.00%0.1 V/div0.80.773.75%0.60.623.33%0.40.384.00%0.2 V/div0.0160.015 53.12%0.0080.008 11.25%0.0040.003 92.50%

由表1数据可知,测量结果都在测量误差允许的范围内,很好地完成了设计任务。

5 结束语

系统在设计中主要有以下三个难点:系统前端调理电路设计,该部分电路设计的好坏是整个系统能否正常运行的关键;触发电路的设计;提高被测波形的相关参数测量的精确度一直都是重点解决的问题。系统的创新主要体现在:一、系统将高速逻辑控制器件与单片机结合在一起,能够将两者的优势发挥出来,分工合作使其设计的效果达到最佳;二、采用高速的AD转换芯片,提高了系统的带宽;三、将嵌入式实时操作系统与嵌入式图形界面结合在一起,比较精确地重建了波形。