基于PC104+的转台信号处理器设计与实现

陈雪坤,扈宏杰

(北京航空航天大学 自动化科学与电气工程学院,北京100191)

转台(包括仿真转台、测试转台及程控转台),是航空航天及兵器系统中的型号研制及生产标检过程的关键设备,除其系统精度要求高以外,其可靠性也是极其重要的指标。 基于工控机的转台控制系统中,早期采用ISA(industry standard architecture,工业标准体系结构)总线,后为提高速度采用PCI(peripheral component interconnect, 外设部件互连标准)总线与外设接口,而板卡连接“金手指”易受潮湿、振动等复杂环境影响[1-2],引发连接故障,致使整个转台系统的可靠性下降。 针对以上问题,可采用CPCI 总线(compact PCI,紧凑型PCI)的方法,抛弃金手指互连方式,可靠性得到保证[3-4],但是成本较高,适合于型号设备。另一种解决方法是采用PC104总线接口,物理连接采用插针形式,可靠性很高,且适合实验室设备环境。

PC104+总线兼容PCI 协议,既可满足系统的实时性,又可保证系统可靠性[5-6]。 故在此,转台控制系统采用了基于PC104+总线的嵌入式计算机作为的主控计算机,设计了PCI 协议的信号处理卡,基于DSP(digital signal processor,数字信号处理器)和FPGA(field programmable gate array,现场可编程门阵列)核心元件,实现了成码盘信号采集、数字输入输出信号处理、控制结果输出、集串口远程通讯等功能于一体。

1 转台系统总体结构

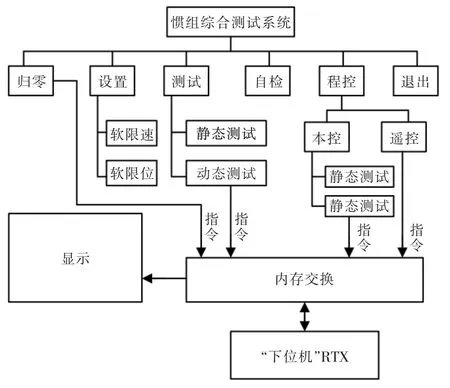

转台控制系统总体结构如图1 所示。

图1 转台系统结构Fig.1 Turntable system overall structure

主控计算机采用PC104+嵌入式计算机, 搭载Windows XP 系统, 通过VC++编写人机交互界面,完成界面管理、参数配置、指令等功能。 具体功能如图2 所示。

图2 人机界面功能Fig.2 Function of human-machine interface

转台直接控制级为RTX 实时子系统,构成3 个独立的伺服控制回路,实现控制算法。 信号处理卡主要由CH365 桥路芯片,DSP、PFGA 主控芯片、双口RAM、D/A 转换、运放等外围电路组成,主要完成D/A 输出、码盘信号采集、与远程计算机及主控计算机的通信的功能。DSP 和CH365 负责与主控计算机的通讯,FPGA 负责与远程计算机的串口通信和码盘数据采集和处理。

2 系统硬件设计

2.1 PC104+接口设计

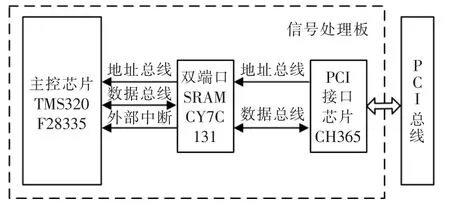

PC104+总线兼容PCI 协议,PCI 总线分别32 位和64 位,最大传输率可达264 MB/s。 其独立于CPU总线,故能够支持多种处理器,但是相较于ISA 等总线,PCI 总线协议复杂, 使用FPGA 设计比较困难。 在此转台系统采用专门的PCI 接口芯片CH365进行接口设计。

CH365 是PCI 总线的通用桥路芯片,其应用如图3 所示,能够实现32 位PCI 总线接口,将其转换为8 位数据并行接口, 带有16 为地址线, 可直接DSP、FPGA 等主控芯片。 由于转台系统通信数据量较大,故使用双口RAM 进行缓冲。

图3 PCI 接口Fig.3 PCI interface

PCI 接口芯片CH365 的PCI 总线端与嵌入式计算机通过插针连接, 本地总线端与双端口SRAM连接,双口SRAM 另一总线端与DSP 总线连接。 通过接口芯片,可以直接通过计算机的端口操作对双端口SRAM 中的数据进行读写。 通过对双端口SRAM 指定地址的写入产生的外部中断,对DSP 进行控制。

2.2 FPGA 电路设计

FPGA 根据码盘协议要求发送时钟信号,经电平转换,差动转换后输出,同样码盘信号经过差动转换,电平转换后进入FPGA。 FPGA 电路如图4所示。

图4 FPGA 电路Fig.4 FPGA circuit

3 信号处理器的软件设计

信号处理器软件按照功能可分为以下几部分:①串口通信 采用RS422 协议实现与测发控的通信;②PCI 通讯 将串口接收的测发控信息与码盘卡接收的码盘信息通过PCI 总线协议实现与计算机的通讯;③SPI 输出 将计算机的控制指令通过SPI 串口输出,经D/A 以及放大后送至驱动器;④信号采集 主要利用FPGA 器件实现对外围器件的逻辑控制,读取码盘数据信号。

3.1 数据采集模块

以FPGA 为核心的数据采集模块如图5 所示。该系统选用Intel 公司Altera 系列芯片,有较高的波特率,能够实时读取三路码盘信息,同时生成内部硬件逻辑模块双口RAM,将采集到的码盘信息存于双口RAM 等待DSP 读取。

图5 以FPGA 为核心的数据采集模块Fig.5 FPGA-based data acquisition module

数据采集模块的主要工作内容如下:

1)码盘数据的采集。 编码器协议为BISS 协议,BISS 是一种同步串行通讯协议,时序如图6 所示。

图6 BISS 码盘时序图Fig.6 BISS encoder timing diagram

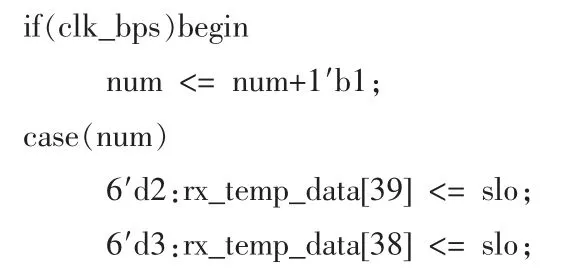

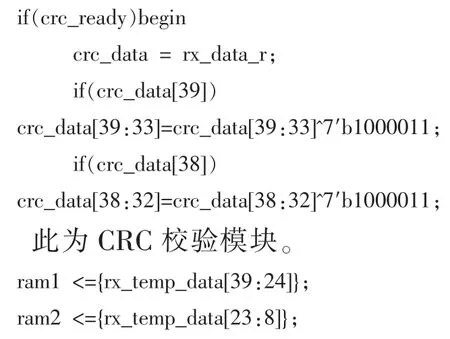

根据协议要求,FPGA 向编码器输入时钟信号,编码器即按该时钟信号进行数据传输,FPGA 按该时钟信号按位接收,去掉帧头帧尾,经过校验后存入内部RAM 的指定地址,等待DSP 访问。部分程序如下:

assign ma =(scl_r || flag2);

ma 为FPGA 输出时钟信号;scl_r 为内部分频出的合适波特率;flag2 为控制开关。

此为接收模块,FPGA 按照编码器发送的波特率按位接收数据。

通过校验的数据赋给16 位数组ram1 和ram2等待存入双口RAM。

通过对写信号置高, 并将数据赋给数据总线,地址赋给地址总线, 将采集的码盘数据存入双口RAM 指定区域。

2)与DSP 之间的通讯。 FPGA 生成DRAM 逻辑模块,与DSP 的16 位数据总线、外部寻址片选信号线、读信号线、写信号线以及地址总线相连。 DSP 通过访问FPGA 内部DRAM 读取码盘数据。

3)FPGA 读取双口RAM 中上位机的控制指令,通过SPI 输出, 经D/A 转换并放大后送至驱动器,完成对电机的控制。

3.2 PCI 驱动模块

为使上位机能够对PCI 设备操作,需要有相应的驱动程序,进行地址映射。PCI 设备查找流程如图7 所示。

主要步骤如下:

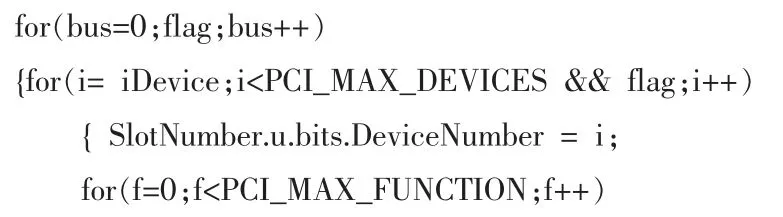

步骤1遍历PCI 插槽,寻找信号处理卡。主要程序如下:

图7 PCI 设备查找流程Fig.7 PCI device discovery flow chart

由于计算机的多级总线结构, 遍历PCI 设备时,首先从PCI Bus0 开始,然后在PCI Bus0 总线上遍历挂接在其上的所有PCI 设备。另外,单个PCI设备可能还有多个功能, 因此还需要遍历其功能号,找到PCI 设备后,获得其设备信息PciData,对比其设备号,厂商号是否与目标设备一致。

信息一致则进行内存映射,否则继续查找PCI 设备。

步骤2调用CH365Map()函数,对板卡进行内存映射和端口映射,得到基地址BaseAddr365,之后可以通过(PUCHAR)((int)基地址+偏移量)直接对本地总线进行读写。 主要程序如下:

其中,RtTranslateBusAddress()函数作用为,将PCI 设备地址变为CPU 可直接访问的物理地址,RtMapMemory()函数则把该物理地址映射到虚拟地址。

3.3 PC104+通讯模块

计算机通过CH365 桥路芯片对双口RAM 进行读写, 另一端信号处理板主控芯片DSP 对双口RAM 进行读写,实现数据交换。 双口RAM 允许两端CPU 同时对不同存储单位进行读写,但是不允许同时对同一单位进行一读一写。 在此采用邮箱中断的方式,中断机制如图8 所示。

图8 中断机制Fig.8 Interrupt mechanism

图中, 上位机通过CH365 向双口RAM 最高位写入数据触发DSP 侧中断,DSP 在外部中断中判断中断信息, 执行读取码盘数据并写入双口RAM 或读取双口RAM 中指令信息。 在DSP 读取数据后该中断清除,以此邮箱中断的方式完成上位机与DSP的通讯。 DSP 程序设计流程如图9 所示。

图9 DSP 软件流程Fig.9 DSP software flow chart

4 结语

所设计的信号处理卡包括信号采集、信号处理、远程通讯、PCI 接口和DA 输出等模块;已成功运用于转台系统,取得较好效果,良好的集成度及丰富的功能减少了转台系统的外设数量,提高了系统可靠性。