面向航天应用的高可靠性FPGA动态局部重构

于志成 庄树峰 刘涛 王洋 杨秉新

面向航天应用的高可靠性FPGA动态局部重构

于志成1,2庄树峰3刘涛1王洋1杨秉新1

(1 北京空间机电研究所,北京 100094) (2 先进光学遥感技术北京市重点实验室,北京 100094) (3北京自动化控制设备研究所,北京 100074)

在航天应用中,FPGA的单粒子翻转是影响航天器功能和寿命的重要因素,目前,部分航天产品使用定时重加载的方式避免单粒子效应的积累和影响,但是重加载的过程会导致全部FPGA逻辑中断,极大影响航天器功能的持续性。因此,文章提出了一种适用于航天的FPGA动态局部重配置系统,在阐述了FPGA动态局部重配置技术的原理和航天应用前景后,详细说明了其设计流程、硬件电路板架构和控制软件框图。通过板级试验验证了系统功能,采用示波器对结果进行了测试,证明该系统设计的高可靠性。FPGA动态局部重配置技术,既提高了FPGA的可靠性,又保证了FPGA部分关键功能的持续性。

单粒子效应 现场可编程门阵列 局部重配置 可靠性 航天遥感

0 引言

FPGA动态部分可重构技术可以实现系统运行时FPGA内部逻辑资源的时分复用。动态可重构FPGA对全局或者局部的逻辑资源采用动态重构,从而产生需要的时序逻辑。对于SRAM型FPGA,通常都是通过对SRAM单元进行用户化,从而实现用户逻辑[1]。在综合时,有两种情况会导致FPGA的组合逻辑受到干扰,分别是LUT单元的某一位发生了翻转以及控制布线单元的某一位发生了翻转。当LUT单元的某一位翻转时,所有的组合逻辑就会发生改变,在这种情况下,只能重新下载配置bit文件进行纠正。而当控制布线单元的某一位翻转时,就会导致连线的连接或者分离,也只能重新下载配置bit文件进行纠正。因此,针对上述两种情况,最有效的解决办法为重配置FPGA[2-4]。然而,在航天应用中,有些遥感器上的FPGA模块往往不允许被中断。因此,本文提出了一种面向航天应用的高可靠性FPGA动态重构系统,该系统在保证当前执行程序不被中断的前提下,具备对部分待纠正的逻辑单元重新配置的功能,并且配置过程中不会影响其它逻辑单元的工作状态。基于局部动态重构技术,设计者可以引入时分复用的思想,利用有限的系统资源完成大规模的时序功能设计。

除此之外,目前的航天遥感器很难在轨进行程序升级,这对其灵活性有极大限制,可在线系统重配置是SRAM型FPGA的应用优势之一[5]。利用动态部分重构技术,可以实现卫星在轨接收FPGA配置bit文件,在不影响其它FPGA区域的情况下,FPGA自动对自己的某个预先定义好的区域进行重配置,从而克服了航天器在轨程序升级的难题,在轨平台资源得到了更充分的利用,节约了航天器的研发成本[6-8]。伴随着航天领域的不断发展,空间应用环境愈发复杂,航天器的设计要求也越来越高,研发成本不断上涨,面向航天应用的高可靠性FPGA动态重构技术将会得到更为广泛的应用[9]。

1 基于反熔丝FPGA控制的FPGA局部动态重配置

由于MicroBlaze在航天系统应用中的种种不足,现急需一种可靠性更高的FPGA局部动态重配置控制方法,反熔丝FPGA在航天中的成熟应用是一种最佳解决方案[10-12]。考虑到动态局部重配置是在Xilinx官方提供的一套固有机制下来控制和操作的,目前还无法对写入重配置数据的颗粒度进行修改。因此,本文主要是使用FPGA通过SelectMAP接口,在符合现有Xilinx机制的条件下,通过FPGA软件实现了对另一块FPGA的动态局部重配置。该方案与传统的基于MicroBlaze、PPC等控制方式相比,可靠性更高,也更适合于航天应用。本文试验部分也主要是针对该方案的软硬件设计进行功能性的验证,以证明其上述功能。

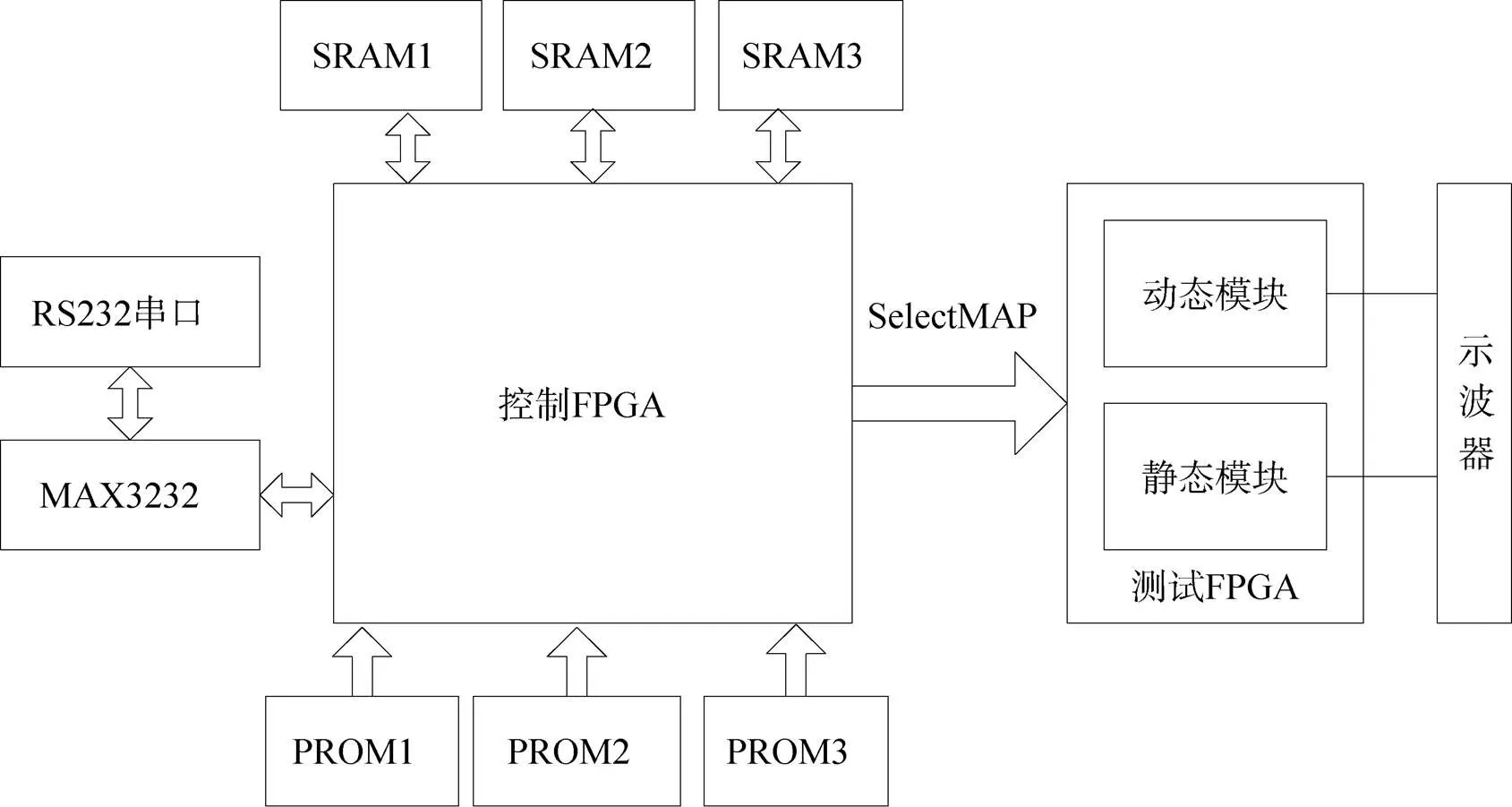

1.1 系统整体框图

基于反熔丝FPGA控制的FPGA局部动态重配置系统整体框图如图1所示。试验中使用一片控制FPGA替代反熔丝FPGA,验证方案的可行性,因此,系统中有两片FPGA。控制FPGA用来向测试FPGA写入配置数据,在控制FPGA的周围有3片PROM和3片SRAM,分别存放全局配置数据、局部配置数据1、局部配置数据2,用PC机向控制FPGA发送指令,来控制测试FPGA的配置过程。

系统上电后,控制FPGA运行,将PROM中的MCS文件读出,并转换成32位的并行数据储存到SRAM中。存储结束后,相应的LED变亮,这时,控制FPGA等待上位机的指令。当接收到0x03时,控制FPGA读出SRAM1中的全局配置文件,通过SelectMAP接口,写入到测试FPGA的配置存储器中,此时测试FPGA开始工作,输出波形;当控制FPGA接收到0x06指令时,读取SRAM2中的局部配置数据,通过SelectMAP接口写入到测试FPGA的配置存储器中,这时动态模块输出的波形发生改变,而静态模块输出波形不变;当控制FPGA接收到0x0c指令时,读取SRAM3中的局部配置数据,通过SelectMAP接口写入到测试FPGA的配置存储器中,此时,动态模块恢复为全局配置文件时的波形,静态模块依旧不发生变化。

图1 系统整体框图

1.2 重构FPGA配置文件的设计和生成

按照本文所采用的设计思路,如图2所示。将重构FPGA内逻辑资源区分为动态重构区域和静态区域两部分,其中,重构区域可以随时根据传入的动态局部配置数据而更新功能;静态区域中的配置逻辑是固定不变的,其功能不受动态区域逻辑重构的影响。相应的,重构FPGA共需要一个全局配置文件和两个动态局部配置文件,共3个配置文件。其中,全局配置文件主要用于在系统上电后对整个FPGA进行全局的功能配置,具体为在静态区域中实现了一个周期为1、占空比为50%的方波,同时将重构区域配置为周期为2的方波(同动态局部配置文件1);两个动态局部配置文件主要用于对重构FPGA中的动态重构区域的功能进行配置和升级,分别实现了周期为2和3的占空比为50%的方波。

图2 配置文件功能示意

在重构FPGA配置文件生成方面,主要采用Xilinx公司ISE开发环境中的PlanAhead工具,其优点是可视化程度较高,具备手动划分FPGA内部逻辑资源,并根据具体应用需求,对划分出的FPGA动态可重构区域中的各种资源进行可重构功能设定。具体操作步骤如下所示:

1)用ISE建立一个顶层模块top.vhd,如图3所示。顶层模块中包含三个子模块:静态模块S_LED、MicroBlaze处理器mb_xps和重构模块DPR_LED。

图3 顶层模块框图

2)设计两个可重构模块PRM1和PRM2。

3)建立一个PlanAhead工程,并将工程设置为局部重配置工程,将生成的各个网表文件以及全局约束文件添加到工程中。

4)利用PlanAhead集成的Floorplan工具手动规划出各个重构区域,然后为每个重构区域添加重构模块。其优点是可直观地看到各个重构区域的资源占用情况,如果占用率达到或超过100%,则需要重新手动规划重构区域。

5)运行DRC检测。

6)实现设计并产生比特流文件。

7)下载到电路板上调试。

通过上述操作,共生成3个配置文件:1)全局配置文件开头部分由冗余字、同步字、校验复位指令、设置配置选择寄存器、写入数据掩码、转换时钟频率、写芯片序列号、设置起始地址、进入写入配置存储器状态、设置配置数据长度等指令和数据组成。开始传输配置数据时,将所有配置数据写入到FPGA后,在配置文件的结尾包含CRC校验、空指令、最后一帧标识、最后一帧配置数据写入地址、发送启动序列以及掩码、校验指令,最后的同步指令标识配置结束。2)与全局配置文件的结构组成相比,动态局部配置文件省去了转换时钟频率、写芯片序列号、设置起始地址等步骤,在数据传输时,仅传输局部配置数据,数据量相对较小。同时,在配置文件尾部数据中也省去了最后一帧地址、启动码和掩码等部分。因此,局部动态重配置可以仅针对局部区域进行配置的功能升级而不影响其他区域功能,所需要的时间要明显小于全局配置的时间。在后面试验设计和结果分析中,将进一步对这部分结论进行板级试验验证。

1.3 控制FPGA软件设计

控制FPGA用于接收串口发送来的指令,并根据指令读取相应SRAM中的配置数据,并通过SelectMap接口写入到重构FPGA中。图4为控制FPGA软件框图。

图4 控制FPGA软件框图

1)配置数据读取模块PROMSRAM。由于FPGA是基于SRAM结构,每次掉电时,FPGA内部程序都会被清空,所以需要PROM在每次上电时对FPGA进行配置。设计中使用了3片PROM,分别存放全局配置文件、局部配置文件1和局部配置文件2,在RS232指令的控制下,读取不同的配置文件来对测试FPGA进行配置。如果每次都从PROM中读取的话,由于PROM的读取速度较慢,会严重影响增加测试FPGA的配置时间。为了避免这种情况,设计中使用了3片SRAM,每次上电后,由配置数据镀膜模块从PROM中读取配置数据,并将数据转换成32位并行数据存储到SRAM中,这样,每次对测试FPGA进行配置时,直接从SRAM中读取配置数据发送给测试FPGA,缩短了配置时间。

2)串行数据接收模块RS232。串行接收模块接收PC机发送来的RS232指令,并将接收到的串行指令转为并行八位指令发送给状态机模块。

3)状态机模块STATEMACHINE。状态机模块是本设计的核心控制模块,它接收串行数据接收模块输出的并行8位指令,根据指令,触发相应的配置控制模块对测试FPGA进行配置;配置结束后,接收配置控制模块的配置完成标志位,同时复位状态机,等待下一条控制指令。

4)配置控制模块ConfigCtrl。配置控制模块接收到状态机模块发送来的控制标志后,首先向SelectMAP接口模块发送01指令,这条指令用于清除FPGA配置寄存器中的数据;然后开始顺序读取SRAM1中的全局配置数据,并将配置数据发送给SelectMAP32模块,由SelectMAP32模块向测试FPGA中写入配置数据;配置结束后,测试FPGA的Done信号拉高,配置控制模块检测到此信号为高后,即产生配置完成信号发送给状态机模块。

5)局部重构控制模块DPRCtrl。在对测试FPGA进行全局配置结束后,可随时根据需要发送局部重配置指令,局部重构控制模块接收到状态机模块发送来的控制信号后,开始顺序读取SRAM中的全局配置数据,并将配置数据发送给SelectMAP32模块,由SelectMAP32模块向测试FPGA中写入配置数据。在配置结束后,由于测试FPGA的DONE信号不会再变化,因此需要检测向SelectMAP接口写入的数据。全部数据写入完成后,同时产生配置完成信号发送给状态机模块。

6)SelectMAP接口模块。SelectMAP接口模块接收配置控制模块或局部重构控制模块的指令或数据,根据指令操作测试FPGA的SelectMAP接口,或者向SelectMAP接口写入数据。

2 测试结果与分析

在设计试验中,使用PC电脑通过串口发送控制指令给控制FPGA,控制FPGA格局接收到的串口指令,相应地对重构FPGA进行配置,改变重构FPGA中的配置程序。同时,用示波器观察重构FPGA输出的信号波形,通过波形信号的变化,验证本文提出的动态可重构系统的功能。

具体操作步骤如下:

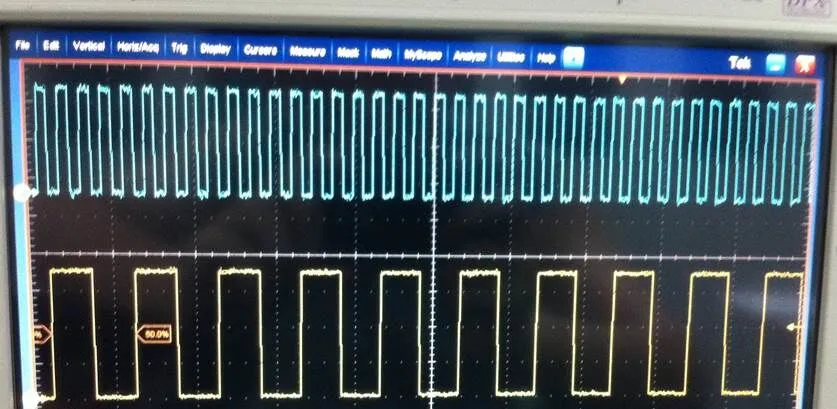

1)上电后,用PC机向控制FPGA发送0x03指令,对重构FPGA进行全局配置。配置结束后,示波器显示的波形如图5所示,蓝色的波形是重构FPGA的静态区域输出的波形,下面的黄色波形是动态区域输出的波形,可以看出静态区域和动态区域均能输出稳定的、不同频率的方波。

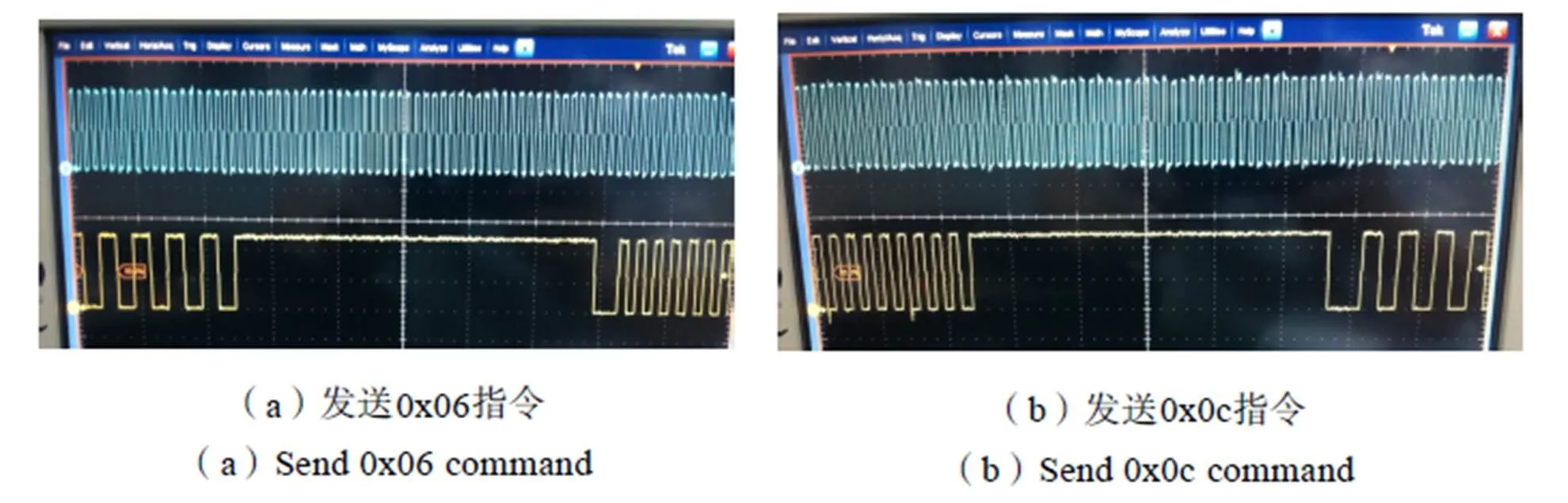

2)在上述输出稳定波形的基础上,用PC机向控制FPGA发送0x06指令,接到该指令后,控制FPGA向重构FPGA的重构区域中写入局部配置文件2,经过短暂的配置过程后,重构FPGA的重构区域将实现局部配置文件2的相应功能,此时,示波器输出的波形如图6(a)所示,从图中可以看出经过约560μs的短暂间隔后,FPGA的重构区域更新为新的功能,而在此过程中,静态区域输出的信号并没有中断。

3)为了测试,将再次用PC机向控制FPGA发送0x0c指令,接到该指令后,控制FPGA向重构FPGA的重构区域中写入局部配置文件1,经过短暂的配置过程后,重构FPGA的重构区域将实现局部配置文件1的相应功能。此时,示波器输出的波形如图6(b)所示,可以看出,同样经过约560μs的短暂间隔后,FPGA的重构区域更新为新的功能,输出新频率的方波,在此过程中,静态区域输出的信号并没有中断。

图5 全局配置后的波形

图6 局部配置后的波形

经过上述多组试验,果证明局部重构的时间约为560μs。主要原因是局部配置时,配置数据的长度较小,同时配置文件的头尾也较全局配置文件有所压缩。另外局部重构的时间还是会受到局部配置区域的尺寸和资源量影响,因此,在实际应用该技术时,宜根据具体需实现的功能需求,划分动态重构区域,保证在重构资源可满足设计需求的前提下,使重构区域尽量小。

3 结束语

本文使用FPGA的动态局部重配置技术,在FPGA里划分一个动态区域和静态区域,分别输出不同频率的波形,然后用另一块FPGA通过SelectMAP接口控制配置过程,最后用示波器对设计结果进行了验证。结果表明,在动态区域重新配置的过程中,静态区域输出的方波不受影响,功能不中断,并且在动态区域配置结束后,也能够正常输出新的波形。本文提出的设计方法验证了使用反熔丝逻辑芯片控制FPGA的动态局部重配置功能的可行性,在未来的航天器电子学设计中具有较好的应用前景。

[1] 黄伟, 刘涛, 王华, 等. SRAM型FPGA的单粒子效应及TMR设计加固[J]. 航天返回与遥感, 2012, 33(2): 49-53. HUANG Wei, LIU Tao, WANG Hua, et al. Single-event Effects on and TMR Radiation-harden of SRAM-based FPGA[J]. Spacecraft Recovery & Remote Sensing, 2012, 33(2): 49-53. (in Chinese)

[2] 薛建伟, 张杰, 关永. 基于EAPR流程的动态局部可重构实现[J]. 计算机工程, 2010, 36(23): 252-254. XUE Jianwei, ZHANG Jie, GUAN Yong. Implementation of Dynamic Partial Reconfiguration Based on EARP Flow[J]. Computer Engineering, 2010, 36(23): 252-254. (in Chinese)

[3] TODMAN T J, CONSTANTINIDES G A, WILTON S J E. et al. Reconfigurable Computing: Architectures and Design Methods[J]. IEEE Proceedings-Computers and Digital Techniques, 2005, 152(2): 193-207.

[4] CHAMBERLAIN R D, FRANKLIN M A, TYSON E J, et al. Auto-pipe: Streaming Applications on Architecturally Diverse Systems[J]. Computer, 2010, 43(3): 42-49.

[5] 徐新民, 乐莹, 尚丽娜. FPGA动态部分重构的研究及位流信息重构的实现[J]. 科技通报, 2008, 24(2): 235-240. XU Xinmin, LE Ying, SHANG Lina. The Research on Partially Dynamic Reconfiguration for FPGA and Its Implementation Based on Bitstream[J]. Bulletin of Science and Technology, 2008, 24(2): 235-240. (in Chinese)

[6] DEHON H, MARKOVSHY Y, CASPI E, et al. Stream Computation Organized for Reconfigurable Execution[J]. Reconfigurable Computing, 2008, 30(6): 203-218.

[7] 范斌, 常青. 基于DSP的FPGA动态重构系统研究与设计[J]. 信息与电子工程, 2010, 8(2): 123-127. FAN Bin, CHANG Qing. Dynamically Reconfigurable System of FPGA Based on DSP[J]. Information and Electronic Engineering, 2010, 8(2): 123-127. (in Chinese)

[8] 赵秋桂, 段青亚. FPGA动态局部可重构中基于TBUF总线宏设计[J]. 现代电子技术, 2009, 32(12): 22-24. ZHAO Qiugui, DUAN Qingya. Design of Bus Macro-based TBUF for FPGA Dynamic Reconfiguration[J]. Modern Electronics Technique, 2009, 32(12): 22-24. (in Chinese)

[9] CHOW P, SEO S O, ROSE J, et a1. The Design of an SRAM-based Field-programmable Gate Array-Part I:Architecture[J]. IEEE Transactions on VLSI Systems. 1999, 7(2): 191-197.

[10] WOLF W, JERRAYA A A, MARTIN G. Multiprocessor System-on-chip Technology[J]. IEEE Transactions on Computer-aided Design of Integrated Circuits and Systems, 2008, 27(10): 1701-1713.

[11] 冯晓静, 李曦, 王超, 等. 支持动态部分重构特性的异构多核体系结构[J]. 中国科学技术大学学报, 2014, 44(4): 310-316. FENG Xiaojing, LI Xi, WANG Chao, et al. A Multiprocessor Architecture Supporting Dynamic Partial Reconfiguration[J]. Journal of University of Science and Technology of China, 2014, 44(4): 310-316. (in Chinese)

[12] WATKINS M A, ALBONESI D H. ReMAP: A Reconfigurable Heterogeneous Multicore Architecture[C]//43rd Annual IEEE/ACM International Symposium on Microarchitecture. Atlanta, USA: IEEE Press, 2010: 497-508.

High Reliability FPGA Dynamic Partial Reconfiguration for Aerospace Application

YU Zhicheng1,2ZHUANG Shufeng3LIU Tao1WANG Yang1YANG Bingxin1

(1 Beijing Institute of Space Mechanics & Electricity, Beijing 100094, China) (2 Key Laboratory for Advanced Optical Remote Sensing Technology of Beijing, Beijing 100094, China) (3 Beijing Institute of Automatic Control Equipment, Beijing 100074, China)

In aerospace applications, the single event flipping of FPGA is an important factor affecting the function and lifetime of the spacecraft. At present, the time reloading method is applied to avoid the accumulation and influence of the single event effect in some of the aerospace products. However, the reloading process will lead to all FPGA logic interruptions, which greatly affects the sustainability of the spacecraft's functions. Therefore, a FPGA dynamic partial reconfiguration system for aerospace applications is proposed in this paper. The principle of FPGA dynamic partial reconfiguration technology and its prospect in space application are expounded firstly. Then the design process, the hardware circuit board architecture and the control software block diagram are described in detail. The function of the system is verified by the plate test, and the result tested by the oscilloscope demonstrates that the design of the system has high reliability. The FPGA dynamic partial reconfiguration technology proposed in this paper not only improves the reliability of the FPGA, but also ensures the sustainability of some key functions of the FPGA.

single event effect; field programmable gate array (FPGA); partial reconfiguration;reliability; space remote sensing

TN47

A

1009-8518(2019)03-0040-07

10.3969/j.issn.1009-8518.2019.03.006

于志成,男,1986年生,2012年获哈尔滨工业大学电子与信息工程专业硕士学位,现在中国空间技术研究院飞行器设计专业攻读博士学位,工程师。研究方向为航天遥感相机视频电子学。Email:tony_yzc@163.com。

2018-04-08

国家重大科技专项工程

(编辑:王丽霞)