三维功率MOSFET器件的热可靠性设计

林洁馨 杨发顺 马奎 丁召 傅兴华

摘 要: 基于三维集成技术的功率MOSFET器件,在发热量大和散热难的双重压力下,热可靠性设计凸显得尤为重要。文中采用硅通孔散热方式,在三维功率器件内嵌入大量的散热硅通孔,以降低芯片内热阻,疏导功率器件产生的热量,保证器件有源区结温低于极限安全结温,可有效提高芯片的热可靠性。以100 V,60 A的功率VDMOS器件为研究对象,以提高芯片的热可靠性为目的,合理设计和充分优化了三维功率MOSFET器件的版图和散热硅通孔的布局。基于多物理场分析软件开展了大量的热可靠性仿真分析工作,并流片验证了设计的正确性。

关键词: 热可靠性设计; MOSFET; 三维集成技术; 功率器件; 硅通孔布局; 散热; 热阻降低

中图分类号: TN626?34 文献标识码: A 文章编号: 1004?373X(2019)12?0081?05

Abstract: The thermal reliability design is of particular importance for the power MOSFET devices based on the 3D integration technology under the dual pressure of large heat generation and difficulty in heat dissipation. A great number of heat dissipation through?silicon viae are embedded in a 3D power device by using the through?silicon via heat dissipation pattern, so as to reduce the internal thermal resistance of a chip, dissipate the heat generated by the power device, ensure the junction temperature in the active region of the device is lower than the extreme security junction temperature, and effectively improve the thermal reliability of the chip. Taking the 100 V 60 A power VDMOS device as the research object, the layout of the 3D power MOSFET device and distribution of heat dissipation through?silicon viae are reasonably designed and fully optimized, so as to improve the thermal reliability of its chip. A lot of simulation and analysis work of thermal reliability was done on the basis of the multi?physics field analysis software. The correctness of the design was verified by the tape?out.

Keywords: thermal reliability design; MOSFET; 3D integration technology; power device; through?silicon via layout; heat dissipation; thermal resistance reduction

0 引 言

功率半导体器件作为功率(电力电子)系统的关键元件,主要为负载提供大功率,它通常工作在高压、大电流条件下[1],因此自身也会有很大的功率损耗,这些损耗的功率以热量的形式散发出去。目前,高可靠功率MOSFET器件的制作工艺仍然以平面集成工艺为主,但随着集成电路特征尺寸的缩小,传统二维集成技术导致的信号延迟、功耗增加等一系列问题日益突出。集成电路的发展已进入后摩尔时代,三维集成技术是业界公认的超越摩尔主流技术之一[2],它是一种系统级架构方法[3],采用在垂直方向上堆叠多个器件、芯片或模块,在保证芯片面积不变的前提下提高芯片上的器件数目。为了增大功率容量,可将功率器件制作在多个堆叠层上,但三维功率集成芯片与二维平面功率芯片相比,在单位体积内的功耗密度更高,层间低热导率介质层的存在也导致了散热问题的恶化,如果不能及时将热量散发出去,三维芯片层间的温度梯度急剧上升,温度升高会影响功率器件的电学特性,如:迁移率下降、载流子速度上升、结泄漏电流和导通电阻增大等,导致器件性能的降低;若温度过高,还会引起绝缘层的击穿、多晶硅或金属连线的烧毁、钝化层的破坏等现象,导致功率器件失效[4]。因此,在发热量大和散热难的双重压力下,热可靠性设计是三维功率集成设计的重中之重。本文采用在三维功率MOSFET器件的安全位置嵌入大量的硅通孔的散热方式,降低芯片的内热阻,疏导功率MOS器件内部产生的热量。以一款100 V,60 A的功率VDMOS器件为研究对象,从提高热可靠性出发,对三维VDMOS器件的结构、布局和版图进行了设计,并通过大量的Comsol多物理场仿真结果和流片测试结果验证了该设计的正确性。

1 三维功率MOSFET器件的热可靠设计

1.1 三维功率MOSFET器件的结构设计

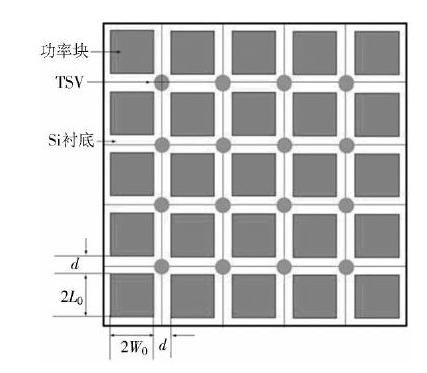

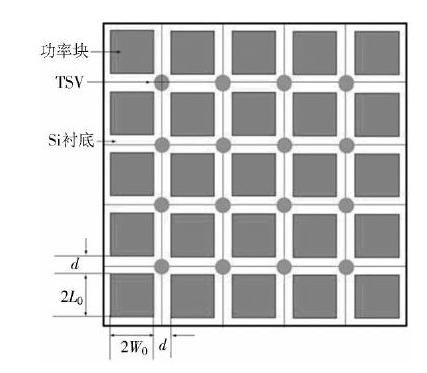

为了提高功率容量和集成度,把高压大功率器件制作在两片或两片以上的平面芯片上,高压大功率器件的功率损耗大,产生的热量多,可把它放在热沉或散热器之上。对于功率MOS器件来说,器件是由数万个元胞并联而成,可将并联元胞划分成多组重复单元,每一单元称为一个功率块,每一个功率块可以看成是一个功率器件,故每个功率块周围都含有防止边缘击穿的终端设计,为了将功率块产生的热量快速传导到散热器,在每个功率块周围安全位置插入多个散热硅通孔,三维功率MOSFET器件的结构剖面如图1所示,顶视如图2所示。

图1 三维功率MOSFET器件结构剖面图

图2 三维功率MOSFET器件结构顶视图

1.2 功率块与散热硅通孔间安全距离的设计

在功率块周围制作散热硅通孔时必须要考虑TSV的工艺残余应力和热应力[5]。工艺残余应力主要是来自于电镀时铜晶粒生长演变过程和电镀结束后的退火温度使铜发生塑性变形引起的,可以通过调整电镀工艺参数和退火温度、时间来改善。熱应力是由于TSV中填充金属材料(尤其铜)和硅的热膨胀系数(CTE)差异太大,在工艺温度和工作温度升高或降低时,由于材料间CTE失配在周围的硅衬底引入的应力。TSV的热应力导致硅衬底应变,造成衬底碎裂,TSV铜柱凸出、键合剥离等可靠性问题[6]。

文献[7]通过大量的实验数据证实,100 MPa的应力可以让MOSFET器件的载流子迁移率变化7%,严重影响硅器件的性能,导致在TSV周围无法布置器件。因此,为了表示TSV与器件的安全距离,用阻止区(Keep?out Zone,KOZ)来表征热应力特性。由于TSV热应力过大使周围不能制作器件的区域[8],越过KOZ的区域可以安全制作器件,称为安全工作区。文献[9]在考虑硅各向异性时对沿着(100)晶向和(110)晶向的P沟道MOSFET和N沟道MOSFET阵列的载流子迁移率进行了评估,通过有限元方法给出KOZ可以用载流子迁移率变化率为5%进行评判的标准,KOZ可定义为载流子迁移率变化率超过5%的区域。文献[10]提出TSV热应力与载流子迁移率变化率的关系,可以用式(1)表示。

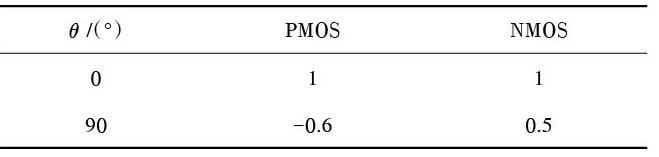

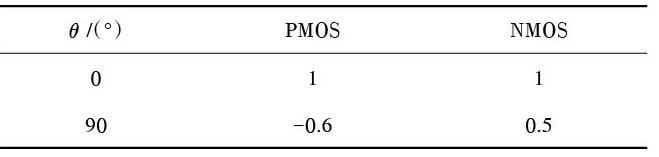

式中:[Δμμ]为载流子迁移率变化量;[Π]为器件的压阻系数;[σrr]为径向热应力;[βθ]为取向因子,如表1所示[11]。一般情况下,N沟道MOSFET和P沟道MOSFET的压阻系数分别为-31×10-11 Pa-1和71.8×10-11 Pa-1。

表1 取向因子

本文用多物理场仿真软件Comsol对干法刻蚀形成的圆柱形散热通孔结构的热应力进行了仿真分析,主要考虑400 ℃下的冯米斯(Von Mises Stress)热应力分布情况,并根据载流子迁移率变化量5%的KOZ标准和式(1)在两个最坏的的方向(θ=0°和θ=90°)估算了功率块与散热硅通孔间的安全距离。表2是散热硅通孔深度为200 μm,直径分别为10 μm,20 μm,30 μm,40 μm,50 μm和60 μm时,周围能安全放置功率器件的最小距离。

表2 考虑各向异性时的NMOS和PMOS的KOZ

从表2可见,圆柱形TTSV周围产生的热应力对PMOS器件更敏感,PMOS器件的KOZ比NMOS器件的大;TTSV直径越大,KOZ越大。设计中仅一味追求散热效果使用大直径的TTSV,不仅增加工艺的难度,也会造成芯片面积的增大。

1.3 三维功率MOSFET器件的布局设计

功率MOSFET器件可分割在两个或两个以上的平面芯片层,芯片内部用TTSV进行散热,底层芯片可与铜散热器直接键合或通过介质层后再键合。为了避免平面芯片上存在温度梯度,产生附加的温度漂移,以芯片中心线为对称轴,把功率块放在对称轴的两侧,功率MOS器件的源极和栅极放置在顶层芯片的上表面,功率MOS器件的漏极由底层芯片的背面引出,各层芯片上的栅、源、漏极金属互连通过电信号TSV完成,为了不增加额外的制版和工艺复杂度,信号TSV与散热TSV的大小和制作工艺可以相同。

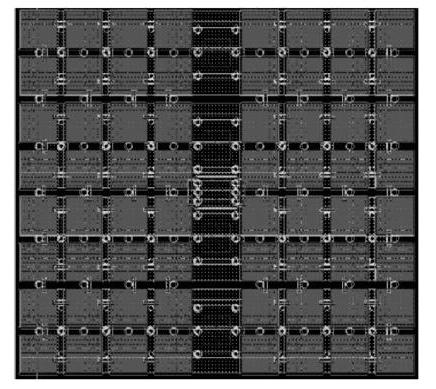

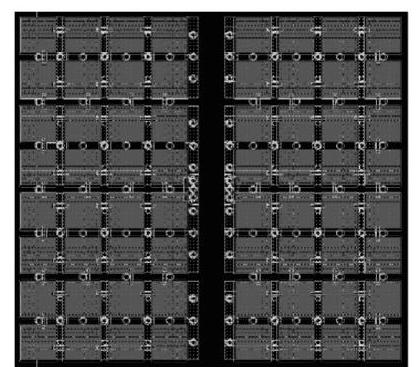

本文以100 V,60 A的三维功率VDMOS器件为研究对象,将VDMOS器件分割在两层芯片上。每层VDMOS器件输出电流为30 A,最大直流功率损耗约为130 W,由大约395 000个24 μm×1 μm的仿真元胞并联组合,若设每个功率块尺寸为400 μm×400 μm,则每个VDMOS平面芯片层可分成64个功率块。三维功率VDMOS器件的两层芯片版图如图3和图4所示。

圖3 三维功率VDMOS器件顶层芯片版图

图4 三维功率VDMOS器件底层芯片版图

2 三维功率MOSFET器件的热可靠性验证

2.1 三维功率VDMOS器件的热仿真验证

设VDMOS器件的最高工作结温为420 K,散热底座温度为300 K,则芯片极限温升120 K,若平均分配两层芯片的温升,则单层温升为60 K。若60 A三维功率N沟道VDMOS器件制作在两层芯片上,每层VDMOS器件输出电流30 A,若VDMOS器件的目标导通电阻为140 mΩ,则最大直流功率损耗约为130 W,每层由大约395 000个24 μm×1 μm的仿真元胞并联组合,若设每个功率块尺寸为400 μm×400 μm,则每个VDMOS平面芯片层可分成64个功率块。若采用Ankur Jain等人的热计算方法[12],即本层芯片的温升等于上层热负载加上本层热负载之和与本层热阻的乘积。则顶层每个功率块的热负载为2.04 W,底层每个功率块的热负载为4.08 W,根据温升极限,顶层热阻小于等于29 K/W,底层热阻小于等于14.7 K/W。

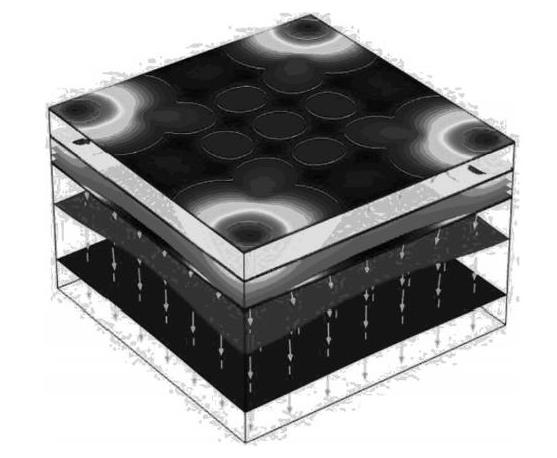

本文采用多物理场仿真软件COMSOL建立三维功率MOSFET器件的热仿真模型,模型如图5所示。

图5 三维功率MOSFET器件热模型

热模型中三维功率MOSFET器件分别制作在两层芯片上,每层芯片上功率块和TTSV均匀分布于硅衬底,功率块数与TTSV数相等,功率块之间的间距由TTSV的直径大小和TTSV的KOZ大小进行调整,底层芯片与铜散热器通过直接键合方式连接。

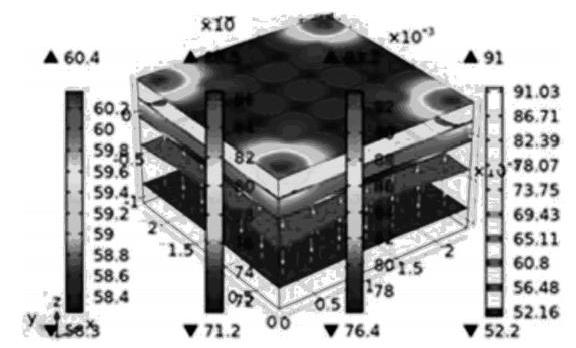

热仿真实验中,设TTSV的直径为30 μm,深度为200 μm,TTSV内绝缘介质层厚度为0.2 μm,介质层热导率为1.5 W/(m·K)。TTSV中铜的热导率为380 W/(m·K),上、下两个芯片层间的键合层厚度为10 μm,键合层热导率为1.5 W/(m·K),功率块与功率块间距可设为60 μm。Comsol仿真结果如图6所示,上层芯片最高温度为93.2 ℃,下层芯片最高温度86.5 ℃,两层芯片的温升共39.1 ℃。该结果均能满足芯片安全工作。

图6 三维功率VDMOS器件热仿真结果

2.2 三维功率VDMOS器件流片验证

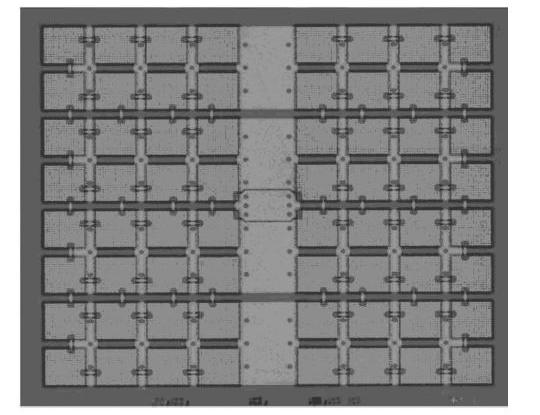

在三维功率VDMOS版图设计时,每层芯片布置了64个大小为400 μm×400 μm的功率块,在功率块间均匀嵌入了70个直径为30 μm的TTSV,每层芯片中还布置了56个互连各层功率块漏极的信号TSV、48个互连各层功率块源极的信号TSV和6个互连各层功率块栅极的信号TSV,它们既作为信号互连通道,也可以散发热量。实验基于4 μm MOS工艺设计并制作了三维功率VDMOS器件中的各层芯片,每层芯片均采用单层金属布线,共14次光刻,15块光刻版。其中每层上的VDMOS器件制作使用8次光刻,9块光刻版;实现芯片三维堆叠制作使用6次光刻,6块光刻版。图7和图8分别为顶层和底层芯片的显微镜图片。

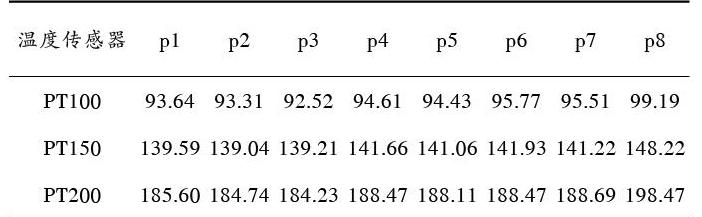

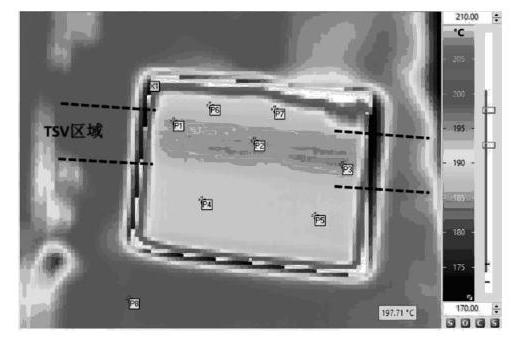

实验中采用红外热像仪设备测试了芯片上TTSV的热分布,共选择了8个测温点,其中p1~p7测温点位于样品放置区,包含TSV区域和非TSV区域,p8测温点为放置样品的铜板温度测试点。

表3为铜板发射率和样品发射率通过PT100,PT150和PT200温度传感器进行标定的结果。从各个测温点的标定温度可见,位于TSV区域的测温点p1,p2和p3温度下降最快,可见TSV中的金属铜的传热最快,如图9所示。

图7 顶层芯片显微镜照片

图8 底层芯片显微镜照片

表3 TSV热分布分析表

图9 样品的温度分布(200 ℃)

3 结 语

本文将未来主流的三维集成技术应用于功率系统,在发热量大和散热难的双重压力下,重点对提供大功率输出的高压大电流功率器件进行热可靠性设计,采用在芯片内嵌入大量的硅通孔的散热方式来疏导功率器件产生的热量,保证器件有源区结温低于极限安全结温。以功率VDMOS器件为研究对象,以提高芯片的热可靠性为目的,对三维功率MOSFET器件的结构、布局及版图进行设计,并通过多物理场仿真软件Comsol和实验流片验证了该设计的正确性,该设计方法对三维功率系统的热管理具有一定的指导意义。

参考文献

[1] NEAMEN D A. Semiconductor physics and devices [M]. Beijing: Electronic Industry Press, 2010.

[2] LAU J H. Evolution and outlook of TSV and 3D IC/Si integration [C]// Proceedings of 2010 12th Electronics Packaging Technology Conference. Singapore: IEEE, 2011: 560?570.

[3] AKASAKA Y, NISHIMURA T. Concept and basic technologies for 3?D IC structure [C]// Proceedings of 1986 International Electron Devices Meeting. Los Angeles: IEEE, 1986: 488?491.

[4] 王喆垚.三维集成技术[M].北京:清华大学出版社,2014.

WANG Zheyao. Three?dimensional integration technology [M]. Beijing: Tsinghua University Press, 2014.

[5] 秦飞,王珺,万里兮,等.TSV结构热机械可靠性研究综述[J].半导体技术,2012,37(11):825?831.

QIN Fei, WANG Jun, WAN Lixi, et al. Review on the thermal mechanical reliability of TSV structures [J]. Semiconductor technology, 2012, 37(11): 825?831.

[6] 刘荡.硅通孔热应力对于器件性能的影响的研究[D].西安:西安电子科技大学,2015.

LIU Dang. Research on the impacts of TSV induced thermal stress on device performance [D]. Xian: Xidian University, 2015.

[7] THOMPSON S E, SUN G, CHOI Y S, et al. Uniaxial?process?induced strained?Si: extending the CMOS roadmap [J]. IEEE transactions on electron devices, 2006, 53(5): 1010?1020.

[8] VANDEVELDE B, OKORO C, GONZALEZ M, et al. Thermo?mechanics of 3D?wafer level and 3D stacked IC packaging technologies [C]// Proceedings of International Conference on Thermal, Mechanical and Multi?Physics Simulation and Experiments in Microelectronics and Micro?Systems. Freiburg im Breisgau: IEEE, 2008: 1?7.

[9] RYU S K, LU K H, JIANG T, et al. Effect of thermal stresses on carrier mobility and keep?out zone around through?silicon vias for 3?D integration [J]. IEEE transactions on device & materials reliability, 2012, 12(2): 255?262.

[10] KUO C Y, SHIH C J, LU Y C, et al. Testing of TSV?induced small delay faults for 3?D integrated circuits [J]. IEEE transactions on very large scale integration systems, 2014, 22(3): 667?674.

[11] 王凤娟.基于硅通孔(TSV)的三维集成电路(3D IC)关键特性分析[D].西安:西安电子科技大学,2014.

WANG Fengjuan. Analysis of key characteristics of through?silicon?via (TSV) based three?dimensional integrated circuits (3D ICs) [D]. Xian: Xidian University, 2014.

[12] JAIN A, JONES R E, CHATTERJEE R, et al. Analytical and numerical modeling of the thermal performance of three?dimensional integrated circuits [J]. IEEE transactions on components and packaging technologies, 2010, 33(1): 56?63.