并联交错在数字功率因数校正中的应用

张明栋 沈伊慧 黄艳军 王杰

摘要:本文给出了一种数字控制的单相功率因数校正(PFC)方案。主电路采用并联交错拓扑,减小了系统输入电流纹波。控制系统采用数字算法构建PI调节器。为提高系统控制精度,考虑了数字延迟和采样保持等过程。用一款样机验证了设计结果,验证了设计的正确性。

关键词:数字控制;功率因数校正;PI

中图分类号:TP391.41 文献标识码:A 文章编号:1007-9416(2019)03-0060-01

为提高电能质量,目前用电设备输入侧广泛采用功率因数校正(Power Factor Correction,简称PFC)技术。模拟电路实现的PFC技术简单,成本较低,但是存在一定的缺陷,即控制电路受主回路参数影响较大,适应范围小。数字电路实现PFC相对而言较为复杂且成本较高,但随着数字控制技术的不断发展,数字控制PFC技术的应用日臻成熟。目前广泛采用的数字控制模型,针对控制系统的PI补偿器参数整定还是基于主电路的小信号模型,缺乏对控制系统本身采样保持和计算延迟等过程的考虑。本文建立了系统采样保持和计算延迟的数学模型,并利用Z变换在离散域对数字PI调节器进行参数整定,取得了比较精确的控制模型。最后,通过一款样机验证了模型的准确性和设计的可行性。

1 并联交错拓扑及小信号模型

1.1 并联交错PFC

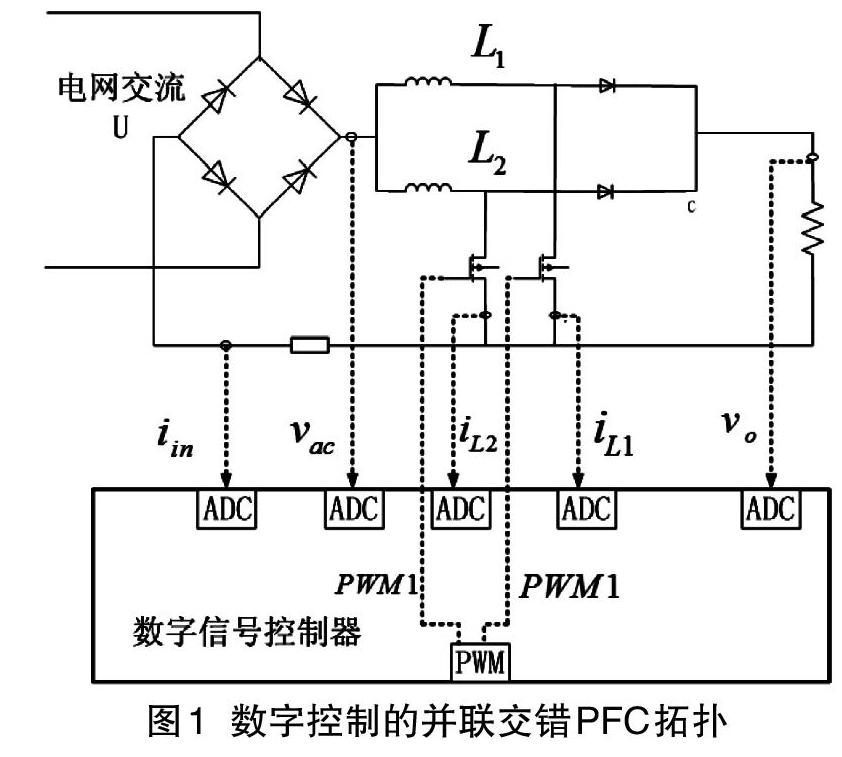

图1所示是本系统所采用的并联交错主电路及数字控制器的原理。

主电路采用并联交错(Interleaved)拓扑。并联交错将N(N≥2)路Boost电路并联,各路开关管驱动波形相位彼此相差。采用并联交错可以显著减小储能电感体积和输入电流纹波。此外,并联交错能够在相同开关频率的情况下显著提高转换效率[1]。控制回路由单片MCU实现模数采集和PWM生成,减小了电路体积并有效提高了控制算法的灵活性。下面分别对主回路和控制回路进行数字化建模。

1.2 主电路建模

Boost电路的小信号模型如图2[2]:

(1)电流环传递函数。电流控制环的输入是电感电流,输出为PWM占空比,传递函数的基本形式是电流小信号与占空比小信号的比值。电流环的交流小信号传递函数为: (1)

(2)电压环 传递函数: (2)

其中, (3)

(3)采样-保持(S&H)延迟。采样保持过程可以用零阶保持器来描述[3]。当信号在时刻被采样并保持一个时间后输出转换结果,输出如下:

(4)

这里u(t)是单位阶跃函数。对公式4进行拉普拉斯变换,得到:

(5)

(4)算法执行延迟。用表示算法执行所带来的控制环延迟,称为计算延迟。离散系统的计算延迟可利用单位冲击响应来描述: (6)

因此计算延迟的传递函数如下: (7)

2 控制系统参数整定

控制环包括电压外环和电流内环。电压外环的作用是按预设给出稳定的输出电压,保证电压不随负载变化而产生突变,电流内环的作用是使电流跟踪参考信号,即同相的交流正弦信号。为保证电感电流负载平衡,添加了电流平衡补偿器。记为积分饱和修正系数,表达式如下:

(8)

上式中的,是待整定的PI控制器系数,根据自动控制原理中有关系统稳定性补偿的方法在Z域加以确定,采用MATLAB求解,此处不再具体展开。

3 系统的实验验证

设计了一款400W样机系统,基于上述模型计算得到的控制系数编写控制算法,在满载时输入电压及校正后的输入电流波形如3图。实际结果表明,控制系统参数整定合理,功率因數可达到0.99。

4 结语

采用数字控制的并联交错PFC转换器,控制环采用小信号建模,主回路通过相差180°相位的PWM驱动波形及均流环节,能够很好的达到功率因数校正的效果,满载功率因数可达0.99。

参考文献

[1] Balogh L.Power factor correction with interleaved boost converters in continuous-inductor-current mode[C].San Diego: Applied power electronics conference and exposition,1993:168-175.

[2] 徐德鸿.电力电子系统建模及控制[M].北京:机械工业出版社,2005.

[3] Chen Fu-Zen,Dragan M.Digital control for efficiency improvements in interleaved boost PFC rectifiers[C]. Palm Springs:Applied power electronics conference and exposition,2010:21-25..

Application of interleaving topology in PFC Based on Digital Control

ZHANG Ming-dong,SHEN Yi-hui,HUANG Yan-jun,WANG Jie

(Shanghai Areospace Electronic Technology Institute,Shanghai 201109)

Abstract:This paper presents a digital controlled single-phase power factor correction (PFC) design. The interleaving topology is applied to the main circuit to reduce the input current ripple. A digital algorithm is introduced to construct a PI regulator for the control system. To determine the parameters of the PI controllers, In order to improve the control precision, both the digital delay and sample & hold process are take into consideration. To verify the correctness of the design, a prototype is given.

Key words:digital control; power factor correction; PI