应用于AMOLED源极驱动的高精度DAC设计

孟 宇,尹勇生,宇跃峰,邓红辉,贾 晨

(1.合肥工业大学 微电子设计研究所,安徽 合肥 230009;2.深圳清华大学研究院,广东 深圳 518057)

1 引 言

随着各类电子显示设备的日益发展,AMOLED面板相对于液晶显示面板因其能够自主发光、响应速度更快、宽广的视角、器件更薄等优势被广泛应用于手机、手表等各类显示设备上。由于AMOLED的像素驱动电路在驱动精度和发光效率上都有很好的优势,对应的像素电路的驱动芯片设计已成为大规模数模混合系统设计领域的研究热点[1]。源极驱动电路是AMOLED面板驱动芯片的重要组成部分,其功能是将携带有图像信息的RGB数据转换成可以快速、精确建立在面板电容像素负载上的灰阶电压[2]。

由于显示设备亮度与输入电压的非线性关系以及人眼对于亮度变化的非线性感官,GAMMA曲线校正是源极驱动电路的必要功能。目前,业界GAMMA校正实现方式的研究主要集中在输入图像数据的转换和产生灰阶电压的DAC结构这两方面。采用非线性DAC结构实现GAMMA曲线的校正不需要对图像显示数据进行转换,但实现非线性DAC则需要大量不同阻值的电阻,这不仅占用大量的芯片面积,同时,采用不同阻值的电阻其匹配性能也相对较差。不仅如此,非线性DAC体系结构采用对电压分段的方式来拟合GAMMA曲线,实现的灰阶电压精度受限于图像显示数据的位宽,其精度较低。采用非线性数据结合线性DAC结构实现的GAMMA曲线校正方法因其匹配性好、精度高、面积小、成本低、灵活性强的特点成为更受欢迎的方案[3-5]。而屏幕所需的灰阶-电压曲线一般为不规则的非线性曲线,线性DAC的输出曲线与灰阶-电压曲线形状通常有较大差距,图像数据在选择线性DAC上的电压时就会产生较大的误差,对线性DAC进行输出曲线形状进行调节可以有效的减小这种误差,提高灰阶电压的精度。

本文基于非线性数据结合线性DAC结构实现GAMMA校正的方法,对传统的线性10 bit DAC结构进行改进,通过在第一级6 bit DAC结构前增加一个斜率调节单元,对DAC输出曲线斜率进行调节,实现具有3段不同斜率线段的DAC曲线来拟合显示屏所需的灰阶-电压曲线,经图像数据选择后,相对于传统的线性DAC结构可以实现更高的灰阶电压精度。

2 本文高精度DAC设计

2.1 DAC整体结构

源极驱动的功能简单来说就是实现图像数据到灰阶电压的转换,可以理解为一个数模转换器。最初始的实现方法是采用非线性的DAC结构,但因其灰阶电压精度受图像数据位宽限制以及其它的一些缺点,这种实现方式逐渐被线性DAC结构替代。

实现线性DAC的方法有多种,常用的是选择电阻串分压实现。若仅采用一级的电阻串结构来实现10 bit的线性DAC,则需要1 024个电阻,这会占用大量的芯片面积。因此,通常10 bit的线性DAC都采用两级插值的结构来实现,文献[4]中采用的两级DAC结构,每级都采用5 bit的电阻串来实现分压功能,不仅节省了芯片面积,且灰阶电压精度可以达到10 bit[4];文献[6]中采用高6 bit的GAMMA校正电阻串DAC结合低2 bit的多项式插值子DAC共同实现8 bit线性DAC,灰阶电压精度为8 bit[6];文献[7-8]中都使用了一种尾电流源可编程单位增益运放起到第二级线性DAC的作用,结合第一级7 bit电阻串共同实现10 bit线性DAC,进一步节省了芯片面积[7-9]。图1为文献[8]中采用的线性DAC结构,也是传统的10 bit线性DAC体系结构。这种方式实现的灰阶电压精度达到了10 bit,且芯片面积代价较小。但实现的线性DAC输出曲线相较面板所需的灰阶电压曲线偏差较大,本文通过减小这种偏差来进一步提高灰阶电压的精度。

图1 传统的10-bit DAC结构Fig.1 Structure of conventional 10-bit DAC

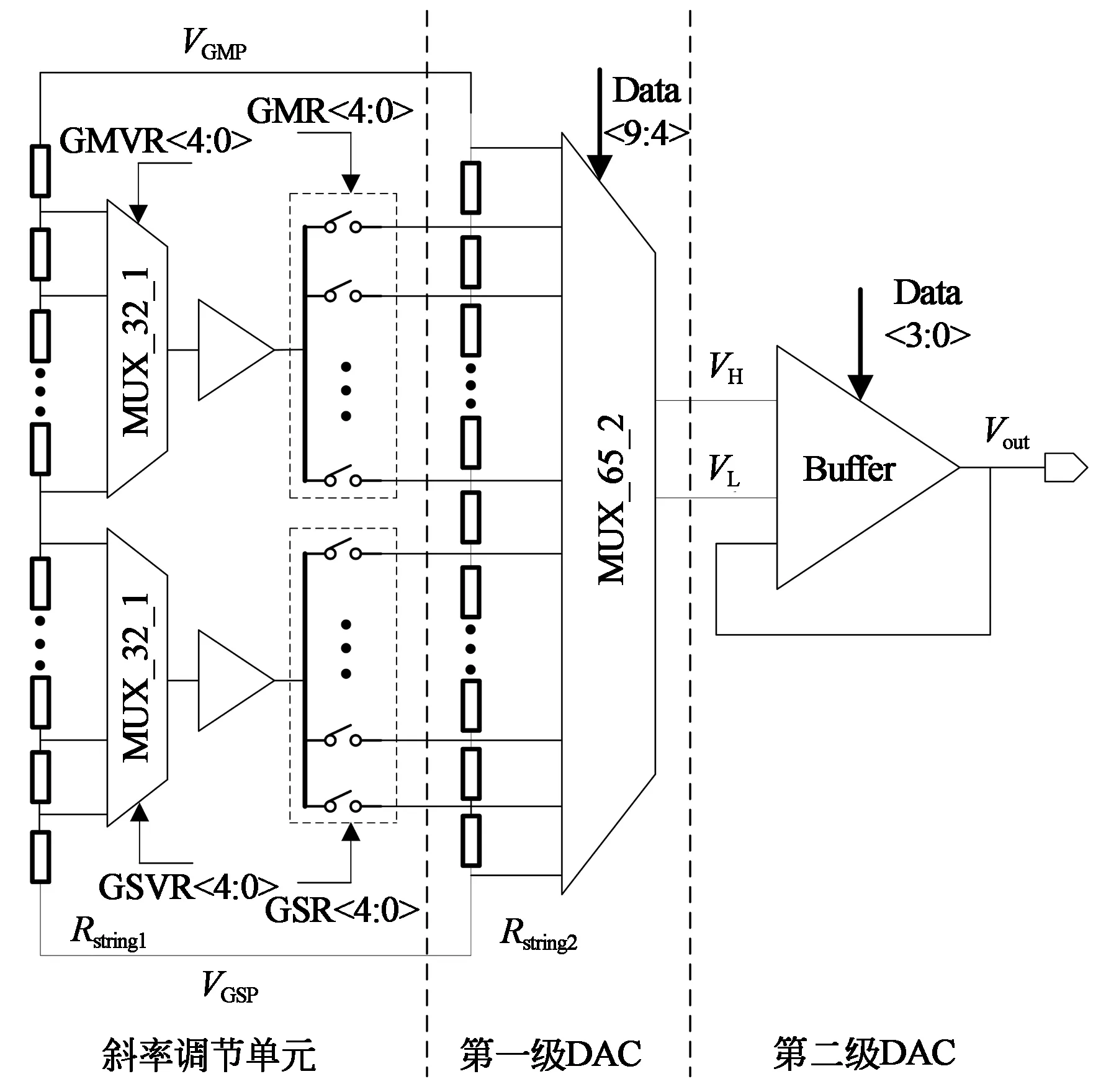

图2 提出的斜率可编程DAC结构Fig.2 Structure of proposed slope programmable DAC

本文提出的斜率可编程DAC结构如图2所示。综合芯片面积,匹配性能及设计复杂度考虑,本文设计采用6 bit GAMMA校正电阻串DAC结合4 bit插值运放实现10 bit DAC结构。10 bit DAC由两级线性 DAC构成,第一级通过64个阻值相等的电阻分压结合一个65选2多路选择器构成6 bit DAC结构,由高6 bit的图像数据Data<9∶4>选出第一级DAC的输出电压VH和VL;第二级DAC则采用尾电流源4 bit可编程的插值输出缓冲器来实现。斜率调节单元由一串包含64个等值电阻的斜率调节电阻串Rstring1及与两个斜率调节点对应的多路选择器构成,VGMP和VGSP分别为最高和最低基准电压,由基准模块提供,Data<9∶0>为8 bit的图像显示数据经非线性转换后得到的10 bit图像数据,用来对10 bit的DAC进行选择得到最终的灰阶电压。斜率调节单元产生的两个斜率调节点插入到第一级6 bit DAC的电阻之间来调节DAC的斜率,最终得到具有3段不同斜率线段的DAC输出曲线。DAC输出曲线的斜率可根据显示屏所需的灰阶-电压曲线进行灵活调节,使DAC输出曲线拟合显示屏的灰阶-电压曲线达到更高的灰阶电压精度。

2.2 第一级斜率可编程DAC设计

图2中的斜率调节单元和第一级DAC共同构成了第一级斜率可编程DAC结构。灰阶电阻串Rstring2和65选2多路选择器为第一级的6 bit DAC,Rstring1为斜率调节电阻串,寄存器GMVR<4∶0>和GMR<4∶0>共同控制第一个斜率调节点的产生,寄存器GSVR<4∶0>和GSR<4∶0>共同控制第二个斜率调节点的产生,通过两对寄存器的调节可以实现DAC斜率的灵活调节。

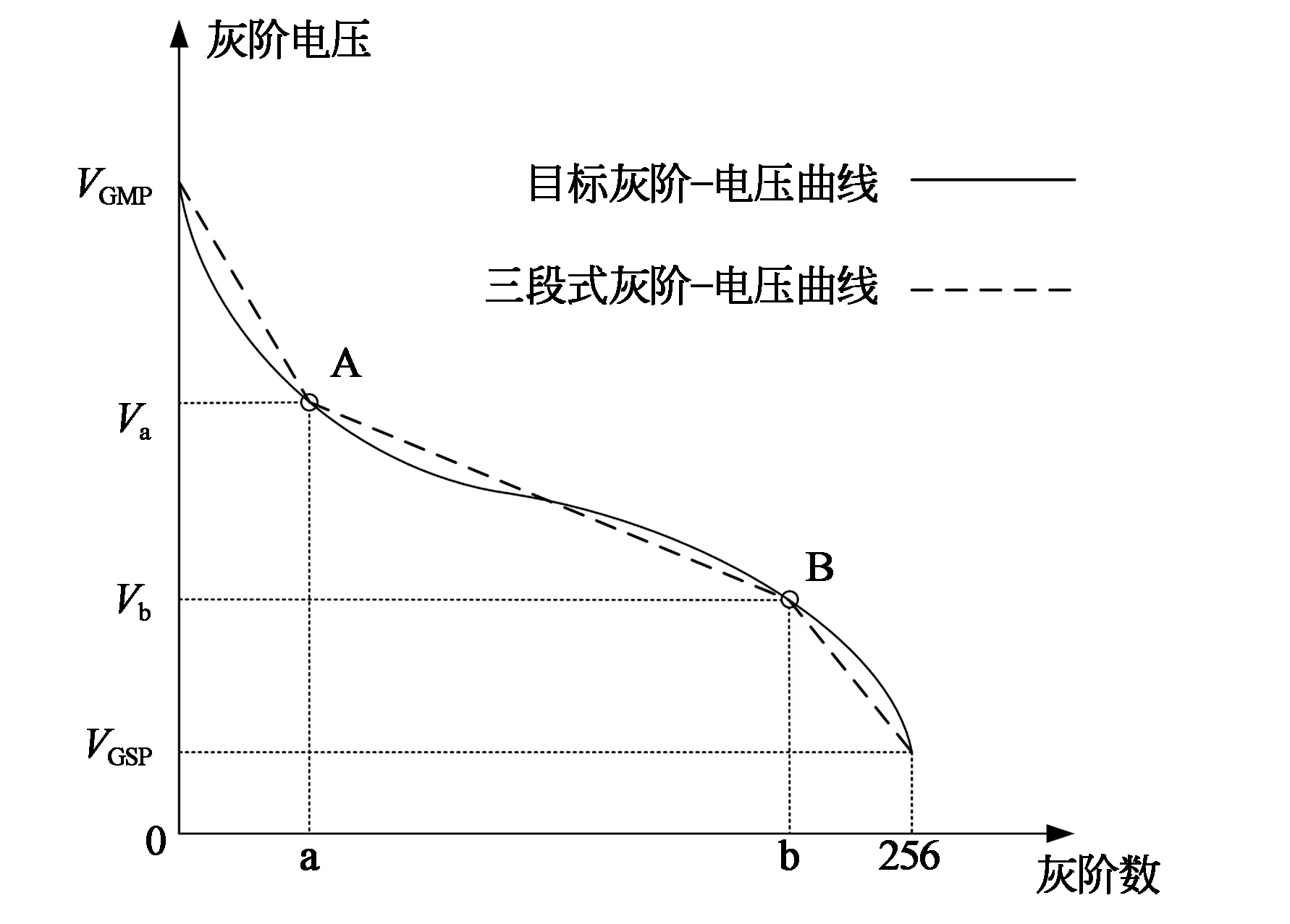

进行DAC斜率调节时,首先要将显示屏所需的灰阶-电压曲线分为3段斜率不同的线段来确定曲线的基本趋势,两个分界点依据显示屏的灰阶-电压曲线来确定。如图3所示,为保证三段式的灰阶-电压曲线最接近目标灰阶-电压曲线,选取A和B两点作为分界点,对应的灰阶数和灰阶电压分别为a、Va和b、Vb。这样,我们可以得到一条与实际所需的灰阶-电压曲线形状最接近的三段式灰阶-电压曲线。

图3 斜率调节点的确定Fig.3 Determination of the slope adjustment point

确定了三段式灰阶-电压曲线后,斜率调节的目标就是实现最接近三段式灰阶-电压曲线形状的DAC输出曲线,三段式DAC输出曲线是在线性DAC的基础上通过产生两个斜率调节点来实现的。本文通过斜率调节单元产生的两个斜率调节点来调节DAC的斜率。

由于斜率调节电阻串DAC仅为6 bit,步长较大,不一定存在与Va和Vb完全一样的电压值,所以在斜率调节电阻串Rstring1上选取与Va和Vb最为接近的两个电压Va’和Vb’。本文通过斜率调节寄存器GMVR<4∶0>及GSVR<4∶0>的值来选取两个斜率调节点的电压值,同时,通过控制寄存器GMR<4∶0>及GSR<4∶0>的值来控制斜率调节插入点的位置。如图4所示,斜率调节点A’的电压值Va’由寄存器GMVR<4∶0>控制,插入到灰阶电阻串Rstring2的位置由寄存器GMR<4:0>控制;斜率调节点B’的电压值Vb’由寄存器GSVR<4∶0>控制,插入到灰阶电阻串Rstring2的位置由寄存器GSR<4∶0>控制。通过控制寄存器GMR<4∶0>和GSR<4:0>值的设定可以调节a’和b’的位置,从而保证实现的DAC曲线形状最为接近三段式的灰阶-电压曲线。

图4 DAC斜率调节示意图Fig.4 Diagram of DAC slope adjustment

相对于传统的线性DAC实现GAMMA校正的方法,本文实现的DAC输出曲线可以通过斜率调节点寄存器的灵活控制使其更接近于显示设备的灰阶-电压曲线,转换后的图像数据对DAC输出电压进行选择后可以达到更高的灰阶电压精度。

2.3 第二级电流源插值缓冲器设计

本文在设计DAC时,使用了尾电流源可编程插值运算放大器来实现第二级线性DAC的功能,插值运放作为输出缓冲器驱动后级像素电路的同时也节省了第二级DAC的面积。图5是本文提出的基于尾电流源可编程的带有4 bit DAC功能的插值缓冲器简化原理图。

图5 带有4 bit DAC功能的输出缓冲器Fig.5 Output buffer with 4 bit sub-DAC

本设计是采用4 bit图像数据控制两对差分对尾电流源的比例来实现第二级线性DAC的功能。第一级DAC结构中65选2多路选择器的输出电压(VH和VL)分别连接到运放的两个差分对输入管M1和M4的栅端,同时输出Vout接回到M2和M3的栅端形成负反馈闭环回路构成单位增益缓冲器。两对差分输入对管都被偏置在亚阈值区,差分对等效跨导与输出Vout的关系可以表示为:

(1)

(2)

对于处于亚阈值区的MOS管,其跨导gm和漏源电流ID的关系为可以表示为:

(3)

式中,ζ>1,是一个非理想因子,VT=kT/q。

低4 bit的图像数据Data<3∶0>(记为D3,D2,D1,D0)可以控制两个差分对的尾电流之比,4 bit的图像数据分别控制8I,4I,2I,1I比例的电流,且设计两个差分对尾电流IBH与IBL之和固定为16I,设IBH=KI,则IBL=(16-K)I,因此,输出电压可以表示为:

(4)

这里,K的取值范围为1,2,3…16,分别对应4 bit图像数据从1111到0000变化。这样,第二级DAC可以根据图像数据的变化,在第一级DAC的输出电压VH和VL之间进行插值,本文设计的第二级4 bit DAC可以根据低4bit的图像数据从0000到1111变化选取出16个不同的电压值。

本设计运放的尾电流源采用电流镜结构实现,通过尾电流源晶体管尺寸的比例关系精确复制基准电流,确保由4 bit图像数据D3,D2,D1,D0分别控制的8I,4I,2I,1I电流的精准比例关系,进而保证输出缓冲器插值的精确度。

图6 提出的插值运算放大器结构Fig.6 Structure of proposed interpolation OPA

图6是本文提出的插值运算放大器。运放采用轨到轨输入级结构,保证满足大范围的输入电压变化;带有悬浮电流源的class_AB输出级结构,保证较大的输出摆幅的同时又具有较小的静态偏置电流;同时,运用共源共栅Miller补偿结构[10],只需要很小的Miller补偿电容和静态电流,就可以高速、稳定的驱动大电容负载。

3 仿真结果

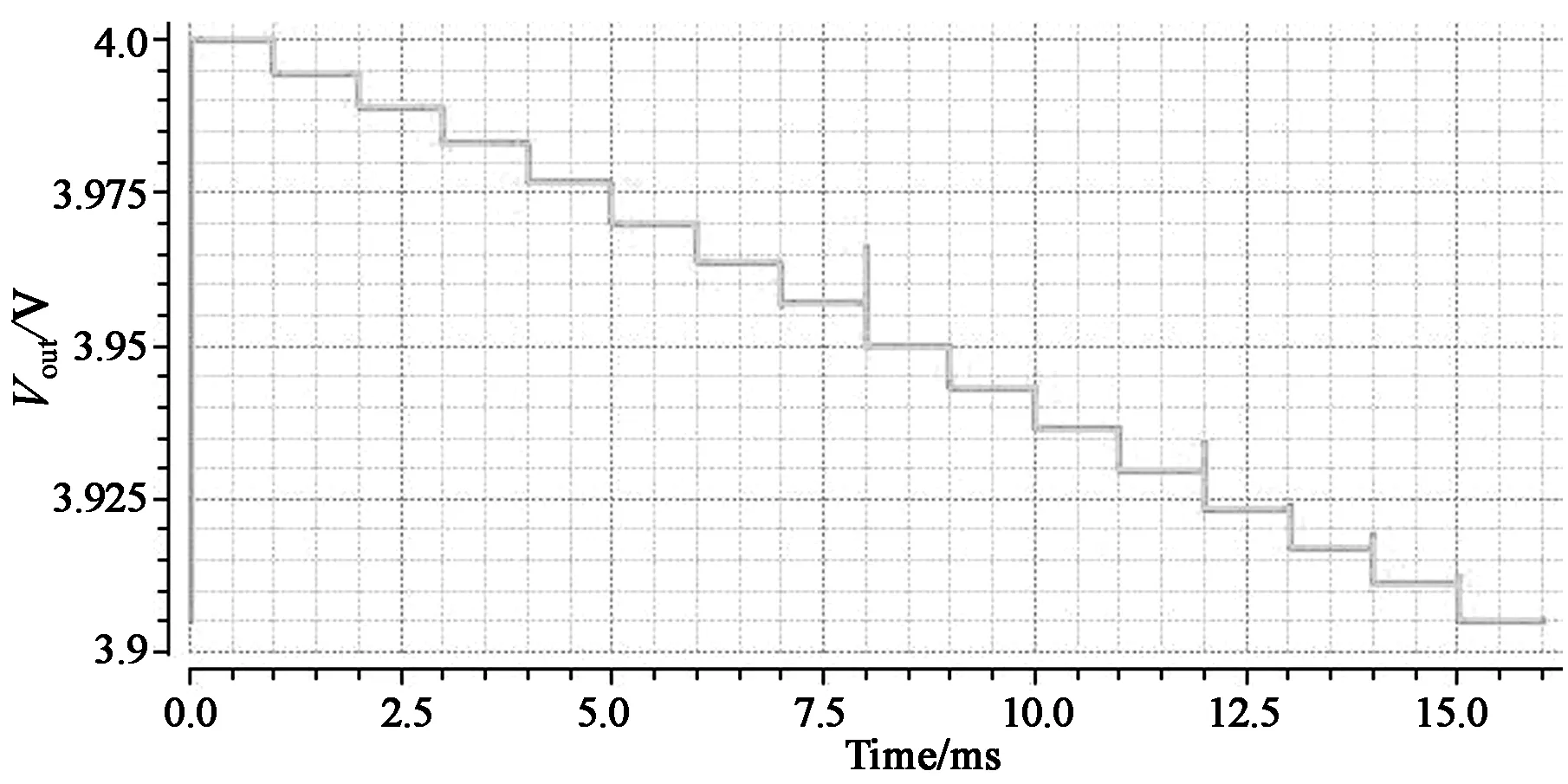

本文基于UMC80nmCMOS工艺对设计的DAC进行了仿真验证。首先对设计的第二级DAC即插值输出缓冲器进行误差分析,将低4 bit的图像数据应用到第二级DAC中,对第一级DAC的输出电压进行插值输出。以VH为4 V、VL为3.9 V为例,4 bit图像数据从1111到0000依次跳变,得到插值缓冲器的输出结果如图7所示。

图7 输出缓冲器插值结果Fig.7 Interpolation results of outbuffer

对插值结果进行采点取值并与由式(4)所得的理论值进行比较,可以得到第二级DAC插值结果的误差,经比较得到16个输出结果最大的误差仅为0.9 mV,使用插值缓冲器作为第二级DAC可以满足高精度10 bit DAC的要求。

将10bit的图像数据应用到驱动电路中,对设计的DAC输出曲线进行线性度分析,结果如图8所示,得到DAC输出结果最大的INL和DNL分别为0.47 LSB和0.24 LSB,仿真结果表明提出的DAC结构具有良好的精度及线性度,满足AMOLED驱动芯片高精度的应用需求。

图8 提出的10 bit DAC的INL(a)和DNL(b)Fig.8 INL(a) and DNL(b) for the proposed 10 bit DAC

图9表示的是当图像数据从0000000000突变到1111111111时10 bit DAC的瞬态仿真结果,应用的等效面板负载为10 kΩ电阻及30 pF电容,仿真结果表明驱动电路电压建立精度达到0.1%的建立时间为3.38 μs,满足分辨率为1 080×2 160驱动芯片的应用需求。

图9 瞬态仿真结果Fig.9 Simulation results of transient

4 结 论

本文针对高分辨率AMOLED驱动芯片的高精度需求,提出了一种应用于AMOLED源极驱动的高精度DAC结构,通过对AMOLED显示屏GAMMA校正方案的深入研究,为进一步提高灰阶电压精度,对线性DAC结构进行了改进。在采用6 bit线性DAC及4 bit插值缓冲器的基础上,增加一个DAC斜率调节单元,可实现DAC斜率的可编程控制,从而实现一条具有3段不同斜率的DAC输出曲线来拟合显示屏的灰阶-电压曲线,并设计尾电流可编程控制的输出缓冲器作为第二级DAC,进而达到更高的灰阶电压精度。仿真验证表明:本文提出的DAC的最大INL和DNL分别为0.47 LSB和0.24 LSB,具有良好的线性度,同时图像数据从最低到最高灰阶跳变时,驱动电路对应的灰阶电压建立时间为3.38 μs。驱动电路可以快速、精确地完成图像灰阶电压的建立,满足1 080×2 160分辨率AMOLED驱动芯片的应用需求。