适用于卫星通信的速率自适应型LDPC译码器设计

田瑞甫,刘 聚,钟 鸣,张朝路,侯 俊

(上海航天电子技术研究所,上海 201109)

0 引言

卫星通信信号在传输过程中受衰减和噪声干扰的影响会出现差错,信道编码技术作为保证信息可靠传输的有效手段被广泛应用于卫星通信系统[1-2]。LDPC最早由Gallager提出[3],经Mackay等人进一步研究表明[4],LDPC码的性能在置信传播(Belief Propagation,BP)译码算法下可以接近香农极限,且具有较低的误码平台[5]。准循环LDPC(QC-LDPC)码,因其校验矩阵具有准循环性,可以采用简单的移位寄存器实现具有线性复杂度的编译码,硬件复杂度大大降低,是CCSDS推荐的卫星通信纠错码型之一[6]。

BP算法涉及较大动态范围取值的非线性函数的计算,不易于硬件实现[7]。因此,实际应用中通常对BP译码算法进行简化,MMSA被认为是在译码性能和实现复杂度间取得较好平衡的一种算法[8-9]。MMSA算法在译码处理过程中,所需主时钟高于输入数据伴随时钟,如果主时钟由输入数据伴随时钟倍频后得到,需要通过硬件锁相环实现,对于不同输入数据速率的译码运算往往需要复杂硬件逻辑和时钟切换逻辑[10-11]。

根据型号任务需求,设计的LDPC译码器采用MMSA译码算法实现LDPC译码功能,并在此基础上通过对输入数据加填充帧和输出数据伴随有效性标记位方式,实现了单一主时钟处理多种速率数据的译码运算。

1 MMSA译码算法

MMSA译码过程是不断迭代的消息传递过程,一般包含4个步骤[12-13]:

① 初始化。设定最大迭代次数,并对每个变量点赋予由信道得到的LLR,作为变量点的内信息。

(1)

式中,Pn为第n个变量节点的信道先验信息。

② 第t次迭代,变量节点到校验节点的传递信息。

(2)

③ 第t次迭代,校验节点到变量节点的信息传递。

(3)

迭代若干次后,若满足最大迭代次数,计算后验概率并判决,否则重复步骤②和步骤③。

④ 计算变量节点的后验概率并判决输出。

每个变量节点输出的后验概率为:

(4)

根据以下规则对每一个比特进行判决:

(5)

式中,最大后验概率L(post)(un)为变量节点n的外信息与节点n的初始似然比信息之和。

2 译码器结构选择

QC-LDPC码的译码器结构主要有3种[14-15]:

① 串行译码:通过重复使用一个CFU和VFU运算单元来完成所有行(列)运算,占用资源最少,但需要很多个时钟周期才能完成一次完整的行(列)更新。

② 全并行结构:通过为每一行(列)配置一个运算单元,并使所有的运算单元并行工作来提高运算速度,最少只需要2个时钟周期就可以完成一次迭代运算,但是需要消耗很多硬件资源,芯片难以支持。

③ 半并行结构:利用QC-LDPC校验矩阵准循环的特点,可以使用半并行结构,将校验矩阵划分成若干个子块,每个子块的节点映射成一个硬件处理单元,每次迭代过程中通过重复一个子块的校验节点与变量节点运算单元来计算该子块校验节点与变量节点的外信息,所有节点的信息更新依次由这一个子块节点处理单元来完成,这种结构能够获得串行和并行的折中。

本文设计基于CCSDS标准(8176,7154)的缩短LDPC码译码器,采用部分并行译码结构,根据H矩阵特点,使用2个校验节点运算单元,16个变量节点运算单元同时运算,即行、列更新运算的并行度分别是2,16,这样的结构需要511×2或者1 022个时钟周期才能完成一次迭代运算,数据吞吐量[13]为:

(6)

式中,dnum为信息比特数;fmax为译码器的工作时钟频率;nc为一次迭代所需周期数;Niter为译码器的迭代次数,如果时钟工作频率为100 MHz,则译码器的吞吐量等于70 Mbps。为简化时钟处理逻辑,采用数据吞吐率为0.5,即100 MHz主时钟处理数据速率50 Mbps。

3 译码器设计

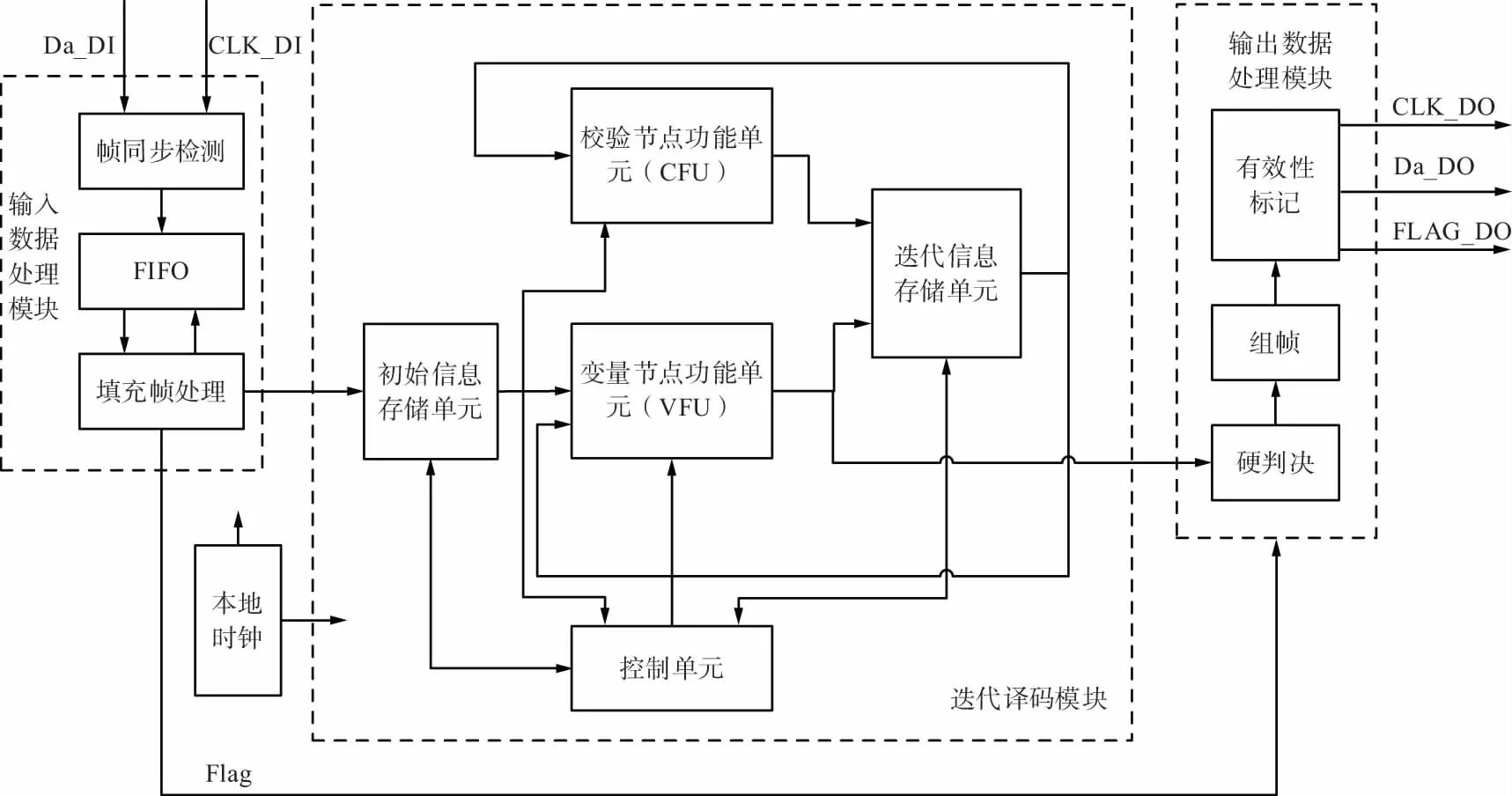

译码器结构如图1所示。

输入数据处理模块对接收各速率数据做帧同步检测、跨时钟域处理和填充空帧。由伴随时钟将数据送入FIFO,同时对输入数据做帧格式检测,输入数据格式错误则对FIFO做复位处理,格式正确数据送入后续处理模块。本地时钟读取FIFO数据时根据FIFO的空满状态添加空帧,以连续数据形式送入后续译码模块,并将数据是否有效状态量Flag送入输出数据处理模块。

图1 译码器结构

输出数据处理模块根据式(4)和式(5)对完成迭代译码后的数据硬判决后输出,并根据接收接口处理模块中FIFO读取数据的有效性,对输出数据有效性做标定。

3.1 填充帧处理单元设计

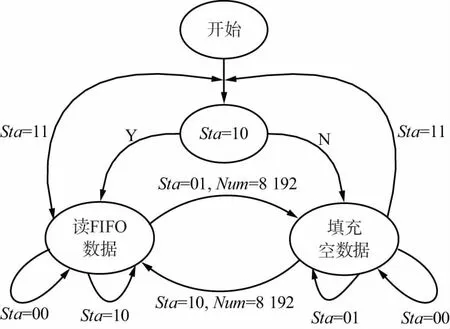

输入数据处理模块填充帧处理单元状态转移如图2所示,用于FIFO数据读取状态控制。

图2 填充帧处理单元状态转移示意

根据型号任务需求,为适应不同卫星通信工作模式,需要同一译码器完成多种速率LDPC译码任务。为解决不同速率时复杂时钟切换逻辑问题,也为后续更多速率译码留有升级空间,采用了单一主时钟加填充帧的处理模式。当输入数据速率低于处理主时钟时,添加空帧使核心译码模块处于固定速率连续工作状态,不需要时钟切换。

输入数据处理模块FIFO的读取时钟固定为50 MHz,读取端根据设置FIFO的满/空标记读取或添加填充帧,共3个状态:初始状态、读FIFO数据和填充空数据,状态标记由Sta表示(Sta=10表示FIFO的满状态标记为“1”,空状态标记为“0”)。

FIFO的读取标记经延时后送至输出数据处理模块,作为数据有效性标记位伴随输出(以高电平表示该帧数据有效,低电平表示该帧数据无效)。后续数据处理单机根据伴随标记位状态读取数据。

3.2 变量节点单元设计

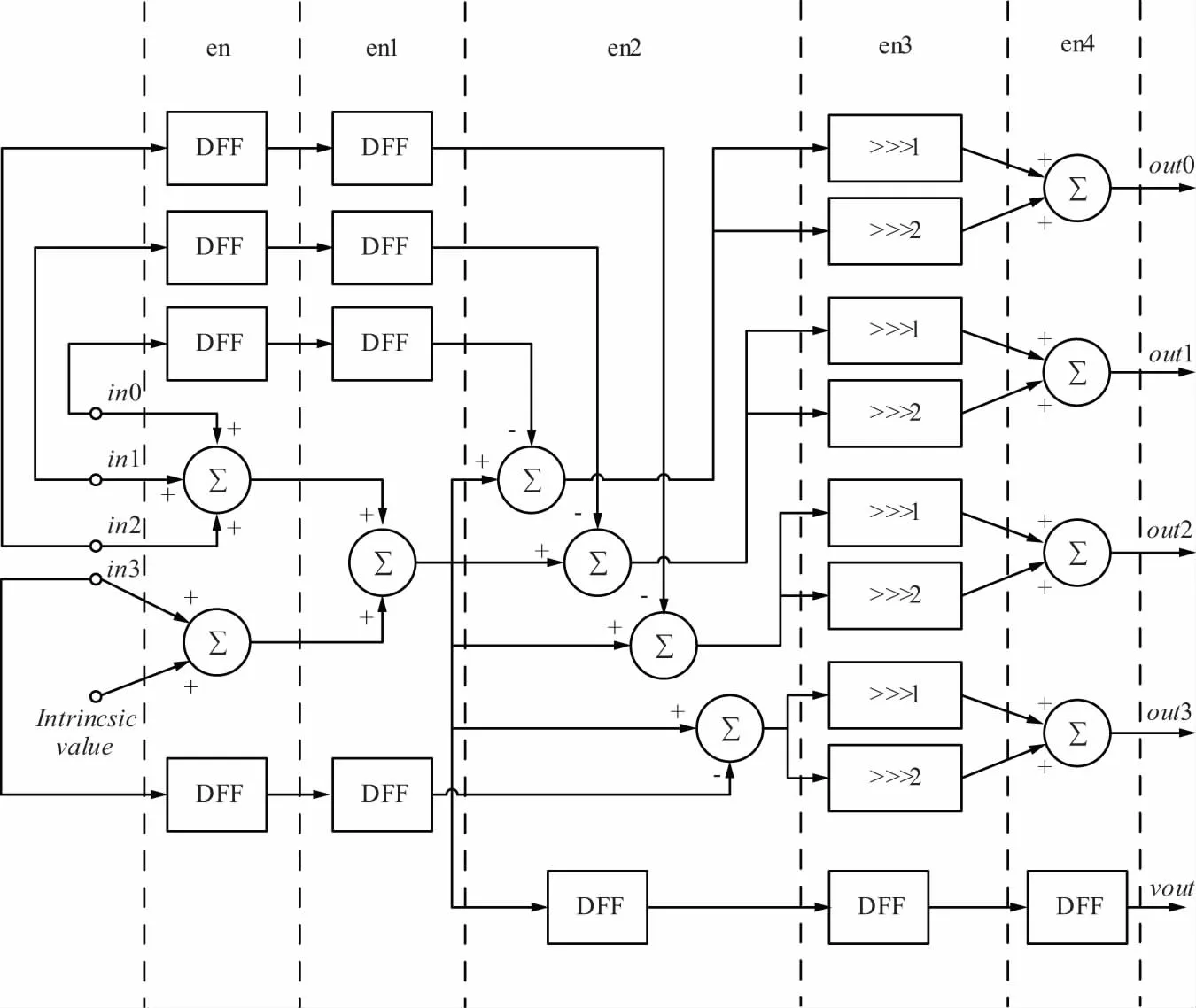

迭代译码模块中变量节点单元结构如图3所示[13],用于实现变量节点数据更新。

变量节点更新过程又称为垂直运算,主要实现式(2)内容,作用包括2部分:一部分是更新变量节点消息,送至迭代信息存储器用于给校验节点进行下一次迭代;另一部分(vout)是更新后验概率消息,该消息主要用于硬判决。

变量节点单元工作流程为:从每个信道初始信息存储器中读出一个信道似然比(LLR)信息。同时,根据地址从4个迭代信息存储器中读出4个校验节点信息。变量节点单元通过对由迭代信息存储器中读出的校验节点信息和LLR信息进行垂直运算,得到新的变量节点信息。最后,将新的变量节点信息按读地址写回到各迭代信息存储器中,完成置信度信息更新。完成一次迭代的垂直运算需要对这个过程重复10次。

垂直运算过程采用5级流水线方式,完成算法中变量节点到校验节点的计算,其中式(2)的factor取0.75[8],只要进行移位相加就能实现。

图3 变量节点单元结构

图3中的in0,in1,in2,in3是在Tanner图中与一个变量节点相连的4个校验节点更新后的信息。IntrinsicValue是变量节点的初始化信息。out0~out3是4个变量节点进行更新之后的信息。vout是内信息和4个输入信息的和,通过检查该信息的最高位来判决。

3.3 校验节点单元设计

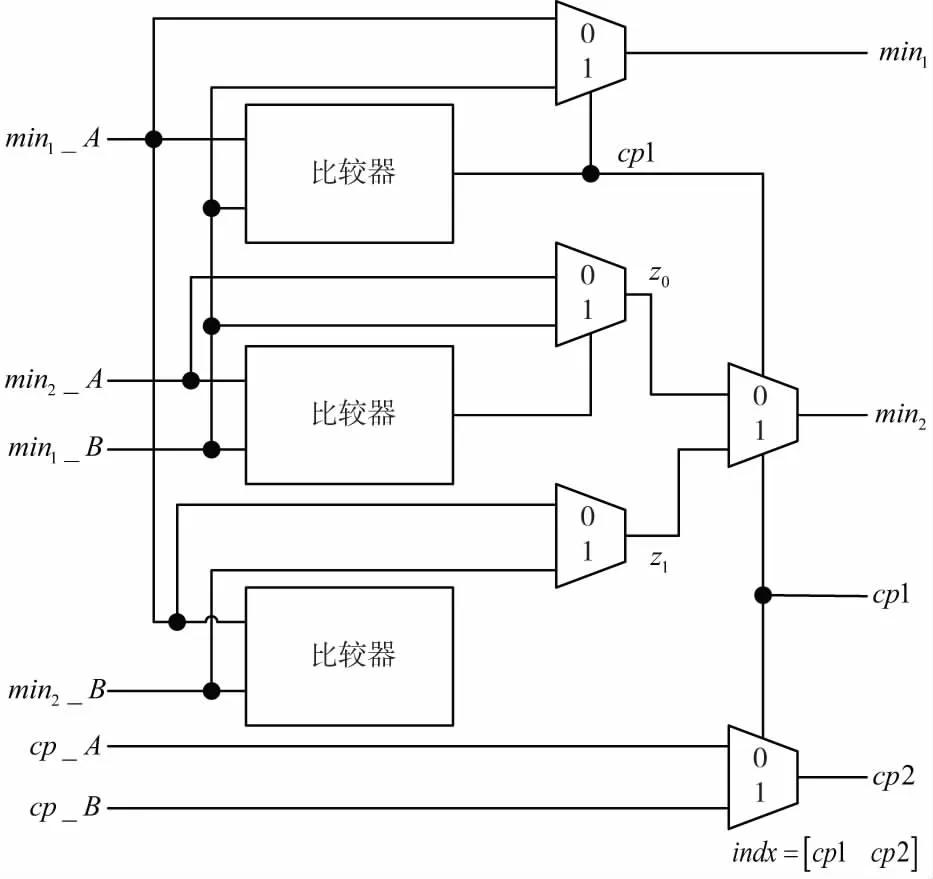

迭代译码模块中校验节点单元结构如图4所示[12],用于实现校验节点数据更新。

图4 校验节点单元结构

校验节点处理单元主要实现式(3),用来完成校验节点消息的更新,其更新过程称为水平运算,是迭代过程的一部分,进行的操作主要是使译码器对每个行块的第i行做行置信度信息更新运算。

其工作流程为:每个校验节点从32个迭代信息存储器中读出32个变量节点消息。由于32个存储器的读地址均为i,因此这一步操作只需要计数器就能实现信息的读取。然后,32个变量节点信息读出后直接送给该校验节点单元进行信息更新运算,得到新的校验节点信息。最后,将新的校验节点信息按读地址写回到各迭代信息存储器中,完成校验节点信息更新。完成一次迭代的水平运算,即校验节点信息更新运算,需要对这个过程重复10次。

在修正最小和算法中,校验节点处理模块需要完成的工作是求出与一个校验节点相连接各变量节点数据(除自身外)绝对值的最小值。如果当前节点的值为最小值,则输出为其他所有值中的最小值,即次最小值。求各数据符号值的乘积,将所得最小值与符号值合并成新数据。

图4所示结构图主要实现功能:

(7)

各符号的乘积可以通过查找表的方式得到。

3.4 控制单元设计

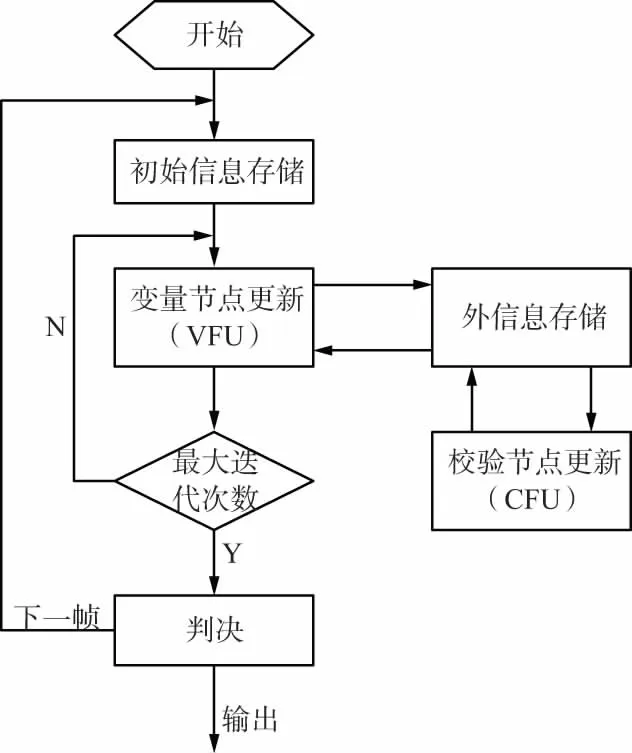

迭代译码模块中控制单元流程如图5所示,用于各单元工作协调控制。

图5 控制单元流程

迭代译码模块的工作流程[16]如下:

① 总状态机控制初始信息存储单元的一组RAM,该组RAM写使能有效,接收来自信道的信息,当一帧数据全部存储后,切换到另一组RAM存储下一帧数据,同时返还给总控一个信号。

② 控制单元在一帧数据存储结束后,使能VFU模块,并使能初始化存储单元读取功能,进行变量节点更新运算,运算结果写入外信息存储模块。

③ VFU运算完成后,VFU单元给总控发送结束信号,总控屏蔽VFU和初始化存储单元,启动CFU的运算。CFU从外信息存储单元读取信息,并将运算结果写入、读出地址相同位置中。

④ CFU运算结束后,CFU单元给总控发送结束信号,总控屏蔽CFU单元,启动VFU单元和初始化存储单元,VFU单元和CFU单元交替运算。

⑤ 经过10次迭代运算后,进行硬判决,对判决数据做有效性标记并输出,开始下一帧数据迭代译码。

4 译码器实现

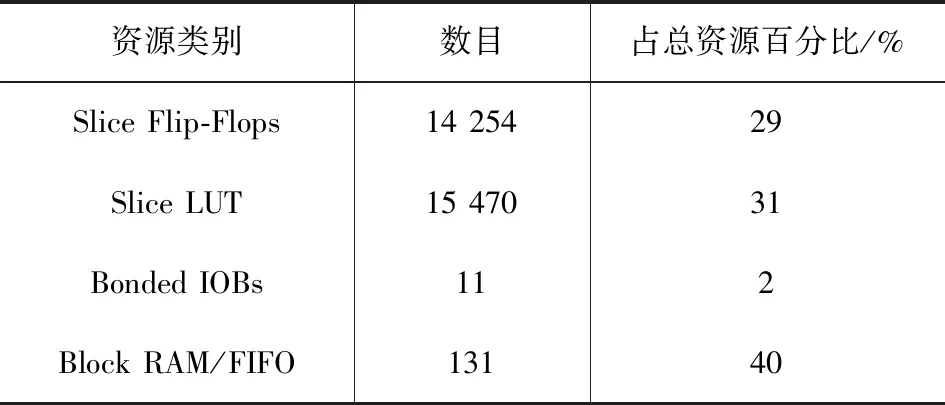

基于前文设计思想,采用VHDL语言编写,ISE14.7编译环境,在Xilinx公司Virtex-4系列FPGA芯片XC4VSX55上实现了CCSDS规定的缩短(8176,7154)准循环LDPC译码器。译码器的逻辑资源和存储资源利用情况如表1所示。

表1 译码器资源利用率

资源类别数目占总资源百分比/%Slice Flip-Flops14 25429Slice LUT15 47031Bonded IOBs112Block RAM/FIFO13140

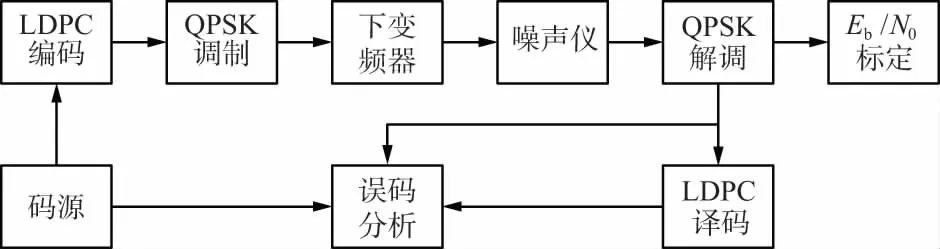

译码器设计实现后,需要对其进行测试,以验证其纠错性能[17]。译码器测试原理如图6所示。

图6 译码器测试原理

测试步骤如下:

① 码源产生PN15伪随机数据,按CCSDS标准组帧;

② 在数传发射机内进行LDPC编码和QPSK调制;

③ 射频信号通过下变频器到中频信号,并在中频加噪声;

④ 在接收机内进行QPSK解调[18],并标定输出Eb/N0值;

⑤ LDPC译码,分别比对译码前后对应误码率。

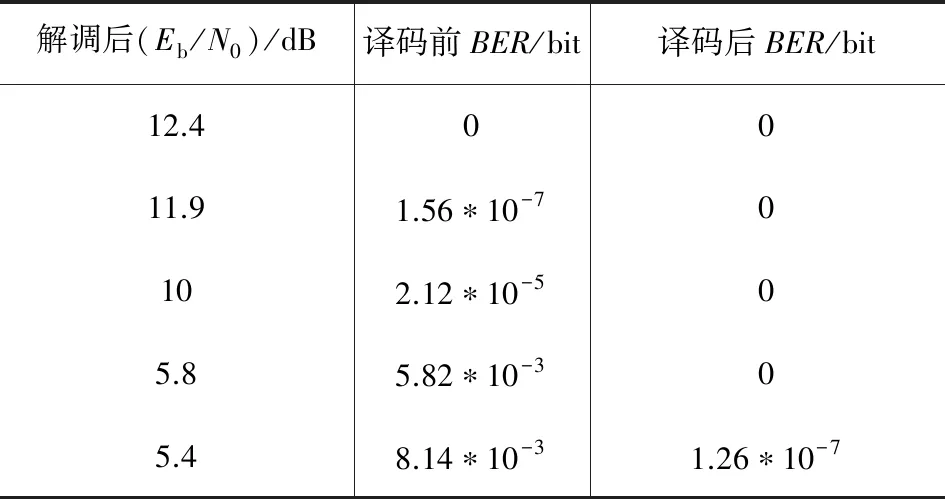

分别在50,30,20,10,2,1 Mbps速率下进行了测试,不同速率下译码性能测试结果一致,如表2所示。

表2 译码性能测试结果

解调后(Eb/N0)/dB译码前BER/bit译码后BER/bit12.40011.91.56∗10-70102.12∗10-505.85.82∗10-305.48.14∗10-31.26∗10-7

测试结果显示,设计的译码器在BER为1×10-7量级有6.5 dB增益。

5 结束语

以航天型号为基础,采用MMSA译码算法对CCSDS标准推荐的缩短LDPC码实现译码功能的基础上,通过对输入数据加填充帧和输出数据伴随有效性标记位的方式,实现单一主时钟处理不同速率数据功能。通过对输入数据格式判断和复位处理相结合,使译码器具有接收错误数据后自恢复功能。实验结果表明,译码器在BER为1×10-7量级有6.5 dB增益,且在不高于50 Mbps速率条件下可以速率自适应。