SOPC通用化弹载自测试平台的设计与实现*

陶然,王昭磊,罗悦,田琨

(1.北京航天自动控制研究所,北京 100854;2.北京电子工程总体研究所,北京 100854)

0 引言

传统的导弹武器测试方法为地面测试,通过综合测试系统完成对导弹内部各产品硬件、软件及系统功能、特性的全面检查,将弹上各测试信号全部引入地面,通过各类测试设备完成测试功能。地面测试方法需将大量待测信号经过长线传输引入地面设备,影响测试准确性,导致弹地接口庞大,地面测试设备复杂度高,资源消耗大。

随着武器系统的智能化、网络化发展,在不增加过多的有效载荷情况下使得弹载自测试功能逐渐可行,简化了弹地接口,降低了弹上产品和地面产品的耦合度,可独立进行模块化、通用化设计,降低了研制成本。若设计一种功能通用、扩展性好、可靠性高的弹载自测试设备,根据不同的被测产品进行快速的配置实现一个测试平台测试多种产品的功能,既可以减少资源重复、通用性差的问题,同时大幅降低导弹武器系统研制成本。

1 系统架构设计

1.1 弹载自测试架构现状

现阶段弹载自测试技术系统架构主要分为2种:

(1) 基于弹上载荷实现的非独立式自测试架构。主要应用于对小型化要求较高的武器系统中,利用弹上载荷中未使用的空闲资源实现弹载自测试,其测试电路与弹上功能电路集成于同一印制板内,测试电路的可靠性直接影响弹上载荷飞行的可靠性,且测试资源受制于弹上载荷的空余资源,存在一定的局限性,且无法实现通用化。

(2) 基于DSP(digital signal processing)+FPGA(field programmable gate array)的独立弹载自测试架构[1]。随着武器系统复杂程度的不断提升,利用DSP作为核心处理器同时辅助FPGA扩充处理器接口资源,此类架构需要针对2类芯片设计独立的外围电路以及专用的外部总线进行数据交互,可靠性较低,且需要针对DSP及FPGA独立进行开发,增加了调试及开发的成本。

本文提出SOPC弹载自测试架构,SOPC资源丰富,硬件电路设计及软件开发集成于单个器件内,降低开发成本的同时具备较强的通用化及可扩展性,可以满足现阶段武器系统复杂测试及小型化的需求。

1.2 SOPC技术

SOPC,即片上可编程系统(system on a programmable chip,SOPC),通过可编程逻辑技术将整个系统集成到单个芯片上,是一种新型的嵌入式系统,结合了SOC,PLD,FPGA的各自优势,片上资源丰富,包括嵌入式处理器、DSP、存储器、外围IO及可编程资源,同时是一种具有灵活设计方式的可编程系统,具备可剪裁、可扩充、可升级的特点。

基于SOPC技术的处理器按类型分为软核处理器与硬核处理器2种。软核处理器即通过FPGA逻辑源码构建出虚拟的处理器,处理器实现是以逻辑源码的IP核方式进行设计,用户可以根据自己的需求修改IP核[2]。硬核处理器是固化在FPGA内部的独立处理器内核,用户只能对其进行配置而不能对其接口进行修改与替换,即固化在FPGA内部的ASIC(application specific integrated circuit)电路,性能上硬核处理器运算速度较高,整体功耗低。基于SOPC的通用化弹载自测试平台作为武器有效载荷之一,首要考虑的是其可靠性与环境适应性,其次需要具备高通用性,适应多种类型接口数据的高速处理与运算,硬核处理器环境适应性强、可靠性高,通过基于ARM COTEX A9的硬核处理器SOPC芯片,实现了应对复杂环境条件下的高可靠弹载测试。

1.3 平台架构设计

弹载自测试平台基于小型化、通用化的原则,与弹上计算机进行集成化设计。现有导弹武器系统对弹载测试资源类型的需求相同,其中数字量、模拟量为通用测试资源需求,不同装备型号的测试信号数量不同,所选用的总线类型不同,为满足通用化需求,弹载自测试平台可设计足够的数字量信号,且同时具备多种不同类型总线通讯功能,弹载自测试平台通用化资源详见表1所示。

表1 弹载自测试平台通用化资源Table 1 General missile-borne self-test platform resources

本文提出的基于SOPC技术的通用化弹载自测试平台系统架构如图1所示,整个自测试平台以SOPC处理器为控制处理核心,外部连接电源模块、DDR3存储器模块、SPI FLASH模块、各类通信模块、模拟量隔离及信号调理模块以及数字量输入输出模块,其中通信模块包括1553B总线、CAN总线、RS485/RS422、以太网以及RapidIO,通信模块可兼容不同型号装备的通信需求,以最大程度上保证平台的通用性。SOPC处理器IP资源丰富,同时基于FPGA的可编程特性实现数字量输入、输出接口以及各类总线通信接口的可配置功能,以适应各类复杂系统的测试需求,此外考虑到后续机内总线的发展与应用,预留Rapid I/O接口满足后续弹上计算机机内总线的纵向扩展功能。

弹载自测试平台作为弹上计算机的机内载荷以子板连接的方式与弹上机进行连接,为实现独立有效性的弹载测试,应最大程度上减少与弹上各设备的耦合性,故自测试平台设计采用独立电源与弹上机隔离,各对外接口进行电平隔离,最大程度上保证测试的有效性及可靠性。

2 硬件平台设计

2.1 SOPC架构设计

本文采用ZYNQ[3-4]SOPC实现通用化弹载自测试平台,ZYNQ由多个ARM COTEX A9硬核及传统FPGA逻辑资源构成,通过内部总线将ARM核PS部分(Processing System)与FPGA的PL部分(Programmble Logic)部分互联为一个整体,以此获得高内聚、低耦合的SOPC架构。通过利用PS部分灵活裁剪的各类接口控制器以及PL部分强大而灵活的IP核资源实现SOPC处理器设计[5-6],SOPC架构如图2所示。自测试平台采用了PS部分可配置硬核Uart接口接收弹上计算机母版的RS-485导航数据,通过ARM硬核处理器对关键导航节点参数进行实时判断后,将测试结果通过可配置硬核CAN总线接口控制器或Ethnet接口控制器传输至地面,为满足弹上机导航数据的高实时性处理及有效性数据鉴别要求,通过高度集成的DDR接口控制器完成外部DDR3的高速数据存储与运算,同时通过多路MIO(Multiuse I/O)接口输出关键测试信号及指示,确保外部被测弹上载荷与测试平台的测试状态统一有效。考虑到自测试平台的通用性与可扩展性,在PL部分设计了1553B接口控制器IP核、双向多路可配置GPIO IP核、高可靠可配置Uart IP核、以及XADC运算硬核,各IP核通过AXI4总线挂载至硬核处理器端,面对数据量较大且实时性高的弹载测试多个硬核间可以进行独立配置与并行处理,可由运行于ARM处理器中的顶层应用程序统一控制。通过MTG/MTH硬核收发模块设计多路Rapid IO高速通信以增加自测试平台的数据传输纵向性能扩展能力[7-8]。

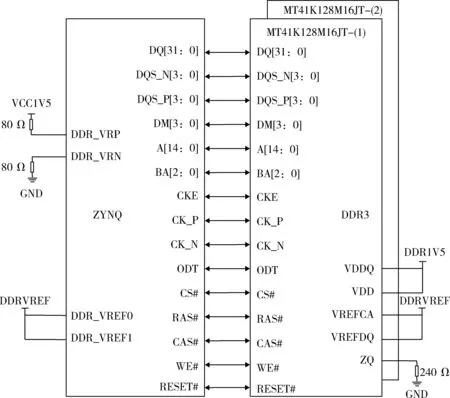

2.2 DDR3缓存模块设计

弹载自测试平台通过接收总线指令进入弹载测试模式,根据不同测试流程的配置,并行采集外部各类通信接口、数字量及模拟量的消息,将采集到的数据传输至ARM处理器进行判断与决策,选用2片DDR3颗粒构建外部32-bit存储模块,存储容量达512 MB,最大支持533 MHz时钟频率,充分满足大数据量弹载测试的实时性需求。DDR3存储颗粒与PS部分DDR3硬核控制器相连[8],通过并联2片DDR3中的数据总线DQ[15∶0],数据选通差分信号DQS_N[1∶0],DQS_P[1∶0],数据写入标志信号DM[1∶0]3类信号,使其扩展为DQ[31∶0],DQS_N[3∶0],DQS_P[3∶0],DM[3∶0],实现方式如图3所示。

图1 通用化弹载自测试平台系统架构Fig.1 Architecture of general missile-borne self-test platform

图2 SOPC架构设计Fig.2 Architecture of SOPC

图3 DDR3缓存模块Fig.3 DDR3 cache module

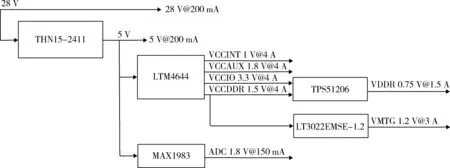

2.3 电源设计

通用化弹载自测试平台作为独立测试平台,需要具备稳定可靠的电源以提供准确的测试结果,采用外部28 V供电作为整体输入,通过2次电源转换为5 V电源后供各模块使用[9],平台2次电源与弹上计算机电源物理隔离,由于SOPC及外部应用电路种类较多,考虑小型化设计整体思路,电源设计应最大程度上遵循一转多路、复用等原则,电源设计如图4所示。

选用可配置4路4 A输出通道阵列LTM4644电源模块提供SOPC需要的1 V内核电压、1.8 V辅助电压、3.3V I/O电压以及1.5 V DDR3存储电压,LTM4644最大支持4通道独立输出,可通过外部电路配置输出电压范围,内置开关控制器、功率FET、电感器等组件,体积小且集成度高,同时具备过压、过流及过热保护,最大程度上保证弹上载荷的可靠性,保证设计安全性,可有效避免因测试状态不确定而造成的弹上负载损坏的情况。同时选取3种线性电源实现MTG模块1.2 V电源电压、0.75 V DDR参考电压以及1.8 V ADC电源供电。通过设计自测试平台SOPC及外围电路上电顺序提升系统可靠性,遵循5 V上电后,内核1.0 V上电,1.8 V辅助电源至3.3 V IO上电,最后DDR模块上电的顺序,有效避免内核未启动的状态下IO上电后输出不定态导致的误发测试指令。

2.4 通信控制模块设计

随着弹上载荷复杂化的趋势,武器系统所采用的数据传输接口从最初的单路点对点传输发展为组网协同多路冗余传输,传输速率也从Mbit/s发展至100 Mbit/s,武器系统常用的各类数据传输总线包括1553B总线、CAN总线、RS-485总线及以太网,为最大程度上实现通用化弹载自测试平台,通信控制模块兼容目前各类总线通信接口,以应对不同武器型号的运用,同时应具备高速数据传输扩展能力[10]。本文通过设计1553B控制IP核控制外部总线协议芯片的方式实现1553B总线通信,RS485总线、CAN总线及以太网通过PS部分硬核控制器配合外部总线收发器及PHY芯片进行实现,同时通过PL部分设计可靠配置Uart IP核扩展12路RS-485/422接口以满足不具备总线接口的弹上载荷数据传输。

2.4.1 1553B IP核设计

为实现1553B子地址、应用层协议通用可配置,用硬件描述语言实现1553B控制器IP核模块控制外部1553B协议芯片。本文选用国产化1553B协议芯片,总线传输速率由传统的1 Mbit/s提升至4 Mb/s,电平标准兼容LVTTL,可直接与FPGA的IO口3.3 V电平进行直连,在实现通用化1553B通信的基础上,具备一定的总线速率扩展能力。IP核模块具备AXI4(Advance Extensible Interface 4.0)总线逻辑功能,以外设的方式挂载至ARM处理器,采用通用化设计思想,可通过处理器在线配置的方式可更新1553B子地址、站点等内容。针对不同型号,可进行在线重配置与应用层二次开发。同时,处理器端应用程序通过软件的方式实现复杂协议与帧结构解析,设计成本降低的同时增强了模块灵活性。

基于AXI4总线的1553B控制IP核设计组成如图5所示,IP核由AXI4总线接口部分与用户逻辑块两部分组成,ARM处理器通过AXI总线互联(AXI Interconnect)将控制信号及数据流传送至AXI4 IP中总线接口部分完成总线地址译码,译码后的数据流写入1553B用户逻辑块(1553B User Logic)中相应寄存器,用户逻辑块控制外部1553B协议芯片完成数据收发,将收到的数据写入用户逻辑块数据寄存器,同时操作读写数据成功寄存器置位,用于向处理器指示当前IP核工作状态,运行于ARM处理器上的应用程序周期性查询该地址空间,确定数据发送或接收状态以及后续数据收发决策。

图4 电源设计Fig.4 Power design

图5 基于AXI4总线1553B的IP核Fig.5 1553B IP core based on AXI4 bus

2.4.2 Uart模块设计

SOPCUart模块由PS部分硬核Uart模块与PL部分高可靠Uart IP核共同组成,外部通过MAX3485收发芯片实现RS485/422串行通信,资源数量总计14路。利用PS部分Uart硬核接收弹上机下传的导航解算数据及配置信息,PS部分外部收发芯片硬件上关闭的发送使能,使其上电后始终工作在接收状态。其余Uart模块均通过PL部分进行扩展,为增加串行数据传输的可靠性及有效性,摈弃传统IP核资源,自行设计了具备高可靠性的Uart IP核,高可靠Uart IP核最大支持921 600波特率,奇偶校验位可设置,IP核针对所配置的波特率进行16倍频后作为数据采样时钟,对每一比特位串行数据进行三取二表决操作,所采集到同一比特的3个数据中连续2个数据相同时则视为有效数据,可有效排除因各类干扰引入的错误数据,增加了弹上测试的可靠性。IP核具备AXI4总线接口逻辑,IP核所采集到的串行数据通过可通过AXI4总线传输至ARM处理器端供顶层应用程序进行协议解析与处理。

2.4.3 CAN总线及以太网设计

CAN总线及以太网设计均采用PS部分硬核模块配合外部电平转换及PHY芯片实现。CAN总线协议及以太网MAC层协议由PS部分硬核实现,硬核结构精简且可靠性高,搭配外部芯片大大降低了开发成本。采用隔离型CAN总线收发器ADM3053实现CAN总线信号下传,ADM3053将双通道隔离器、CAN收发器与DC/DC转换器集成于单个器件中,兼容5 V/3.3 V电平,以最小硬件资源设计实现隔离CAN总线的收发控制。考虑到自测试平台的通用化设计,选用88E1518以太网PHY芯片,根据不同频率的外部晶振自适应IEEE 802.3协议以太网10/100/1 000 MB带宽,支持RGMII(reduced gigabit media independent Interface)接口,具备同步时钟恢复及自动极性矫正、支持低VIO压供电。

3 平台软件设计

3.1 驱动层软件设计

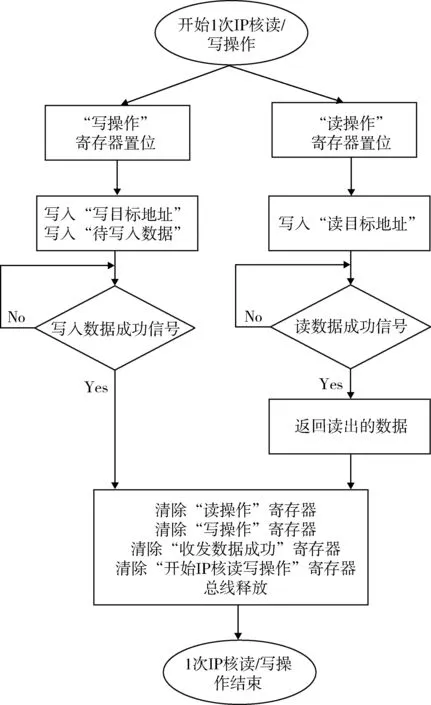

驱动层作为应用程序与IP核之间的纽带,实现IP核的控制与数据处理收发。应用程序通过驱动层将相应地址的寄存器置位后,开始1次数据传输周期[11-12]。1553B IP核读写操作流程如图6所示。

图6 1次1553B IP核读/写操作Fig.6 A 1553B IP core read/write operation

开始1次数据传输周期后,首先将“开始IP操作寄存器”置位,之后对应读写操作,分别将“读操作寄存器”或“写操作寄存器”置位,之后写入“写目标地址”、“待写入数据”或“读目标地址”,驱动层循环查询读/写数据成功信号,数据成功后,若为读数据操作,则返回IP核所读出的数据后复位各寄存器状态,写操作则直接复位各寄存器,至此1次IP核操作结束。

3.2 应用层软件设计

弹载自测试平台应用层软件需要周期性查询地面测发控系统发送的总线测试指令,收到测试命令进行测试项目解析后分发至各模块开始测试,需要将采集到的各类的接口数据按协议组成对应帧结构后,通过总线进行下传,其中包括采集I/O口数据、AD模拟量数据、RS485数据等。应用层软件设计流程如图7所示。

自测试平台上电后,首先通过Begin_T()函数查询总线自测试开始命令,当收到自测试开始指令后,执行Scanf_Bus()函数查询地面测发控发送的测试项目指令,通过解析测试项目,分别向弹上模块A,B,C发送RS485,IO以及AD测试指令,其中模块A测试指令通过485消息发送,模块B,C测试开始指令通过约定的GPIO发送。开始测试指令发送后,延迟5 ms应用程序查询GPIO以确认各模块返回的的测试结果准备好状态,当收到准备好状态后,读取各接口的测试数据,最后向各测试模块发送测试结束指令EOC_T_Uart(),EOC_T_IO(),EOC_T_AD(),各模块状态复位。应用程序将各模块返回的测试结果进行组帧,通过总线发送至地面测发控。

4 自测试平台配置方法

系统测试流程由地面测发控计算机控制,第1次测试开始前需要对自测试平台进行配置,当配置完成后,后续的测试即可直接向自测试平台传输带有配置信息校验帧的测试流程码。测发控计算机向弹上机上传武器型号配置文件,弹上机收到配置文件后将结果解析后通过Uart接口传输至弹载自测试平台,自测试平台应用程序根据弹上机传输的配置信息,解析出详细的接口配置信息并记录相应的校验信息,将配置信息写入PL部分配置寄存器,从而配置自测试平台各对外接口通道数量及通道状态。同时配置信息会备份至FLASH存储器中[13-15]。配置完毕即可进行正式测试流程,自测试平台接收弹上机下发的测试流程码,将测试流程码通过不同的接口如IO,Uart等分别传输至各弹上载荷,各弹上载荷回复相应的测试流程确认帧后,进入模块自测试,此时自测试平台同步接收各载荷传输的测试数据或测试结果,将测试结果组帧后,通过总线进行下传。整体操作可重复配置,最大限度降低系统功耗的前提下实现了在线动态可配置。如图8所示。

图8 自测试平台配置方法Fig.8 Self-test platform configuration method

5 结束语

本文基于导弹武器弹载测试系统的通用化、轻小型化需求,提出了基于SOPC的弹载自测试技术,充分发挥了FPGA的硬件可编程性、实时性、高度集成性、可靠性的特点,大大提高了弹载自测试平台的通用化和可靠性,并且该系统结构简单,性能可靠,最后给出了弹载自测试平台在线配置方法,配置方法灵活,极大程度上降低了系统测试的成本。

SOPC通用化弹载自测试平台需要在实际应用中不断积累和完善,在以下2方面可以进一步改进:

(1) SOPC器件的国产化替代,现阶段尚无同等资源数量的SOPC器件替代,可以针对实际应用场合缩减部分资源以实现器件的国产化;

(2) 扩展测试资源,现阶段通用化平台空余资源仍较为充裕,可以根据实际需求进行资源横向扩充,以及利用灵活的IP资源进行纵向扩展。