一种面向5G通信的宽带压控振荡器设计

张 博, 王三路, 孙景业, 吴昊谦

(西安邮电大学 电子工程学院, 陕西 西安 710121)

压控振荡器(voltage-controlled oscillator,VCO)为无线通信系统提供载波信号,是无线通信系统的重要组成部分之一[1]。随着全球5G通信频段的推出,为了满足5G通信频段3.3~4.2 GHz以及4.4~5.0 GHz的宽频带需求,5.0 GHz压控振荡器的研究受到越来越多的关注[2-3],设计并实现宽带压控振荡器成为研究热点[4-6]。

常用的压控振荡器或者采用3位开关电容阵列实现5.57~6.17 GHz的频带范围[7];或者采用4位开关电容阵列,实现3.12~4.21 GHz的频带范围[8]。其都采用较少比特位的开关电容阵列避免恶化相位噪声性能,但较少比特位的开关电容阵列也限制了更宽的频带范围[9-11]。

本文拟设计并实现一款面向5G通信系统的宽带压控振荡器芯片。拟采用6位开关电容阵列实现覆盖3.3~4.2 GHz以及4.4~5.0 GHz的全球5G通信频段。针对6位开关电容阵列结构带来的相位噪声性能的影响,设计中通过选取高品质因子值电感、应用二次谐波谐振滤波技术以及改进开关电容阵列结构,实现对相位噪声性能的优化。

1 整体电路设计

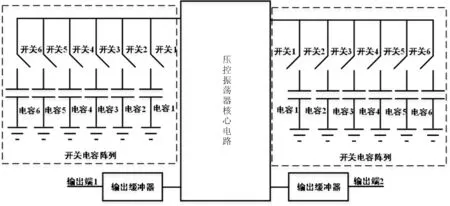

宽带压控振荡器整体电路主要由VCO核心电路、6位开关电容阵列和输出缓冲器三部分组成。其结构如图1所示。VCO核心电路主要通过调谐电压产生单子带调谐频率曲线[12-14]。6位开关电容阵列用于产生64条频率调谐曲线,拓宽调谐频率范围。输出缓冲器用于抑制下一级电路所带来的频率偏移以及对压控振荡器核心电路相位噪声的影响。

图1 压控振荡器整体电路结构框图

1.1 VCO核心电路

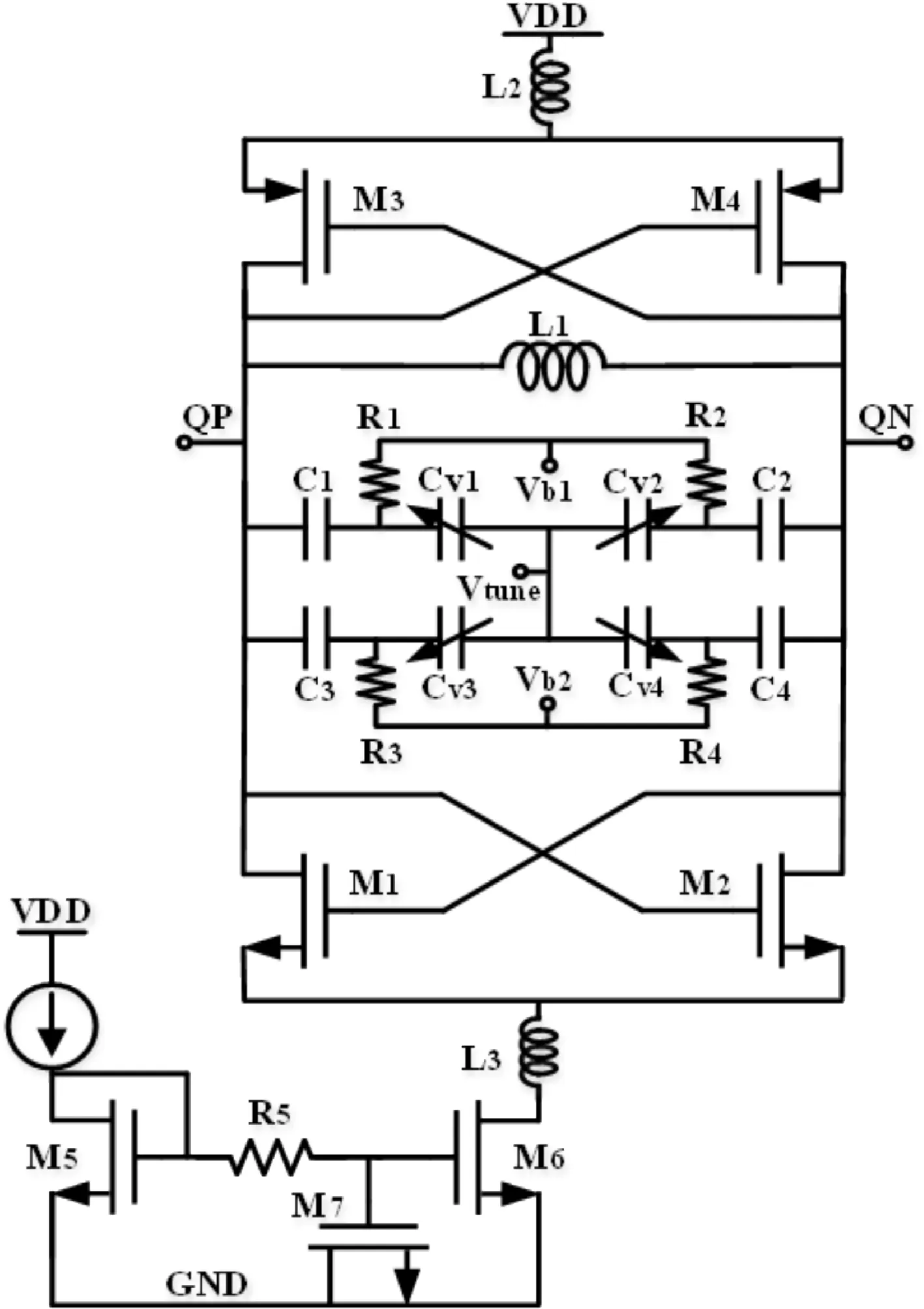

压控振荡器核心电路结构如图2所示。

图2 压控振荡器核心电路结构

其中VDD、GND分别表示电源和地,Vb1、Vb2为偏置电压,Vtune为调谐电压,QP、QN为VCO核心电路差分输出。为了降低相位噪声的影响,实现波形上升和下降时间对称性,VCO核心电路采用互补型金属-氧化物-半导体(complementary-metal-oxide-semiconductor,CMOS)交叉耦合结构。CMOS管M1、M2、M3、M4作为负阻,补偿谐振回路的阻抗损耗。VCO核心电路通过尾电流管M5、M6提供核心电路偏置电流。电阻R5以及MOS管电容M7作为低通滤波,抑制电流源上的交流抖动。电感L2、L3被用来在振荡频率二倍频处提供高阻,抑制互补管对谐振回路品质因素的降低,其采用二次谐波谐振滤波技术,以抑制相位噪声[8]。变容二极管Cv1、Cv2、Cv3、Cv4采用并联结构以提高调谐曲线的线性度。

电阻串联转并联谐振回路结构如图3所示。

图3 电阻串联转并联谐振回路结构

图3中的L为电感,RL为电感寄生串联电阻,C为电容,RC为电容寄生串联电阻,Cvar为变容二极管电容,Rvar为变容二极管电容寄生串联电阻。VCO核心电路中电感的选取对整体谐振回路品质因子的值有很大影响。

由图3电阻串联转并联谐振回路结构,容易推导得到并联阻抗RP以及整体谐振回路品质因子Qtot,其推导过程分别为

(1)

(2)

其中,QL、QC、Qvar分别为电阻串联的电感支路、电容支路和变容二极管支路的品质因子。式(1)中并联阻抗RP值决定着VCO的起振条件。式(2)右边第一部分为主要噪声贡献,其决定着整体谐振回路Qtot的值,QL与L/RL成正比。通过选取L/RL的最大值,得到最优Qtot值。

1.2 开关电容阵列

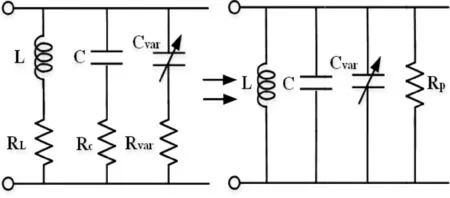

设计的6位开关电容阵列电路结构如图4所示。

图4 设计的开关电容阵列电路结构

图4中的D0—D5为6位数字控制位。与传统结构不同,设计的六位开关电容阵列电路结构在电路中增加了上拉电阻R7、R8并增加了反相器电路。

即使MOS管M9断开,VCO输出的差分大信号仍然会耦合到M9的漏极(drain)和源极(source)。若信号幅度足够大,M9的漏衬底、源衬底节点可能会发生正向偏置,这将会对VCO添加额外的噪声。为了抑制这种情况,当M9关断时,R7、R8被用来把M9的漏极节点和源极节点拉至VDD,纠正M9的漏、源节点的正向偏置,提高谐振回路的品质因子值。

若MOS管M9导通,利用M7和M8把M9的漏、源高阻节点拉至地电位,保证M9在深线性区工作。为提高谐振回路的品质因子值,实现小的导通阻抗,宜选取较大尺寸的M9,当电源高电平直接作用在M9的栅端,其电源噪声会直接通过M9管耦合到谐振腔中,降低了谐振回路的品质因子值。为此,设计小尺寸的反相器电路,隔离电源噪声,使其不能直接耦合到谐振腔中,提高了谐振回路的品质因子值。

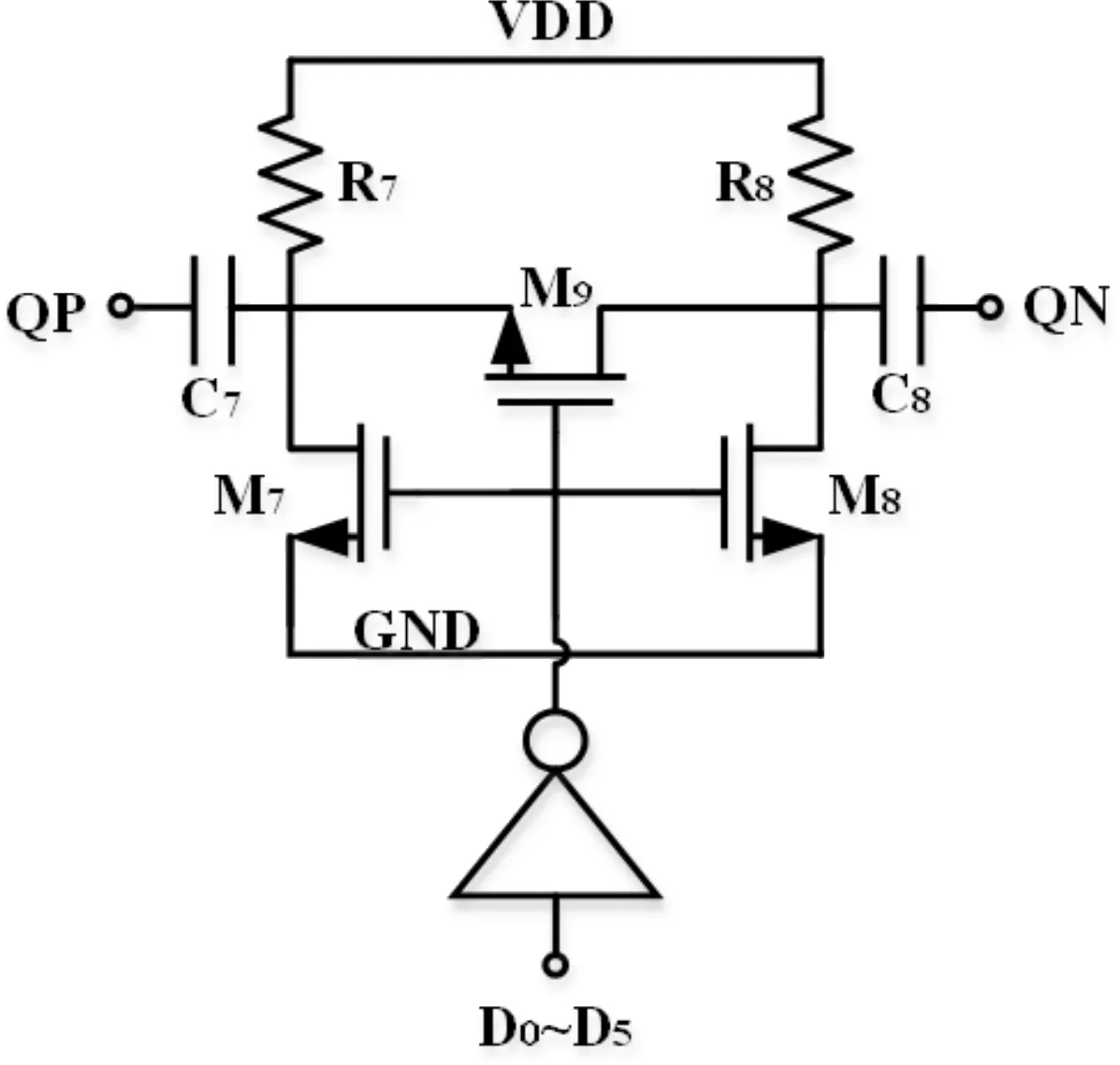

1.3 输出缓冲器

输出缓冲器设计,采用两路差分Buffer电路,用以抑制下一级电路所带来的频率偏移以及对核心电路相位噪声的影响。其结构如图5所示。

输出缓冲器由两部分组成。一部分是由隔直电容C9、反馈电阻R11、MOS管M10和M11组成的驱动放大器;另一部分是由MOS管M12、M13组成的反相器。驱动放大器通过反馈电阻R11实现输出信号轨到轨的传输,通过反相器驱动下级电路。

图5 输出Buffer电路结构

2 宽调谐范围的实现

6位开关电容阵列的宽带压控振荡器会致使电容版图布局面积的成倍增加、寄生电容急剧增大,流片后出现子带不交迭现象。为此,设计带有校准位的开关电容阵列以避免子带出现不交叠现象,其结构如图6所示。

图6 带有校准位的开关电容阵列结构

如图6所示,开关1—开关6为六位电容阵列开关,C0为最小比特位电容。为实现宽调谐范围,6位开关电容按照二进制形式排列。校准1—校准3为3位校准位,可以在2个不交迭子带之间插入多个子带,避免子带不交迭导致的宽带压控振荡器频率的不连续现象。

加入校准位的频率调谐曲线,如图7所示。虚线为加入校准3—校准1比特位为010后的频率子带,实线为由于版图寄生电容假设出现的2个刚好不交叠的频率子带。

图7中每1个子带的频率可以表示为

(3)

其中,Cvar为变容二极管电容,n为加入校准位后开关电容阵列中C0的个数。通过式(3)可以看出,n变化越大时,频率子带之间的间隔越大,当开关6—开关1的比特位从011111变化到100000时,由于版图寄生电容,可能导致开关电容阵列中加入的电容个数n从31C0直接变化到33C0,从而出现频率子带不交迭现象。通过设置校准3—校准1比特位为010,单独加入1个C0,校准后开关电容阵列加入32C0,从而避免了宽带压控振荡器中子带不交迭现象。

图7 加入校准位的频率调谐曲线

3 实验结果及分析

所设计的压控振荡器采用台湾积体电路制造股份有限公司(Taiwan semiconductor manufacturing company,TSMC)0.18 um工艺,通过流片测试验证电路仿真设计。流片后的测试芯片如图8所示。

图8 测试芯片图

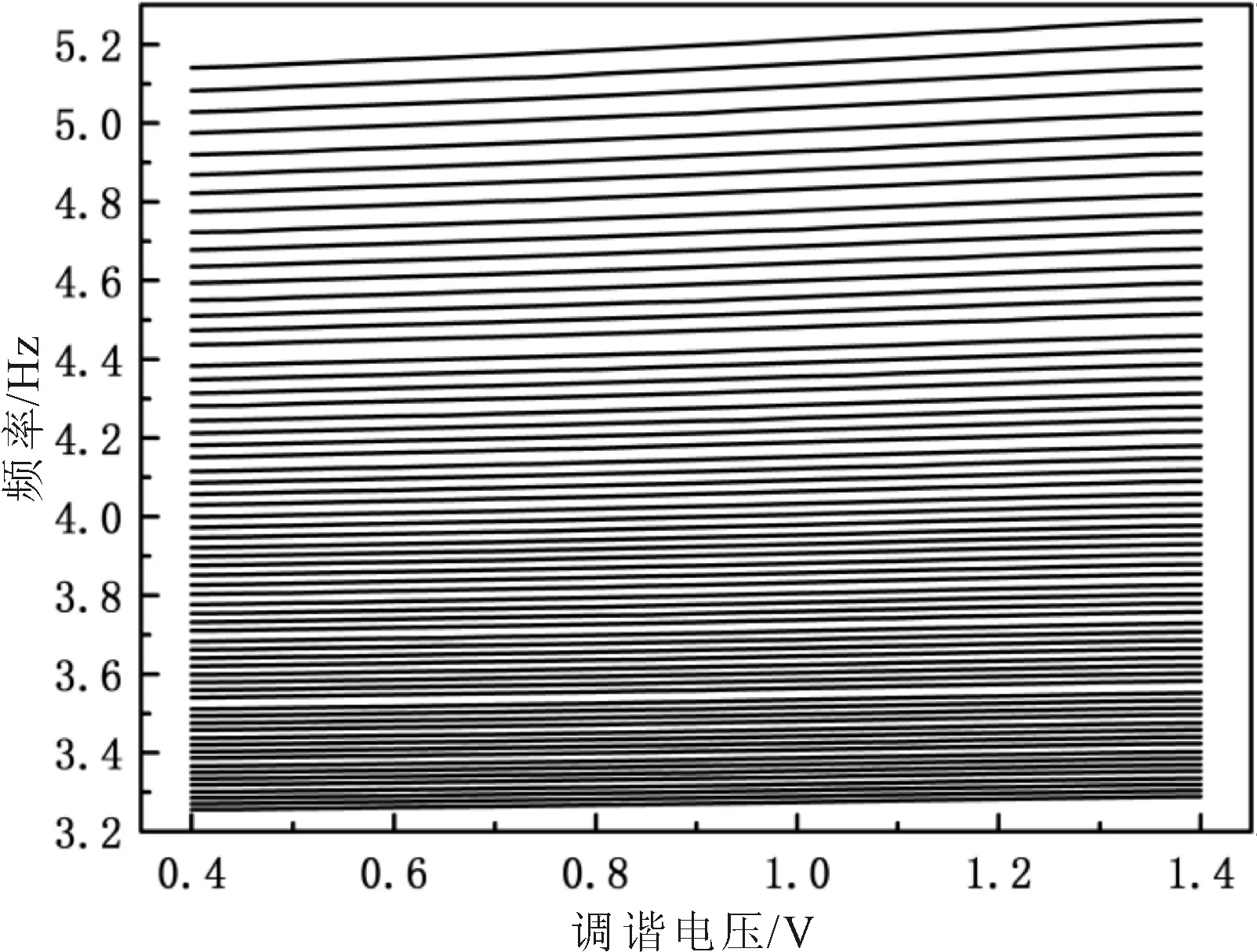

利用R&S FSWP频谱仪测试,得到VCO输出频率调谐曲线的测试结果如图9所示。

当控制位D0—D5从000000变化到111111时,频率调谐范围为47%,输出频率为3.26 GHz~5.27 GHz。在测试的64个子带中,中间2个子带交叠覆盖率仅为10%,这可能是由于第6比特的电容成倍增加,版图寄生电容随之增大,降低了流片后子带覆盖率。本文设计的3比特校准位,可以在校准1—校准3两个子带之间插入1个子带,子带覆盖率在50%左右,避免了温度漂移所带来的子带不交叠现象。

图9 VCO输出频率调谐曲线测试结果

利用R&S FSWP频谱仪测量得到的中心频率处的相位噪声。中心频率为4 GHz时的相位噪声测试结果如图10所示。

图10 中心频率4G时的相位噪声测试结果

从测试结果可以看出,VCO在频偏分别为10 kHz、100 kHz、1 MHz时相位噪声测试结果与仿真结果相差3 dB左右,可能是因为TSMC工艺中电感的实际品质因子值有所降低,导致流片后测试的相位噪声性能下降。

在温度27 ℃、1.8 V电源电压条件下,本文方法与文献[3]、文献[4]、文献[7]的VCO主要性能比较,如表1所示。

表1 本文方法与其他方法VCO性能比较

从表1中可以看出,在偏离中心频率1 MHz处,本文设计压控振荡器的相位噪声为-121.3 dBc/Hz。与文献[3]、文献[4]、文献[7]VCO相比,本文设计的压控振荡器在保证相位噪声性能的前提下,实现了3.26 GHz~5.27 GHz的宽频率调谐范围。

4 结语

设计并实现一款面向5G通信系统的宽带压控振荡器芯片。该芯片应用TSMC 0.18 μm工艺,采用6位开关电容阵列实现覆盖3.3~4.2 GHz以及4.4~5.0 GHz的全球5G通信频段,应用3比特校准位避免了宽带压控振荡器中子带不交迭现象。针对6位开关电容阵列结构带来的相位噪声性能的影响,设计中通过选取高品质因子值电感、应用二次谐波谐振滤波技术以及改进开关电容阵列结构,实现对相位噪声性能的优化。测试结果表明,在频率调谐范围上,与文献[3]、文献[4]、文献[7]VCO相比,本文设计的压控振荡器在保证相位噪声性能的前提下,实现了更宽的频率调谐范围。