基于FPGA和单片机的逻辑分析系统研究

逯玉宏,魏国庆,冉明昊

(重庆金美通信有限责任公司, 重庆400030)

1 引 言

逻辑分析仪是基于时钟捕获的用于测量数字电路中逻辑关系及逻辑波形的重要检测仪器,主要包含数据采集、存储和显示等部分。随着数字技术的高速发展,逻辑分析仪作为重要的检测仪器具有良好的发展前景和广泛的应用范围,在电子研发、工业控制、科研教学等领域发挥着重要的作用。目前,逻辑分析仪主要有独立式和虚拟式两大类别,前者功能强大但价格昂贵,而虚拟式成本较低、应用广泛,可在基于WEB 的仪器、便携式仪器、PC 等不同设备上运行[1-2]。

基于以上情况,研究设计了一种基于FPGA 并结合单片机的简易虚拟逻辑分析仪,通过实际测试能够实现常规逻辑分析仪的通用功能,能较好地满足电子工程应用和科研需求,具有良好的实用性。

从系统设计的总体方案的介绍入手,对软件设计做详细说明,最终得出可行性结论分析。

2 系统方案设计

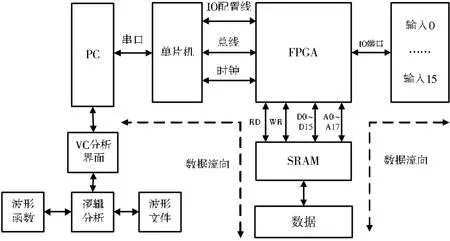

本系统设计的基本框架,包括XILINX 公司的SC3S1500 型号FPGA、SRAM 芯片CY7C1041 以及Silicon 公司的C8051F120 型单片机等硬件资源。系统整体结构如图1 所示。其中,FPGA 外接一个SRAM 存储器;C8051F120 单片机采用EMIO 总线复用的方式连接FPGA;0x0000~0x2000 地址段用于访问内部存贮器,0x2000~0x2020 地址段用于控制和存贮数据读取,实现1~16 通道数据采集和存储功能;单片机的输出主时钟作为FPGA 时钟,与此同时,单片机的串口0 通过max-232 电平转换后被连接到PC 机,并通过串口助手或者由VC 编写的分析工具,在PC 机上完成数据的逻辑分析和波形显示。

图1 系统结构框图

3 软件设计

3.1 FPGA逻辑设计

FPGA 程序采用VHDL 语言编写, 使用Xilinx ISE 14.4 编译,由总线接口(EMI0)、数据采集(LOGIC)、时钟(TIME)、存储器接口(RAM)等模块[3-4]构成。

总线接口模块负责控制指令和逻辑数据的传输。模块接收到C8051F120 的指令后,控制时钟分频比,采集数据宽度与时刻宽度,捕捉页面选择,启动/暂停所采集数据的传输。

LOGIC 模块实现数据的触发、采集功能。数据的采集过程是在主时钟的上升沿读取外部输入信号与上次比较不同时,按不同采集位宽叠加时间信息形成16 位数据写入SRAM,地址加1,准备下次写入。数据的采集取样率与时间基准无关。

TIME 模块是主时钟分频器,根据设定的时间单位控制分频比,形成不同时间基准。时间基准与波形的复现有关,太大或太小会造成波形失真。

RAM 模块实现采样数据的快速写入与顺序读出。FPGA 捕捉信号流程图如图2 所示。由流程图可知,输入信号每变化一次,记录存储一次,从而使存储空间得到最大程度的利用。

图2 FPGA捕捉流程图

3.2 MCU程序开发

C8051F120 是Silicon 公司提供的高性能8 位单片机,主频最高可达到100MHz,实现可编程主时钟输出,FPGA 配置文件压缩存储及配置,与上位机经过串口通信,完成逻辑分析的捕获参数设置,波形的复现,函数还原以及原始数据的上报等功能。PC机到MCU 控制的相关指令如表1 所示。控制模块的软件设计担负着全系统工作状态的控制和管理,是构成整个系统的极为重要的部分[5-6]。

波形的复现原理是:与数据采集相对应,记录数据时保存的时间信息与上次数据的差值就是上次波形延续的宽度。按行为单位,采用打印字符“ - ”(数据为1)、字符“ _ ”(数据为0)及回车换行的方式实现。一行可打印150 个字符,在行尾可选择打印地址信息。只要按照一定的规律逐行将波形一一复现出来,即可实现波形的分析。函数的可编程还原是在波形分析的基础上,识别出帧信号、时钟信号和数据信号,并结合相关文档分析得出的。利用时钟的边沿采集移位数据,在帧尾自定义函数名及参数格式打印。由于分析产生的数据量非常庞大,如果采用串口传输这些文本方式的波形将耗费大量时间,所以只需传输原始数据。具体分析功能由PC 端完成,波形复现程序流程图如图3 所示。

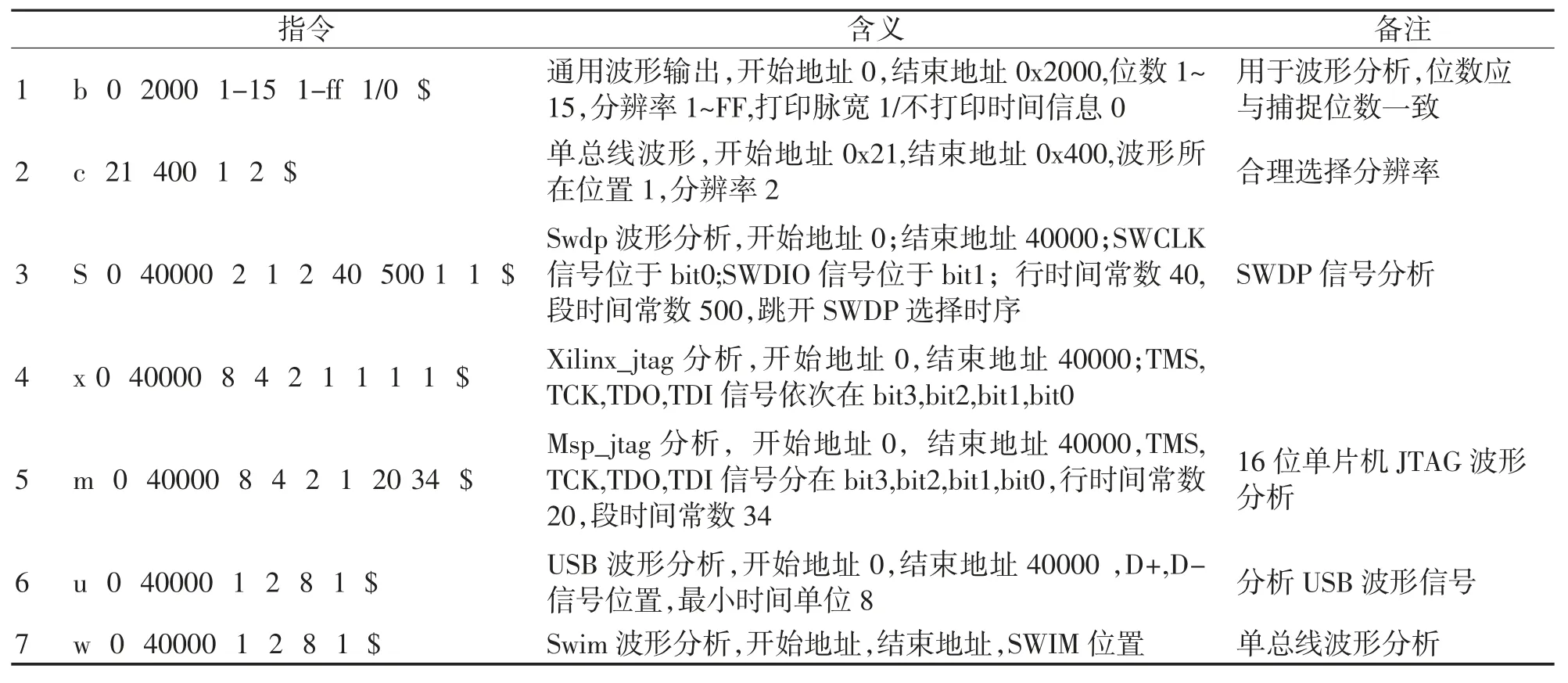

表1 PC机到MCU的捕捉及分析指令

3.3 PC端程序开发

PC 端的程序采用VC 编程来完成,将获取的原始数据还原成波形文本,方便上下行阅读对比分析。VC 方式开发的程序,在指令的下发需要行编辑,生成的文件还是自动保存为文本。以TXT 记事本的方式打开,便于波形分析时添加标志,编译后生成EXE 可执行文件。PC 端的分析工具analyse.exe 的界面如图4 所示,根据显示的提示符,输入不同的命令,即可获得文本文件,命令标志以“a”~“z”区分,参数为16 进制格式,以空格为间隔标志,“$”为执行标志,“#”为结束标志,相应生成的文件也以“a”~“z”命名保存。PC 端分析工具的相关指令汇总于表2 当中。

图3 波形复现流程图

表2 PC端分析指令汇总

根据图4 所示的PC 端界面命令提示,编辑输入命令:b 0 200 2 1 1 $,生成起始地址为0,结束地址为0x200, bit0, bit1 两路波形,最大分辨率带时间信息的波形分析文件b.txt,其原始数据与波形、时间对应关系如表3 所示。

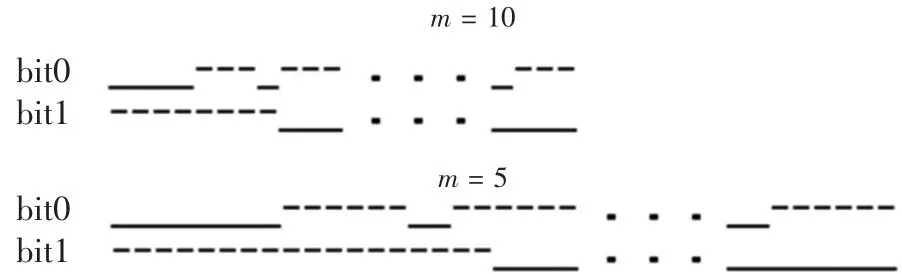

其中,Bit0 为接在逻辑分析仪输入0 脚的捕获值,Bit1 为接在逻辑分析仪输入1 脚的捕获值,以m个时间点(m ≥1)为基数复现一段波形,其波形对照如图5 所示。其中较短的一组对应m=10,较长的一组则为m=5。以Bit0、Bit1 说明数据位与波形对应关系,第一行Bit0,第二行Bit1,依次类推,每位数据占据一行,连续多行数据形成组,多组波形组合形成文本保存,便于手工分析时添加注释,手工分析清楚逻辑关系后,再次编程由电脑辅助分析数据。

表3 原始数据与波形、时间信息对应关系

图5 不同时间基准波形对照图

数据0 在波形中表示为“_”,相邻n 个“_”表示低电平持续n×m 倍时间单位;同理数据1 在波形中表示为“-”,相邻n 个“-”表示高电平持续n×m 倍时间单位。

图6 所示的USB 差分信号是采用0.01μs 时间单位捕捉到USB 串口的一段波形,由基础分析指令b 0 40000 2 1 1 $ 执行后生成b.txt 文件中局部截图得到。其中,数字8、9、25 等字分别表示所在位置高低电平持续了0.08μs、0.09μs、0.25μs;数字0 表示差分0,数字1 表示差分1。波形由再现的D+、D-两信号及时间信息组成,按USB 协议规定,差分信号1满足D+>D-,差分信号0 则有D->D+;EOP 持续2位时间的SE0 信号。根据此特征在analyse 源码中添加分析函数usb_analyse,识别NRZI 码,再转换为源码由u.txt 输出,达到智能可编程分析的目的。

图6 USB差分信号

由波形信息及USB 数据的传输规则[7-8],分析传输一段同步帧,NRZI 码为:

01010100010011101110101110110101

其NRZI 码波形信息转为源码是:

00000001100101100110000110010000

用16 进制表示即为“01966190”。

4 结束语

为降低成本、提高系统的灵活性而设计实现的此款基于FPGA 的数据采集存储逻辑分析仪,以其高速的输入性能,可有效保障数据的完整性,外加MCU 控制传递数据,并使用PC 机软件的分析方案,简化了电路设计的复杂度,使用非常方便。源码自动分析及存储功能也实现了友好的人机协作界面。经研究分析可确定:此款可编程逻辑分析仪上位机及逻辑分析仪实体可以组合运行,也可以单独运行,具有很强的灵活性和实用价值,适用于多种场合,尤其可在电子工程研究人员的工作中发挥重要作用。