基于软件无线电的通信系统实验平台研制(3) —控制 方 法

戴伏生

(哈尔滨工业大学(威海)信息与电气工程学院,山东 威海 264209)

0 引 言

基于类似Unix操作系统但可自由免费使用的开源无线电软件(GNU’s not Unix Radio, GNU Radio)[1],研制的无线通信系统实验平台,采用易于独立发展和便于操作的层级化管理和控制模式。顶层管理控制放在计算机当中实现。底层管理控制由实验平台承担,主要是对中频/射频模块进行管理与控制。在信号处理方面,实验平台负责中频信号的处理,计算机负责基带信号的处理。只有计算机和实验平台有机的结合,才能完成无线电系统功能。虽然,计算机与实验平台相互配合,通过GNU Radio软件能够验证很多应用无线电技术[2-6]。但是,若不掌握实验平台系统内部控制的原理和工作方式,就不能灵活应用该实验平台,验证的功能将局限于基带信号处理方面,很难开发出具有实质创新特色的无线电技术实验,更谈不上对实验平台无线电实现的技术进行移植,进而开发出可独立工作的软件无线装置,因此本文着重介绍所研制的无线电通信系统教学实验平台的控制方法。

1 数据传输协议栈及UDP端口定义

1.1 实验平台传输协议栈结构

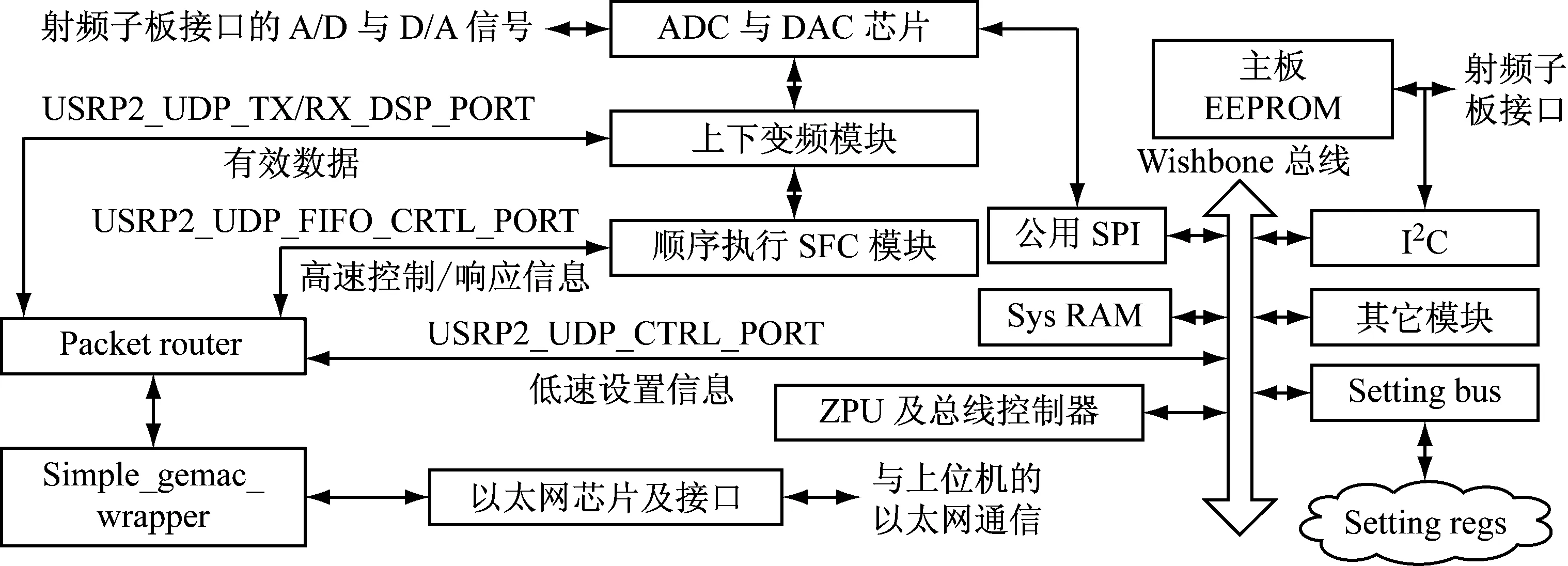

在实验平台XtremeDSP48A FPGA[7]构建的系统中,上位机和下位机均需对所要传输信息进行分类,若从信息的性质方面进行分类,则分为工作背景命令/状态和数据信息;若从信息需要处理的实时性方面进行分类,则分为低速数据和高速数据流。其中所有的数据信息均分类为高速数据流,而命令/状态信息既有低速数据流,也有高速数据流。实验平台上用FPGA构建的系统中对低速数据流和高速数据流的处理,所使用的传输协议栈在高层是有区别的,实验平台上用FPGA所构建的系统信息传输协议栈如图1所示。

实验平台上用FPGA构建的系统主要采用轻量级的网络协议(Light weight IP, LwIP)[8],低速控制数据包传输采用LwIP/UDP+(Application, APP)背景包协议结构,APP为实验平台上用FPGA构建的系统自定义的应用包格式[9]。高速信息流传输采用LwIP/UDP+(Vita Radio Transport, VRT)包协议结构。VRT是基于VITA-49协议规范定义的无线收发数据包格式[10]。由于VITA-49是专门用于软件无线电射频/中频设备网络方式的互操作性传输协议规范,所以VRT非常适合高速数据及高速命令状态信息的网络化传输。

图1 实验平台传输协议栈

1.2 实验平台中对UDP端口定义

为了更明确实验平台的处理流程,主要从信息流向角度介绍。下位机通过UDP/IP协议与上位机进行信息的传输,而在UDP协议的上层使用几种信息包格式,对应地在实验平台中的数据流也包括几种,如下主要介绍的是低速控制信息和高速信息包。低速APP信息包格式采用操作标识ID包格式;而高速VRT信息包格式中又含有两种格式,即数据包Data Packet和工作背景命令包Context Packet,分别对应在高速数据通道和高速控制信息通道上传输。

在千兆以太网的角度来看,其将上位机与实验平台的所有数据交互,都作为千兆以太网的有效数据,并通过UDP/IP协议在二者之间传输。当下位机将以太网数据拆包后,先根据UDP端口号区分是APP低速控制信息,还是VRT的高速有效数据或控制信息,并将不同数据发往不同的方向。图2体现实验平台系统设计上对内部对数据流向的控制思想。

图2 实验平台内部对数据流向的控制思想

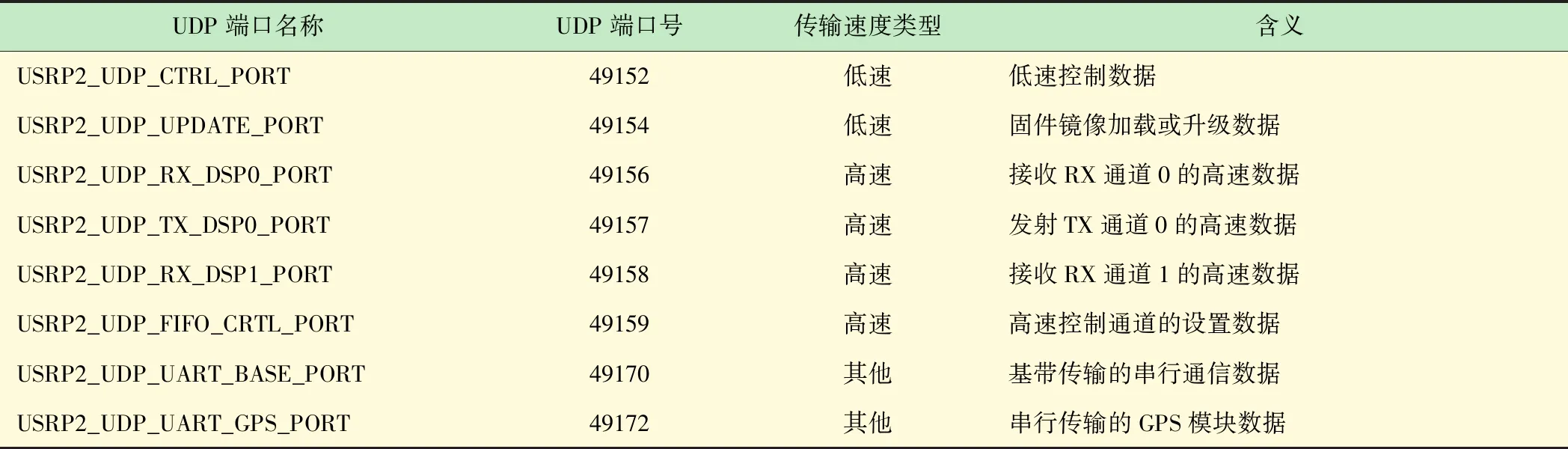

UDP协议使用端口号大于49151的端口号都代表动态端口,用户可以自己定义其对应的应用程序[11]。为了信息传输的需要,对UDP端口进行了定义,表1所示的是实验平台常用的UDP端口。

表1 实验平台主要常用的UDP端口定义

低速控制信息所涉及UDP端口号为49152,主要实现上位机与下位机之间的低速控制状态的设置和读取。对低速控制信息通道的数据处理,均需要片上系统中处理器(Zylin CPU, ZPU)[12]进行解析,然后根据解析出的操作要求,通过Wishbone总线[13],再控制相应功能模块及其子单元。UDP端口号49156~49159是高速数据及控制信息传输通道,这些端口传输的信息主要与数字变频,或者发送接收前端的高速设置寄存器Setting FIFO Control模块相关[14]。高速传输通道在信息传递过程中不需要ZPU进行解析,而是由Packet router解析包头后,直接送给相应的逻辑功能模块,实质上是时序逻辑的硬件动作。

2 低速控制信息的传输与工作方式

2.1 实验平台的低速控制信息格式

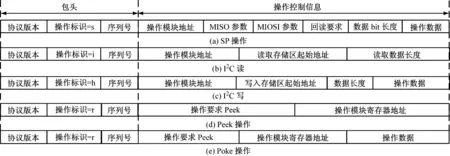

低速控制信息主要涉及五种操作,SPI的处理、I2C读、I2C写、窥探Peek、干涉Poke等。上位机给实验平台低速控制信息APP包格式见图3所示。由于实验平台返回给上位机的APP包格式与此相似,恕不需特别介绍。

图3 上位机给实验平台低速控制信息数据包格式

实验平台低速控制信息APP包格式中的包头与拟操作的功能模块相关,例如SPI的处理包,其操作涉及9个SPI芯片,为:主板A/D转换器、射频子板发射频率合成器、射频子板发射电路参数检测与调整用串行A/D转换和D/A转换器、射频子板接收电路参数检测与调整用串行D/A和D/A转换芯片器、主板D/A转换器、时钟管理器等。对SPI操作将用到挂载Wishbone总线的Settings bus功能模块,且在Settings bus之下的设置寄存器组SR_SPI_CORE,对应总线基组BASE地址为0X7050,SR_SPI_CORE中有3个设置寄存器,SR_SPI_CORE+0寄存器地址为BASE+0=0X7050,它负责设定SPI功能模块的工作时钟参数;SR_SPI_CORE+1寄存器地址为BASE+1=0X7054,它负责选择本次操作针对的是9个SPI芯片中哪个,以及要传输多少位数据和动作时序;SR_SPI_CORE+2寄存器地址为BASE+2=0X7056,存放准备传输的数据。

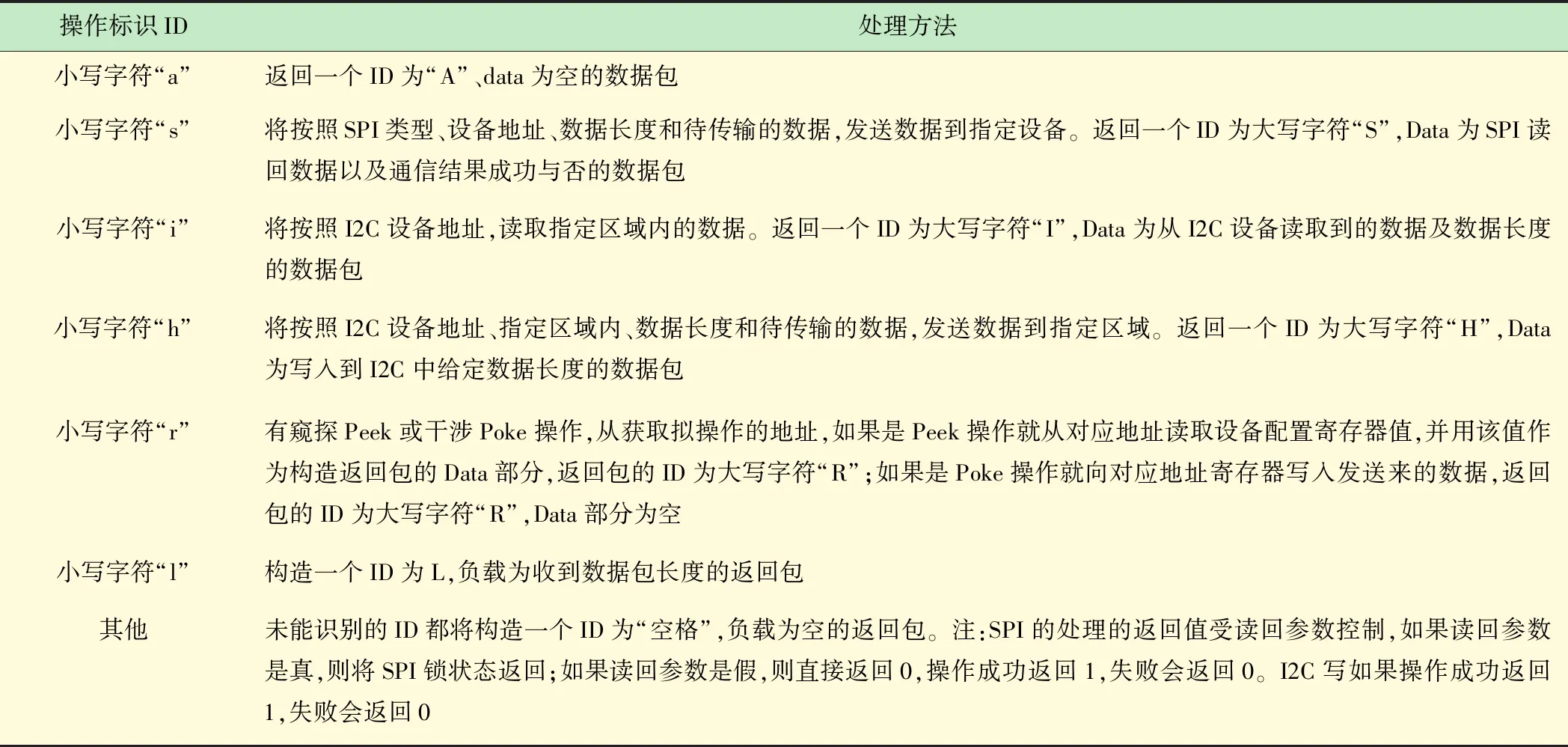

2.2 实验平台对低速控制信息的处理方法

由于ZPU是Wishbone总线的主控制器,对低速控制信息的处理,会涉及路由器模块Packet router与ZPU之间对总线操作的控制,所以需要进行总线资源属性的设置。Packet router给ZPU传送数据称为总线设置资源属性,反之则称为总线读取资源属性。总线设置资源属性时,ZPU将Packet router设置为写ZPU方式,Packet router对来自以太网的APP数据包头进行UDP端口识别,当端口号为49152即USRP2_UDP_ CTRL_PORT时,Packet router把APP数据送到总线。总线再把数据传给ZPU,ZPU进行APP数据解析,进而控制总线挂载的功能模块。总线读取资源属性时,ZPU将Packet router设置为读ZPU方式。Packet router读取ZPU中的资源信息,再把APP包加上相同的端口号49152即USRP2_UDP_CTRL_PORT包头后,然后把APP包通过以太接口送给上位机。

当实验平台接收到端口号为49152即USRP2_UDP_CTRL_PORT的控制信息时,总线处于总线设置资源属性,Packet router把APP包通过总线传给ZPU,ZPU对APP包中的操作控制信息数据处理方法见表2。ZPU给上位机返回信息时,总线处于总线读取资源属性,ZPU把VRT包通过总线传给Packet router,由Packet router给APP包添加UDP端口号49152后发送给上位机。

表2 低速控制信息在实验平台中处理方法

3 高速信息的处理方法

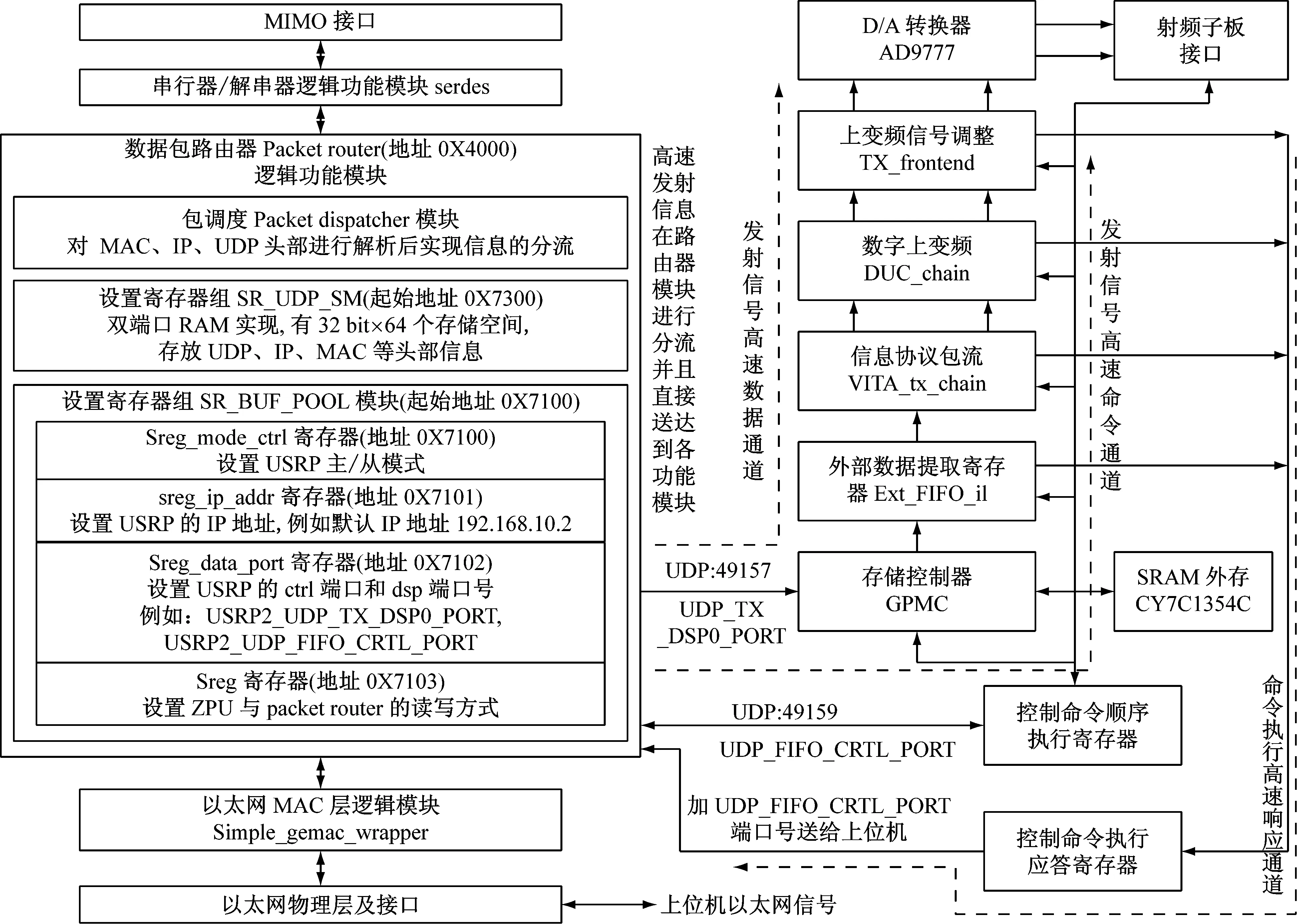

3.1 发射TX信息处理方法

实验平台对发射信息处理方法如图4所示。高速信息数据的来源有两个即以太网或MIMO,由设置寄存器组SR_BUF_POOL中Sreg_mode_ctrl寄存器的最低位决定。若设置该实验平台为主设备,高速信息数据来源以太网;若在多个实验平台级联使用时,设置该实验平台为从设备,则高速信息数据来源MIMO。文中以默认设置实验平台为主设备介绍。

高速信息包流从以太网传输到路由器Packet router模块时,路由器模块中的包调度Packet dispatcher模块,会根据VRT数据包UDP端口判断包流的类型。当UDP端口为USRP2_UDP_TX_DSP0_PORT时,就将其发往发射信号高速数据通道;当UDP端口为USRP2_UDP_FIFO_CRTL_PORT时,则将电路高速控制信息发往高速命令通道,即控制命令顺序执行寄存器。由于发射的高速数据量较大,实验平台中设计了一个9 Mbit SRAM作为突发数据的缓存,并采用了存储控制器(General Purpose Memory Controller, GPMC)[15],GPMC负责协调SRAM缓存数据与外部数据提取Ext_fifo_i1模块间数据输出速率。由于传输数据采用了VRT数据包格式,所以在数字上变频DUC前,需要通过VITA_tx_chain逻辑模块对信息包流进行包头和有效数据分离,分离出的包头信息将会确保数据和时序的正确性,有效数据在D/A转换前还需通过TX_frontend逻辑模块,对信号进行直流偏置工作、信号增益和相位等进行调整。

高速命令通道中的控制命令顺序执行寄存器模块,该模块内包含两个短的先进先出寄存器Short_fifo模块,分别用于存放控制命令和执行结果,主要负责读取输入的控制命令包而进行对应操作,并产生执行结果的VRT格式应答包ACK_packet。该应答包作为UDP的数据通过路由器Packet router模块加上USRP2_UDP_FIFO_CRTL_PORT包头后送给上位机。

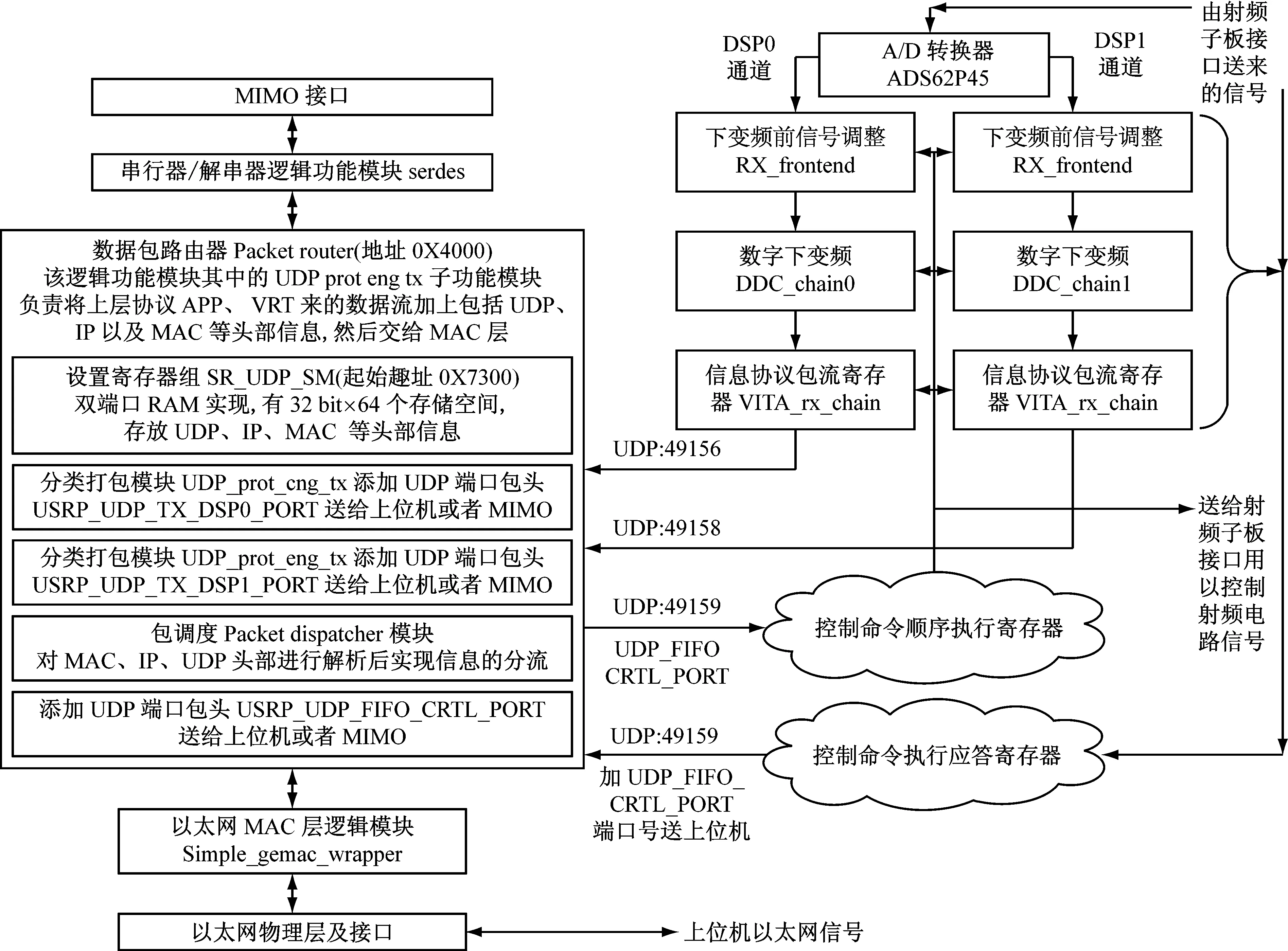

3.2 接收RX信息处理方法

对接收信息处理方法如图5所示。由A/D转换器输出高速采样的数据共有两路DSP0和DSP1通道,两路信号经RX_frontend逻辑模块对数字信号进行直流偏置工作、信号增益和相位等进行调整后,利用VITA_rx_chain逻辑模块进行VITA-49数据格式转换[16],添加包头等信息形成VRT规范数据包流。当传输到路由器Packet router逻辑模块时,路由器首先会根据数据来源,分别给数据包添加上UDP端口,若数据为高速采样数据来自数字下变频DDC0时,路由器会给VRT包添加上USRP2_UDP_RX_DSP0_PORT包头,而来自数字下变频DDC1时,则给VRT包添加上USRP2_UDP_RX_DSP1_PORT包头;若信号来自顺序控制应答寄存器时,路由器会把数据加上USRP2_UDP_FIFO_CRTL_PORT包头后送给上位机。

图4 实验平台对发射信息的处理方法

图5 实验平台对接收RX信息的处理方法

需要说明的是在批量数据发送或者是接收期间将用到一些设置寄存器组,如:路由器Packet router逻辑模块的设置寄存器组SR_UDP_SM、SR_BUF_POOL,数字上下变频逻辑模块DDC_chain和UDC_chain中的设置寄存器组SR_RX_CTRL0、SR_RX_DSP0、SR_RX_CTRL0、SR_RX_DSP1、SR_TX_CTRL、SR_TX_DSP,以及RX_frontend和TX_frontend信号调整逻辑模块中的设置寄存器组SR_RX_FRONT、SR_TX_FRONT等。这些设置寄存器中的参量都是通过低速控制信息Setting bus模块,需要利用ZPU进行事前设置,且在批量数据发送或者是接收期间,这些设置寄存器中的参量应保持不改变。

3.3 实验平台中的VRT包格式

实验平台的高速信息采用VITA-49规范构建了VRT包[10],格式如图6所示。其中,包类型的4 bit字段,实验平台定义3种,若为0001,则包类型定义为表示带有流标识的高速数据包;若为0100或0101,则包类型定义为表示工作背景和扩展背景包的高速命令包。

图6 实验平台中VRT包格式

VRT包格式中C字段用来标志数据包中是否含有类标识符,因实验平台没采用类标识符,故C置为0。T只对数据包起作用,标志VRT数据包中是否含有尾部,含有尾部T置为1。M只对背景包起作用,为0时表示使用精准时间戳。TSI字段标志数据包中使用的整数部分时间戳是UTC、GPS还是其他类型,由于独立工作的实验平台暂时无法获得电信联盟参考时间UTC,所以在实验平台暂不使用UTC,但是若给实验平台外配GPS模块,可设置TSI为10,否则TSI设置为11即其他时间标准。TSF字段标志数据包中使用小数部分时间戳的实时性定义类型。更多有关VITA-49规范建议将另文介绍,此处不再赘述。

4 结 语

对研制的无线电通信系统教学实验平台中低速控制信息和高速信息处理方法和工作特点,进行了系统地介绍。阐明了实验平台中低速控制数据流传输采用LwIP/UDP+APP背景包协议结构,高速数据流传输采用LwIP/UDP+VRT数据包协议结构,并根据UDP端口号区分低速控制信息和高速控制信息。区分后的信息发给相应功能模块进行相应处理。实验平台主板设计特点是通过接口对信息进行分类处理,并采用了层级化管理和控制方法。掌握APP低速控制信息和VRT高速数据及控制信息处理方法,不仅有助于对实验平台工作原理的全面理解,而且为进一步按照用户特定要求实施对实验平台特殊控制,开展个性化创新特色实验奠定了必要的基础。虽然,通过以上介绍对教学实验平台主板工作原理建立了系统工作的概念,但是,若要想充分发挥实验平台提供的资源,尤其是想开发出具有创造性的软件无线电应用,还需要掌握射频子板的工作原理。后续将对实验平台的射频子板工作原理,以及主板控制射频子板的方法进行阐述。