基于列车实时数据协议的以太网高速通信技术

赵辰阳 王立德 简 捷 李召召

(北京交通大学电气工程学院, 100044, 北京//第一作者,硕士研究生)

0 引言

随着车载智能设备和工业控制网络应用的扩展,列车通信网络(TCN)传输的数据类型和数据量在不断增大,传统现场总线技术已经难以满足列车通信网络不断提高的带宽需求。与此同时,列车的智能化程度越来越高,TCN的作用已经不只是简单的数据传输,还需要实现更多的功能,比如数据分类传输、网络故障诊断、优先级调度等。目前的现场总线技术已经成为限制TCN发展的瓶颈,随着以太网在工业领域的普及以及不断完善,基于以太网的TCN逐渐成为了研究的热点。

虽然工业以太网技术作为IEC 61375标准的新成员,已逐渐成为下一代TCN的潮流,但是工业以太网尚有一个重要的问题有待解决:工业以太网通信速率不高、带宽小,不能高速传输过程数据和消息数据。

已有学者尝试解决上述问题。文献[1]将列车实时数据协议(TRDP)应用到列车控制管理系统中,通过使用新型TRDP,来提高TCN的通信速率,解决以太网通信速率低的问题;文献[2]通过引入时分复用机制,提出了一种新的以太网列车的通信速率改进方法;文献[3]提出了一种新型的基于以太网的TCN系统,从控制策略入手进一步改进以太网列车速率低的问题。本文在已有研究的基础上,首先从总线接口入手,提出了一种片间总线通信协议,将片间总线通信速率提升至百兆左右;然后通过信号完整性分析,在硬件上,从反射问题入手,大大降低高速数据传输下信号波形发生畸变的概率,保证高速数据传输的可行性;最后提升TRDP传输过程数据与消息数据的性能。

1 片间总线接口技术

1.1 片间总线时序逻辑

本文提出的片间总线主要用在以FPGA(现场可编程门阵列)为主导的大批量、高速率数据的传输应用。

该片间总线所采用的是一种READY-V ALID握手通信机制。FPGA与ARM(高级RISC(精简指令集计算机)微处理器)进行数据通信之前,先根据操作对各所用到的数据、地址通道进行握手。主要操作包括FPGA接收到ARM的 READY 信号后,将数据与 VALID 信号同时发送给 ARM,这是一种典型的握手机制,如图1所示。

注:ACLK为片间总线时钟信号

本文设计的片间总线包含4组通道:读写地址通道、读写数据通道,以及相应的写应答通道和系统通道:

(1) 读地址通道:主要包含 ARVALID、ARADDR、ARREADY等信号。

(2) 写地址通道:主要包含 AWVALID、AWADDR、AWREADY信号。

(3) 读数据通道:包含 RVALID、RDATA、RREADY、RRESP 信号。

(4) 写数据通道:包含 WVALID、WDATA、WSTRB、WREADY 信号。

(5) 写应答通道:包含 BVALID、BRESP、BREADY 信号。

(6) 系统通道:包含 ACLK、ARESETN 信号。

其中,ARESETN为复位信号,低电平有效;READY与VALID是对应的通道握手信号;BRESP 与 RRESP 分别为写回应信号和读回应信号。其读写操作顺序如图2所示。

读操作顺序为主节点与从节点进行读地址通道握手并传输地址内容,然后在读数据通道握手并传输所读内容以及读取操作的回应,时钟上升沿有效;写操作顺序为主节点与从节点进行写地址通道握手并传输地址内容,然后在写数据通道握手并传输所读内容,最后再写回对应通道,并传输写回应数据,时钟上升沿有效。

本文有限状态机(FSM)的设计采用的是一种时序电路设计常用的设计方式,尤其适合设计数字系统的控制模块。FSM具有速度快、结构简单、可靠性高等优点。片间总线主要通过FSM对片间总线从进行相关的数据及地址访问。其读写状态的状态转移图如图3所示。

图3 读写状态的状态转移图

图3所示的状态转移图一共设置了8个状态,分别是复位(RESET)、读写初始化(RD_IDLE、WR_IDLE)、读写地址等待(RA_WAIT、WA_WAIT)、读写地址就绪(RA_START、WA_START)、读写数据等待(RD_WAIT、WD_WAIT)、读写数据进行(RD_PROC、WD_PROC)、写完成等待(WR_WAIT)及读写完成(RD_DONE、WR_DONE)。FSM按照此状态转移图过程对片间总线从写数据,实现FPGA到ARM端的数据传输。ARM到FPGA数据传输的过程与写流程相似。

1.2 突发模式逻辑

本文设计的片间总线协议基于BURST(突发)模式,主机只给出突发传输的第一个字节的地址。从机必须计算突发传输后续的地址,同时突发模式传输不能跨4 KB边界。其时序图如图4所示。

图4 突发模式时序图

在相应的箭头所指示的位置进行地址和数据的写入。其中读写地址使能、读写数据使能均在时钟上升沿有效,数据传输在WLAST(写完成信号)使能后完成,整个突发模式过程结束。对突发模式后续地址计算的参数如表1所示。

表1 突发模式计算相关参数

则有如下计算公式:

Start_Address=ADDR

Number_Bytes=2STZE

Aligned_Address=(INT(Start_Address/Number_Bytes))·Number_Bytes

Address_1=Start_Address

Address_N=Aligned_Address+(N-1)·Number_Bytes

已知ADDR = 0X0,SIZE=1,可计算出相应的Address_N =2 (N-1),以及每一次突发模式传输的地址偏移,并可以确认各个BURST读写的偏移地址从而完成整个突发模式的读写。

由于有突发模式逻辑以及有限状态机的支持,每次传输的数据字节可以大大增多。由于每次传输的数据量呈指数增长,传输速率大大提高。

2 以太网高速通信的反射问题

网卡设计有高速DDR(双倍速率)通路,且片间总线的通信速率在百兆左右,因此需要解决信号反射的问题,以保证片间总线高速通信的可靠性。

信号的反射一般以过冲以及振铃的形式表现出来,其存在会大大影响通信的信号质量,严重时,可能会导致信号无法传输。信号的反射和互连线的阻抗密切相关,反射的本质就是互连线中的阻抗发生了变化。只要互连线中存在阻抗不连续的点,该处就会发生反射。由于任何接收器都会有一定的输入电容,焊盘、封装等都会引入一定量的寄生电容。输入电容或者寄生电容就是容性阻抗不连续点,其到达接收器的时候就会产生相应的反射现象。不仅如此,容性负载还表现在类似于容性结构的负载,如芯片引脚较宽的焊盘、低速信号的过孔等都可以看做容性负载。例如本次设计的DDR电路,其采用的是桩线很短的菊花链拓扑结构,链路中的每一个接收器都相当于一个容性负载。其等效电路如图5所示。

注:R——电阻;C——电容

该类的容性负载位于传输线中间,设计该网卡的传输线阻抗Z0都是50 Ω,因此信号到达电容时就相当于通过一个25 Ω电阻进行充电。设入射电压最大值为U,则C两端的电压为:

(1)

式中:

t——信号到达电容的时间。

流过电容的电流IC为:

(2)

电容的阻抗Ze为:

(3)

本文τ取0.2 ns。当t为1 ns时,信号到达电容并开始对电容充电。当τ为0.2 ns时,电容电压上升到632 mV,该值是其终端电压的63.2%。

由于信号传播到电容时,感受到的阻抗是电容阻抗和后面一段传输线阻抗的并联,并联阻抗ZP为:

(4)

反射系数γ为:

(5)

如果设上升时间tr=0,则2 ns后容性负载的反射信号返回到发送端,反射、入射信号叠加口波形电压下降到0;之后,信号的电压按照指数的规律不断增加,上升时间由τ决定。

接收端容性不连续会使得高低电平叠加一定的噪声,信号到达接收端后由于接收端的高阻抗而发生反射,反射信号幅度与入射信号相同。反射信号到达中间电容时又会发生反射,电压为负。信号就这样在容性阻抗不连续点和其他阻抗不连续点之间不断叠加,会产生很大的噪声。

实际电路中不存在理想的传输线,也不可能完全匹配,因此信号反射是必然存在的。设计的关键在于如何把互连链路中的各个部件阻抗差距尽量缩小,从而减小反射信号幅度,避免多级反射对信号质量造成致命影响。实际电路中,在单端信号以及差分信号中做相应的阻抗匹配,例如单端信号按照50 Ω的阻抗匹配,差分信号按照100 Ω的阻抗匹配,从而使反射系数或者负载反射系数为0,以此来减弱或者消除信号的反射问题。同时,在实际电路中,1个驱动源驱动2个DDR芯片,且其拓扑结构采用的是菊花链拓扑,因此可采用串行端接的方式,在传输线源加33 Ω的端接电阻来抑制反射的增大。

3 TRDP的实现

3.1 TRDP

TRDP规定了TCN过程数据和消息数据在TCN中的通信流程。如图6所示,以标准以太网协议栈为基础,在传输层与应用层之间增加了TRDP层,能够为TCN中任意两个设备之间的过程数据和消息数据通信提供有安全性保障的端到端数据传输。与此同时,TRDP兼容标准以太网协议栈。

注:TCP——传输控制协议;UDP——用户数据包协议

TRDP由过程数据PD接口、消息数据MD接口、精简TRDP、虚拟操作系统VOS(软交换)和实用程序等构成。过程数据接口处理TCN上的过程数据,消息数据接口处理TCN上的消息数据。其中高级PD/MD接口包括调度、线程,以及过程数据和消息数据的触发等功能。实用程序部分包括数据的编组/解组、TRDP XML配置文件的读取、IP/URI地址转化、安全数据的传输,以及列车拓扑信息的访问等功能。VOS提供了与不同操作系统的接口,上层的应用程序通过调用不同的接口实现不同操作系统下的通信功能。

3.2 过程数据通信流程

TRDP规定了过程数据和消息数据的帧格式、通信流程,并提供了相应的接口函数。本文以过程数据为例,对数据传输模式进行分析。

过程数据的通信包括推模式和拉模式,其中主要的通信角色包括发布者Publisher、请求者Requester和订阅者Subscriber。

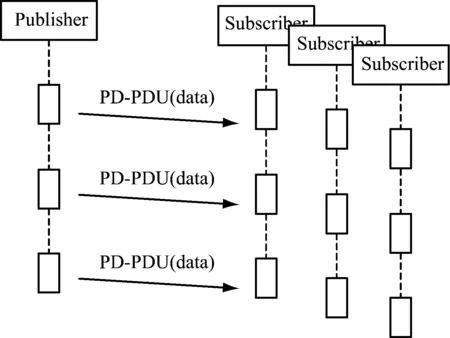

推模式是源端口按照固定的周期定时向订阅者宿端口发送过程数据,源端口作为发送数据的发布者,宿端口作为接收数据的订阅者,其通信方式如图7所示。

图7 推模式(一对多)通信方式

拉模式的工作模式为:由宿端口 sink 作为请求者并向作为广播者的源端口发送请求消息,源端口收到来自宿端口的请求回复消息之后,立即将待发送的数据回复给宿端口,此时宿端口作为订阅者,其通信方式如图8所示。

图8 拉模式(多对多)通信方式

Publisher作为数据的发送方,在推模式下循环发送过程数据PD,以及在拉模式下发送回复信息。同时在推模式下源端口按照固定周期定时向宿端口发送过程数据。Subscriber在拉模式和推模式中均为数据的订阅者。

4 试验测试与分析

本文设计的以太网卡硬件上使用赛灵思公司提供的ZYNQ系列芯片,型号为 XC7Z020-2CLG400I。该类型芯片采用FPGA+ARM架构,搭载双核Cortex-A9应用处理器AMBA,互连内部存储器、外部存储器接口以及外设[4-5]。其中,ARM系统及外设主要有:片上只读内存(Read-Only Memory,ROM)、256 kB片内随机存储内存(Random Access Memory,RAM)、2个千兆网卡以及片内ARM与FPGA之间的高带宽连接。FPGA部分主要有:逻辑单元85 000个、查找表53 200个、触发器106 400个以及JTAG(一种国际标准测试协议)调试接口1个。软件采用linux 3.82操作系统,TRDP功能用C语言编程实现。

ZYNQ(可扩展处理平台)下TRDP程序的编译需要遵循以下步骤:

(1) 编写测试程序,进行通信模式、通信量的配置。

(2) 编写Makefile(文件编写),定义编译规则。

(3) 配置环境变量并设置编译链。

本次测试是在2个嵌入式终端设备之间,进行一对一、点对点的 TRDP 过程数据通信测试。2个设备节点分别生成 28 个源端口,以及28个宿端口。本次测试中,数据帧内容包括本地IP、目的IP、数据发送周期以及数据长度,不同的端口通信周期设定为100 ms;数据长度设定为1 432 bit。

通过在TRDP以太网卡中产生相应的过程数据,将其存入DDR内存中的相应地址位置,同时在电脑终端显示器上显示过程数据发送的信息。利用逻辑分析仪,可以看到片间总线通过读取DDR内存,将ARM中的过程数据传入到FPGA,通过对比发送的过程数据,可以确认过程数据包发送的7C7C7C7C7C…在Chipscope(一款在线调试软件)上抓取出来,如图9所示。

图9 过程数据波形图

Wireshark是一个网络封包分析软件。Wireshark的功能是撷取网络封包,并尽可能显示出最为详细的网络封包资料。

以测试时100 ms下传输1 432 bit数据为例,单包数据传输速率设为13.98 kbit/s;通过Wireshark抓包软件进行统计分析,可以得出在传输过程数据时数据包的接收速率近似为6 590个/s。这样通过计算以太网每秒传输的包数乘以单包传输的bit数,最终就得出通信速率为94.36 Mbit/s。由于MVB(多功能车辆总线)、WTB(绞线式列车总线)、ARCNET(一种令牌总线网络)等其他铁路通信网络速率均不高于10 Mbit/s,通过对比明显看出基于TRDP下的数据通信速率远远高过MVB、WTB、ARCNET等铁路通信网络的的最高通信速率。

该测试状态为网络空闲时的状态。但以太网网速受多种情况的影响[6-8],比如:①测试时使用的TCP通信协议,容易出现数据延迟、数据错位以及数据丢失的问题;②网络质量差会导致设备之间延迟过高,通信不稳定。所以,其网建不能完全达到100 Mbit/s,但是也基本可满足列车通信速率的要求。

5 结语

本文结合FPGA与ARM,设计了符合铁路通信标准的基于TRDP的以太网卡。通过提出一种片间总线技术,从软件和硬件的角度入手,解决了以太网数据传输速率低的问题,有效保障了列车数据高速通信,为工业以太网应用于TCN又向前迈进一步。