一种8 Gsps模数转换器中的8B10B编码电路设计

张 博, 陶晓旭, 刘 宇

(西安邮电大学 电子工程学院, 陕西 西安 710121)

实际生产过程控制往往需要处理温度、压力和速度等连续变化的物理量,这些非电子信号的模拟量先要转换成数字量,才能够被计算机处理。模数转换器(analog-to-digital, ADC)通过将模拟信号转变为数字信号,成为连通模拟世界和数字世界桥梁的重要电子元件,倍受研究者重视[1]。

射频软件无线电结构中,采用超高采样速度ADC器件能够简化射频前端结构,但高分辨率和高采样率的ADC,不仅使芯片引脚设计变得复杂,板级布局和系统互联的成本变高,还对ADC的数据接口电路提出了更高的要求[2-3]。

JESD204B串行接口电路将采样数据映射成帧数据,在链路层完成码组同步、通道同步以及帧同步,再经过8B10B编码,最后以串行方式在高速通道上传输[4]。由于JESD204B串行接口电路采用8B10B编码保证了串行数据流的直流平衡,有助于实现接收端的时钟恢复技术,另外,8B10B编码中的特殊控制字符有助于多通道间的同步以及确定性延迟的实现[5],因此,JESD204B串行接口电路成为了高速ADC主流的数据接口电路之一。

8B10B编码器包括3B4B、5B6B编码两个子编码模块,其中3B4B编码需要5B6B编码的极性信息作为条件[6-7]。这种级联型编码实现方式的逻辑链较长,即便通过流水线将两个子编码模块进行寄存器分割,在每一级子编码过程中的极性计算也会带来逻辑延迟,从而限制编码传输速率。文献[8]采用单字节8B10B编码器实现了500 MSPS ADC的数据采集电路。单字节方案在一个时钟周期内只能处理一个字节,在ADC采样速度达到Gsps级别时,设计难以实现。

从实现方法上看,8B10B编码器的实现方法包括组合逻辑法和查找表法。基于组合逻辑法的电路结构复杂,限制了电路的最大工作频率,降低了通道传输速率[9];查找表通过消耗查找表资源实现编码,速度比组合逻辑快,且简便,适用于数据的高速传输[10]。

为了提高ADC的数据传输速率,本文拟提出一种应用于射频软件无线电的8 Gsps 12 bit ADC中接口电路8B10B编码器的改进设计方案。采用帧时钟域内的并行字节实现结构,以期减轻数据链路层的时钟负担;通过添加均衡指示位,简化3B4B、5B6B编码过程中极性信息的计算与传递;仅使用负极性编码结果减少查找表资源消耗,以期提高传输速率。

1 ADC中的编码器及其原理

高速ADC中JESD204B接口电路及现场可编程门阵列(filed programmable gate array, FPGA)的接收电路结构如图1所示。

图1 JESD204B接口电路结构

JESD204B接口电路包括了传输层、数据链路层以及物理层。传输层将转换器采样数据映射成各通道上的帧数据;链路层完成通道的建立及同步控制工作;物理层完成数据的串化,将串化后的数据经过电流模式逻辑(current model logic, CML)驱动电路传输至高速串行通道。

JESD204B协议中,8B10B编码器将从最高位到最低位依次为H、G、F、E、D、C、B、A的8 bit数据编码成从最高位到最低位依次为j、h、g、f、i、e、d、c、b、a的10 bit数据。记8bit数据为普通数据D码Dx.y或控制字符K码Kx.y,y代表高3位,x代表低5位[11-12]。JESD204B协议有K28.0、K28.3、K28.4、K28.5和K28.7共5种K码,其余为D码。Dx.7编码结果存在1110、0001、0111、1000四种情况,前两种用于普通D码编码,后两种用于D11.7、D13.7、D14.7、D17.7、D18.7和D20.7等6种特殊D码的编码[13]。8B10B编码原理如图2所示。编码器将输入数据分割为3B和5B,分别编码得到4B和6B。最终输出的10B码中,4B放在高位,6B放在低位。

图2 8B10B编码原理

为保证串行传输接收端恢复时钟的质量,传输序列中的1和0的个数要满足相对均衡,即直流均衡,要求每次编码间的10B码、4B码与6B码极性依次翻转。

极性偏差(running disparity, RD)简称极性,指示一个码值所具有的极性信息。一个码值中1的个数多于0为正极性RD+;1的个数少于0为负极性RD-;1的个数与0的个数相等为均衡状态。8B10B编码规定每个3B码、5B码输入对应的4B码、6B码有RD+和RD-两种极性结果。两种极性编码结果中,所有非均衡编码值与3B为011和5B为00111的编码结果按位取反就能相互转化;其余的均衡码两种极性结果一致。

根据前一次输出的10B码的极性信息先完成5B6B编码,并将6B码的极性信息作为3B4B编码的输入条件,最终完成8B10B编码,输出10B码值和极性信息。如此便完成了一次完整的8B10B编码。

2 ADC接口电路的编码器设计

2.1 参数设置

由于8 Gsps的采样速率较难直接实现,因此,为满足8 Gsps 12 bit ADC接口实现的需求及可行性,需要采用多相采样结构。若设备数量为16,则每个转换器设备采样速率为500 MSPS。需要将采样数据映射为帧,帧的长度为字节的整数倍,为降低设计难度,定义每帧中字节数为1。在传输层中,规定将每2个转换器设备的采样数据映射至3个通道上,则取采样数据通道数为24,多帧中的帧数为32,组帧数据中无控制字与控制位。这样,单个串行通道传输带宽为5 Gbps,即可实现链路层系统时钟频率500 MHz。

2.2 双字节并行结构设计

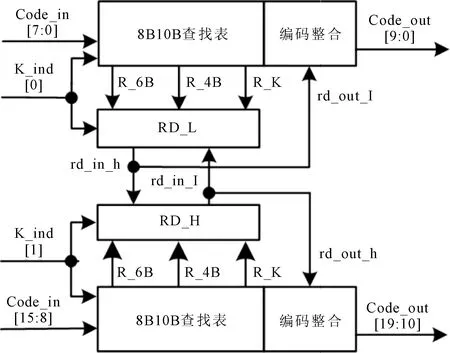

通过对字节间极性传递的处理,使用流水线设计了一种双字节并行的8B10B编码结构,如图3所示。

图3 双字节并行8B10B编码器结构

双字节输入数据Code_in与控制字符指示信号K_ind,按字节分为高字节Code_in[15:8]、低字节Code_in[7:0],进行并行编码。两个字节编码过程基本一致,经过8B10B查找表得到相应的预编码值与均衡信息R_6B、R_4B和R_K,根据当前编码值与前一个编码值的极性信息得到编码值,最终根据字节对应的控制字符指示位K_ind[1]、K_ind[0]输出最终编码结果。

高字节极性处理模块RD_H与低字节极性处理模块RD_L均在一个帧时钟周期内完成极性计算,这是并行字节编码实现的核心。图3中,高字节编码极性输出rd_out_h作为低字节极性输入rd_in_l,低字节极性输出rd_out_l是高字节的极性输入rd_in_h,高字节极性输出rd_out_h作为一个时钟内双字节的编码极性输出。

双字节并行结构实现了多字节编码中极性先于编码结果产生,能够一个帧时钟周期内得到多个字节的编码结果。本方案中电路的工作时钟为250 MHz,相比单字节编码电路降低50%。

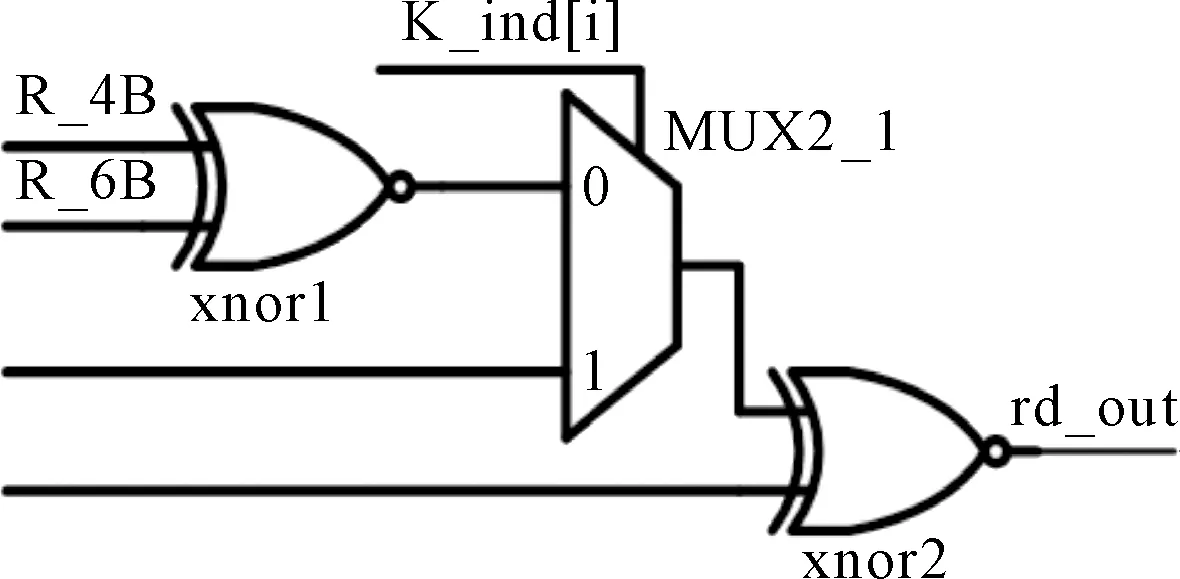

双字节间极性处理逻辑结构如图4所示。在相邻字节并行预编码时,若不考虑二选一MUX2_1的开关延迟,则字节间极性输出的逻辑延迟为一个异或门xnor2。

图4 双字节间极性处理逻辑结构

假设单字节编码极性输出的延迟为Ts,一个异或门的延迟为Tx,那么N字节并行处理的极性输出延迟为

Tm=Ts+(N-1)Tx。

这种流水线结构的关键路径,是第一级中产生最终输出极性。理论上N字节并行的传输速率可以达到10N/Tmbps[14]。

2.3 并联型8B10B编码电路设计

为提高编码器的工作频率,进而满足高速ADC的传输速率需求,需要解决极性信息计算与传递过程中关键路径过长的问题。根据8B10B编码原理分析,设计了改进型的8B10B编码器,包含了3B4B、5B6B和K码等3个编码子模块,极性处理模块RD和编码整合模块Code_gen。并联型8B10B编码器结构如图5所示。

图5 并联型8B10B编码器结构

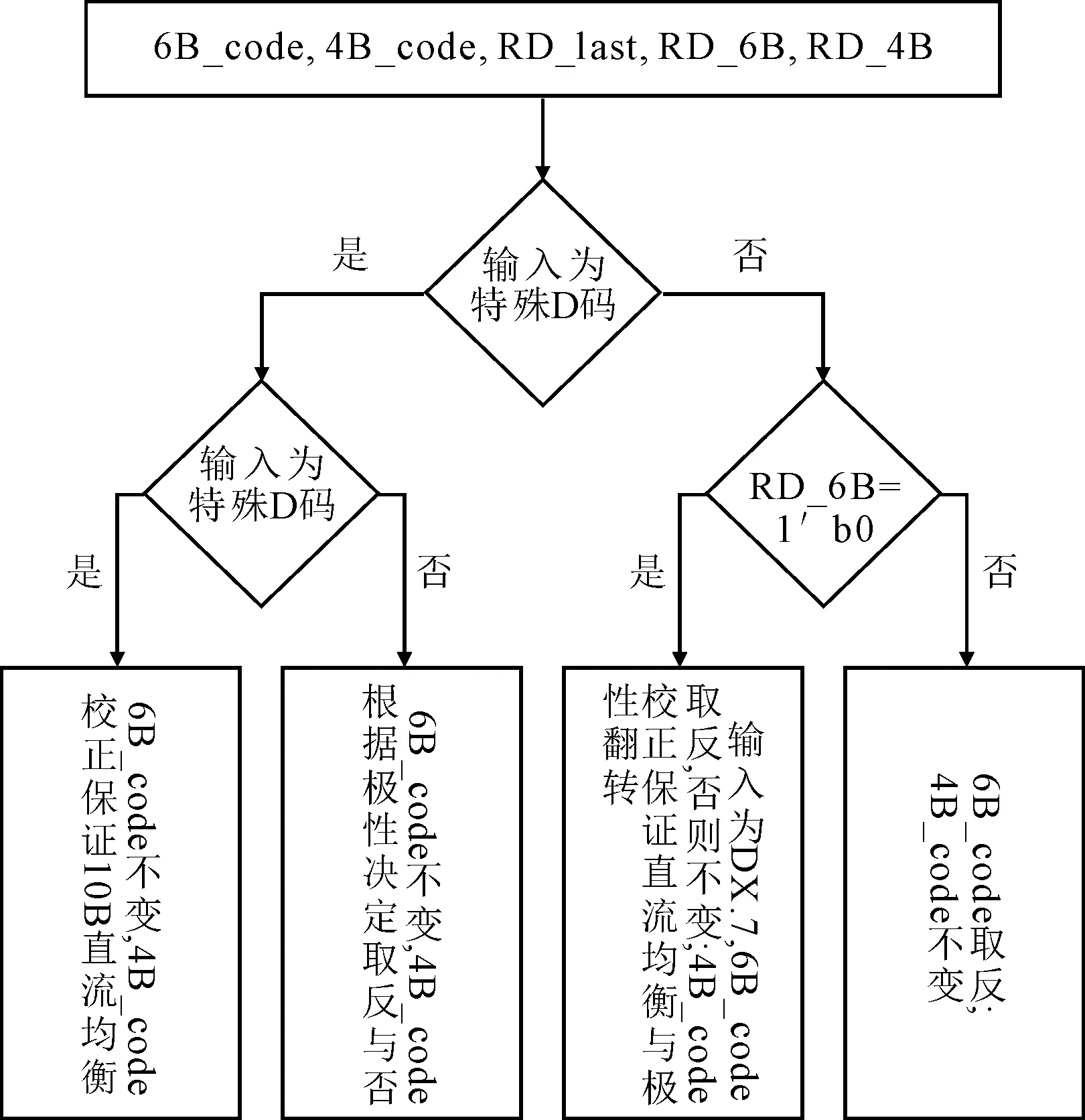

3B4B、5B6B、K分别对应3B4B编码、5B6B编码、K编码。这3个子编码模块独立并行地进行编码,产生对应的预编码值4B_code、6B_code、K_code以及均衡信息R_4B、R_6B、R_K。RD模块根据输入的控制字符指示位K_ind、编码模块输出的均衡信息以及前一次编码输出极性信息RD_in得到本次编码极性输出RD_new。RD_new与3B4B、5B6B编码模块预编码值进行编码输出的整合与特殊D码处理,得到D码编码值D_code。最后D_code与K_code经过一个二选一选择器MUX,在K_ind控制下得到最终编码结果10B码值。

因为3B4B与5B6B的编码模块输出结果均为RD-列的预处理编码值,不能直接输出,且需要对特殊D码进行处理,因此需要对预编码进行处理[14]。Code_gen模块根据预编码结果6B_code、4B_code,加上当前产生的均衡指示信息R_6B、R_4B以及上一次编码极性输出RD_last,在保证编码极性的依次翻转的原则下,完成D码最终编码值的输出。6种特殊D码也在此模块进行处理。D码编码产生原理如图6所示。

图6 D码编码产生原理

其中,直流均衡就是保证10B结果中0和1的个数相对平衡,最大不超过6个,最小不少于4个;同时,不能出现超过连续5个0或1。极性正常翻转要求两次10B结果、6B与上次的10B结果、4B与6B结果的极性信息依次翻转,即产生的极性可以与前一刻的极性相反或者为均衡码。

2.4 改进的查找表设计

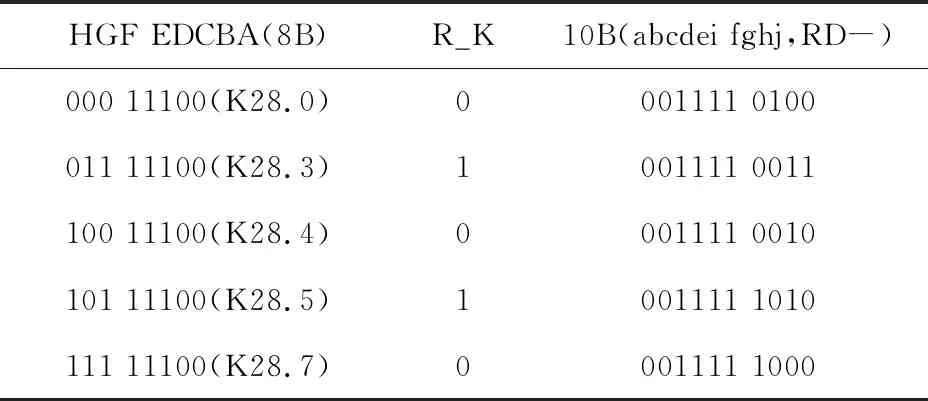

3个子编码均采用查找表法实现。在3个编码表中分别添加均衡指示位R_4B、R_6B、R_K。指示当前编码结果是否为均衡码,用于后续极性处理RD模块产生新的极性信息RD_new。当均衡指示位为1时,表示当前编码结果为均衡码;为0时,表示当前编码结果为非均衡码。K码、3B4B和5B6B编码表分别如表1—3所示。

表1 K码编码表

表2 3B4B编码表

表3 5B6B编码表

基于编码的RD+与RD-结果的关联性,每个编码表中仅使用RD-结果,查找表资源消耗减少了近一半。

极性输出RD_new的结果,由输入极性和均衡指示位通过简单逻辑运算得到。RD_new的逻辑运算关系为:

1)若当前输入码为K码,则

RD_new=RD_in⊗R_K;

2)若当前输入码为D码,则

RD_new=RD_in⊗R_4B⊗R_6B。

这样就在实现3B4B编码与5B6B编码并行处理的同时,减少了两个子编码模块极性计算与传递产生的逻辑延迟,能够显著地提高8B10B编码器的最大工作频率。

3 测试与分析

使用verilog HDL在vivado2017.1中进行电路设计,基于Xilinx的ZC706开发板,使用Xilinx自带的GTX高速串行收发器搭建了验证平台如图7 所示。

图7 验证平台

GTX收发器的差分参考时钟由AD9528提供,时钟频率为125 MHz。ZC706带有高速串行接口,外部闭环连接。禁用GTX发射端8B10B编码器,使能接收端8B10B解码电路,调用直接数字频率合成器DDS产生待编码数据,由设计的8B10B编码器编码后送至GTX电路中,经过并串转换、字符定界、串并转换以及GTX核的8B10B解码器后输出。调用FPGA器件的集成逻辑分析仪ILA,采集数据进行对比分析。测试环境如图8所示。

图8 测试环境

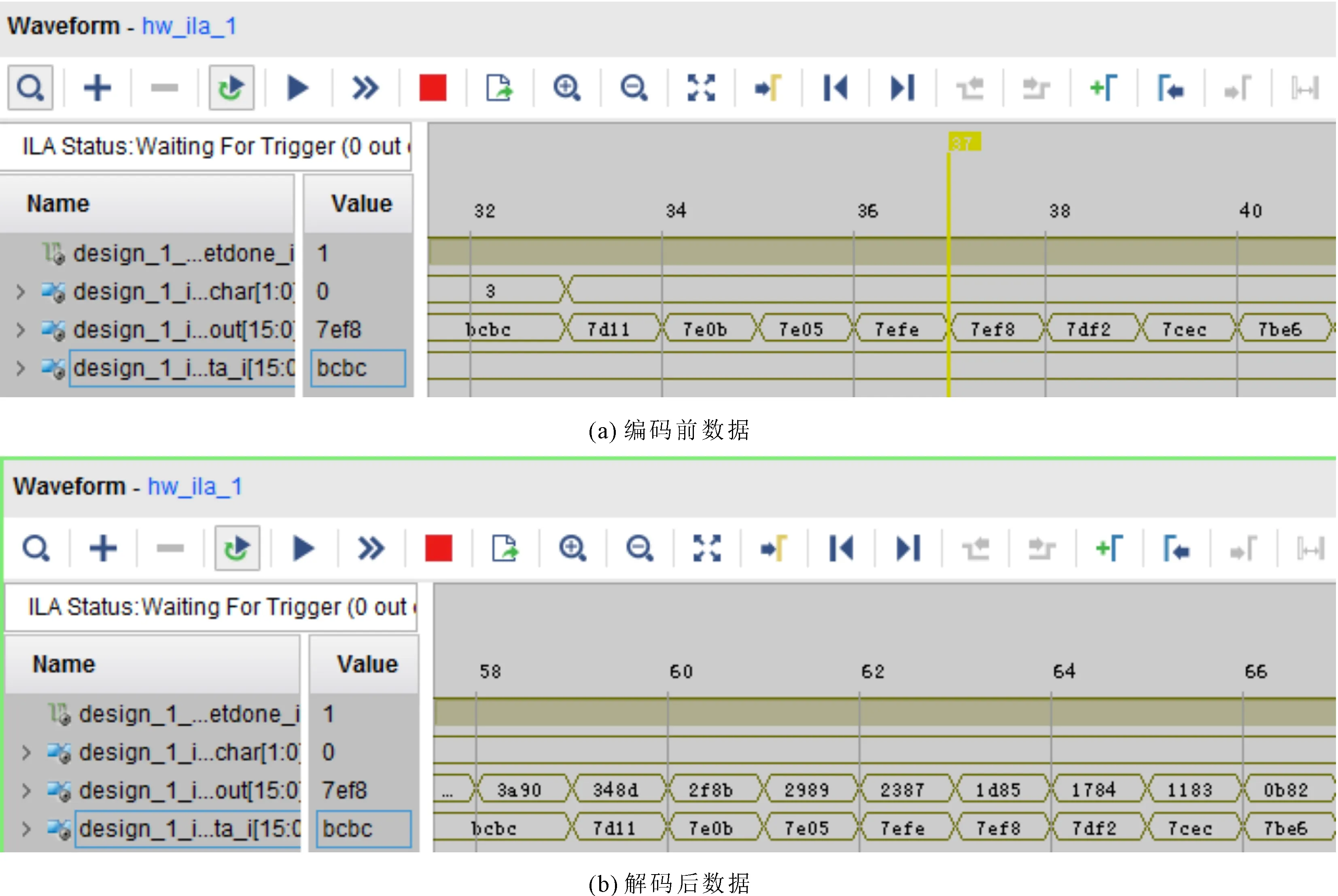

配置GTX相关参数,在传输速率为5 Gbps的条件下,采集编码前与解码后的数据分别如图9(a)和9(b)所示。

图9 编码前与解码后的数据

因为JESD204B电路中初始状态要进行码组同步,连续发射K28.5字符,且RX端字符定界也需要用到K28.5字符。因此,在输入测试数据前,需要加一段K28.5字符。经过对比图9(a)与图9(b)的数据可知,数据能够正确回环,证明了设计符合标准的8B10B编码规则,能够被标准的解码器正确解码。

本文设计的两字节并行8B10B编码电路支持的最大通道传输速率为12.9 Gbps,而文献[7]、文献[8]、文献[11]支持的最大通道传输速率分别为7.49 Gbps、8.24 Gbps和10.3 Gbps。本文编码电路支持的最大通道传输速率高于文献[7-8,11],这是由于通道传输速率由编码器最高工作频率和单位时钟周期内编码的字节数决定。文献[11]尽管采用了并行字节实现,但编码过程中采用级联型编码方式带来了极性的计算与传递延迟,限制了编码器最高工作频率;文献[7-8]一个时钟周期内只能处理一个字节的编码,编码效率不高。本文通过添加均衡指示位,简化了查找表资源消耗,优化了极性计算与传递带来的延迟,实现了一种并联型8B10B编码,提高了编码器最大工作频率;且通过两字节并行处理,提高了单位时钟内编码的字节数量。因此,本文的双字节并联型8B10B编码器能够支持更高的通道传输速率。

4 结语

设计了一种应用于8 Gsps 12 bit ADC接口电路中的8B10B编码电路。通过添加均衡指示位优化了极性信息的产生与传递方式;使用负极性编码减少查找表资源消耗;给出一种通用的并行字节处理方案提高通道速率,降低系统时钟需求。