千兆并行定时同步算法研究及实现

张永杰,孟庆凡,赵 煜

(1.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;2.中国人民解放军92493部队,辽宁 葫芦岛 125000)

0 引言

未来无线通信系统面临传统频谱资源短缺与无线业务需求爆炸性增长的瓶颈问题,拥有丰富可用频谱资源的毫米波通信成为下一代无线宽带通信的有效选择[1]。美国AIRLINX、日本NEC及俄罗斯Elva-1等公司推出了无线“虚拟光纤”——毫米波千兆无线设备,国内也开展了相关研究和设备研制工作,文献[2-7]重点对毫米波高速调制解调器进行了研究。作为千兆调制解调器的核心处理步骤,定时同步的精度直接决定了系统性能。同时,对于千兆量级的高速数据传输,现有处理器均不能支持实施串行处理。本文旨在结合实际工程指标,在现有硬件平台处理能力基础上,选择合适的信号处理架构与适宜工程实现的算法,完成毫米波千兆调制解调器中的定时同步研究。

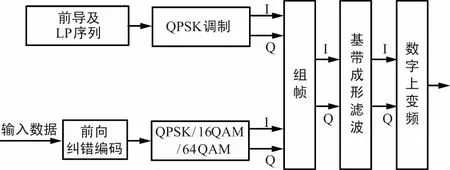

1 调制模块设计

调制模块主要完成输入数据的前向纠错编码、数据组帧、基带成形滤波和数字上变频等功能,图1为调制模块数字信号处理流程。

其中,前导序列和LP序列均采用IQ两路相同的QPSK调制方式,输入数据的调制方式为QPSK,16QAM,64QAM等可选。

图1 调制端数字处理流程

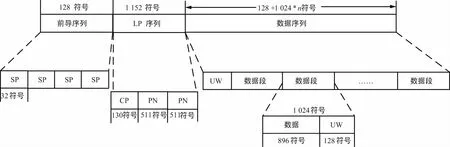

帧结构设计兼顾连续传输和突发传输,同时考虑系统时钟稳定度、载频捕获范围、宽带信号传输、抗多径能力和算法复杂度等因素。数据帧由前导序列、LP序列和数据序列3部分组成。数据帧组成图如图2所示。

前导序列由4个SP序列组成,每个SP序列由32个符号构成。根据SP序列的相关性,寻找相关峰得到SP序列的起始位置,可实现信号帧头预同步,为粗载波频偏估计做准备。

LP序列由两段511符号的PN序列及130符号的循环前缀CP组成,总长度为1 152符号,刚好为8的整数倍,方便并行结构处理。根据采样点和原始LP序列进行相关运算,依据相关峰可以精确找到LP序列的起始位置,同时可以根据序列的长度进行数据帧的精确划分,实现数据段的精确同步,为定时同步提供起始基准。

数据序列由n个数据段组成,n可根据编码方式、传输效率和信道变化选择。传输数据序列由帧头UW独特字和传输数据以及帧尾UW独特字组成,每个数据帧构成一个带循环前缀的数据帧,UW独特字长为128符号,每个数据帧传输有效数据896符号。

图2 数据帧组成图

2 并行定时同步算法

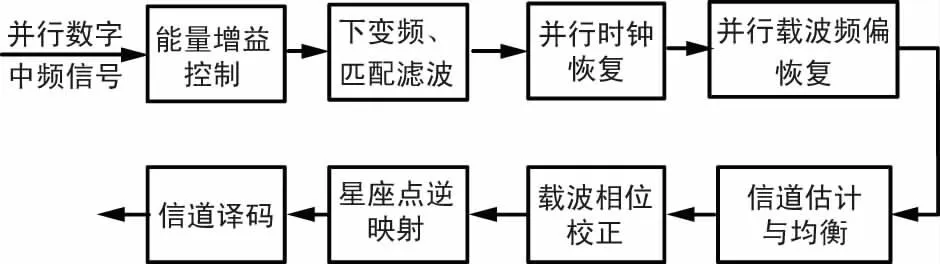

2.1 解调端信号流程

解调端数字处理流程如图3所示。A/D采样输入并行数字中频信号经能量增益控制、并行数字下变频、并行匹配滤波、并行时钟恢复、并行载波频偏粗估计、并行信道估计与均衡、载波相位纠正、星座点逆映射和信道译码后输出。由于系统数据传输速率较高,以上数字电路部分均采用8路并行处理。

图3 解调端数字处理流程

2.2 前向定时恢复算法

传统的定时同步方法主要有反馈式和前馈式两种[8],其主要区别在于同步环路是否构成闭环反馈结构。典型的反馈式同步算法为Gardener定时同步算法[9],其同步建立时间长,适用于连续通信[10]。典型的前馈式定时同步算法为非线性变换法[11],适用于突发通信,而且工程实现电路简单。

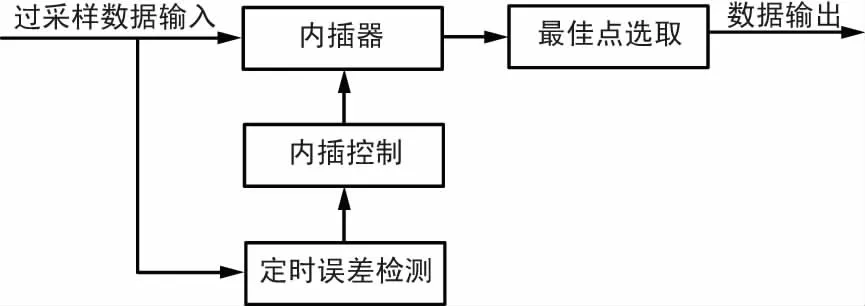

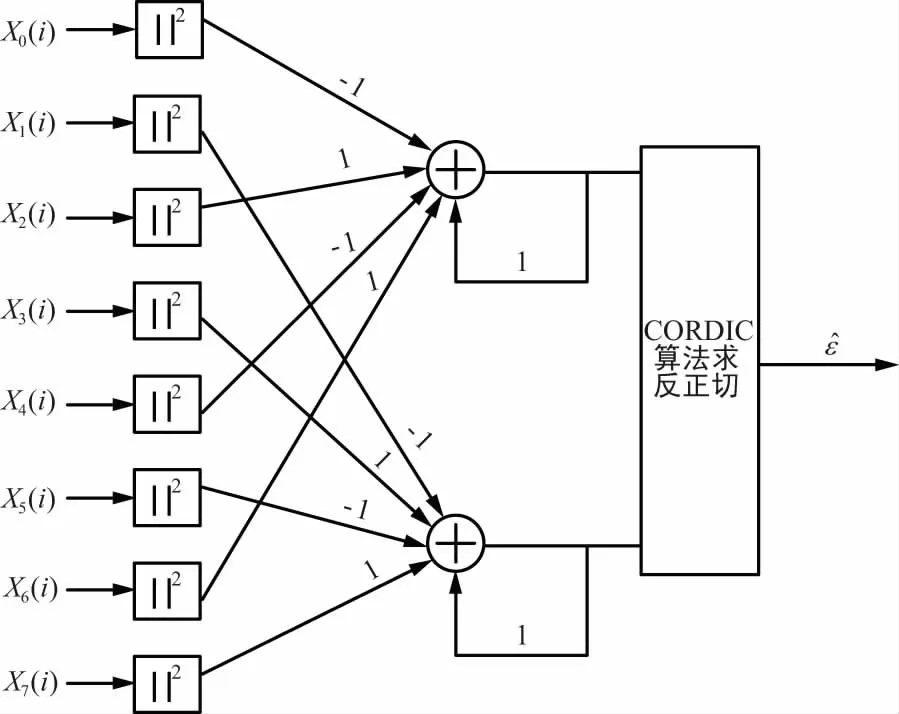

本文采用前馈结构的定时恢复算法,收敛速度快、解调延时也很小,能够独立完成每一帧数据的定时恢复,原理框图如图4所示。

图4 前馈结构定时恢复原理框图

采用Oerder.M和Myer.H提出的数字滤波平方算法[11],设符号周期为T,采样时钟Ts=T/N,对每接收到的LN个采样数据,先进行平方运算,然后计算傅里叶系数得到符号速率1/T处的频谱分量:

(1)

(2)

观察式(1)和式(2)发现,该算法对于载波频率和相位不敏感,可以先于载波恢复。若接收数据采用4倍过采样,则式(2)等效于

(3)

2.3 算法适应性分析

该算法对输入的LN个采样点(N倍过采样,符号数为L),统一计算得到一个采样时钟偏差,并用这个时钟偏差进行插值得到最佳采样点,然后每N个点选择一个最佳点作为输出。那么对于这L个输入符号,要求其第一个符号与最后一个符号的最佳点偏移不超过1/8,低信噪比条件下要求不超过1/32。如果定时恢复算法得到采样时钟偏差μ,第一个符号经过插值后得到最佳采样点,那么经过L个符号周期之后,由于采用时钟偏差的引入导致最后一个符号偏离最佳采样点1/4时,则最后一个符号的输出变成过渡点,因此采样时钟偏移的范围与输入的数据帧长度相关。输入数据帧长度越长,要求采样时钟偏差越小,否则第一个符号与最后一个符号的最佳点偏移越大。

2.4 并行定时恢复算法实现

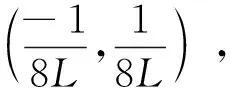

当N=4时,式(1)的运算可等效为通过传递函数为H(z)=jz-1/(1-jz-1)的IIR滤波器[13],可减少运算量。式(2)中求反正切运算采用标旋转数字计算(CORDIC)算法实现[14]。4倍过采样的8路并行数据定时误差检测实现框图如图5所示。

图5 八路并行定时误差检测实现框图

内插控制单元的作用是为8路并行内插器提供内插数据和内插滤波器系数。内插运算利用Ni个采样点计算出一个插值点时,内插控制单元提供长度为8+Ni-1的数据缓存区,将缓存区中的后Ni-1个数据依次移到最前端,从Ni个数据开始更新为输入的8个数据,其更新方程为:

(4)

式中,din(iTs)表示输入数据,dici(iTs)表示缓存区中数据。其输出给并行内插器的8路数据为:

rj(iTs)=dici[(i+j-1)Ts],

i=1,2,…,Ni,j=1,2,…,8,

(5)

式中,rj(iTs)表示输出给第j个内插器的第i个数据。

并行插值运算公式为[15]:

(6)

式中,hI为内插滤波器的时域响应[16-17],mn,j与μn,j分别为第j个内插器的插值估值整数部分与分数部分。8个并行内插器的输出与已知的UW相关,相关峰最大的作为输出[18]。

3 仿真验证

系统采用64QAM调制,数据传输符号速率为250 Msps。在接收端对接收信号采用近似4倍过采样fs/f=4.000 2,fs为采样速率,f为符号速率。载波频率偏差1.530 MHz(相当于0.613%符号速率,约0.153%采样速率),相位偏差70°。AWGN信道SNR=26 dB,对应于64QAM调制Eb/N0=18.22 dB。

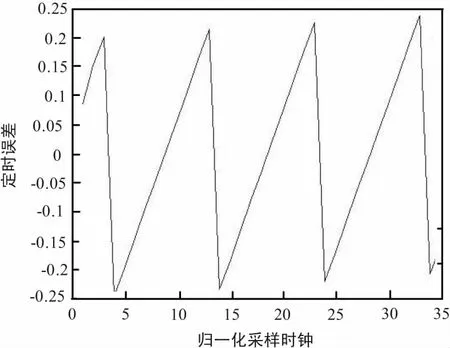

前向定时估计的仿真如图6所示,可以看到时钟偏差整体是逐步递增的,符合过采样率为4.000 2的情况。

图6 采样时钟偏差估计

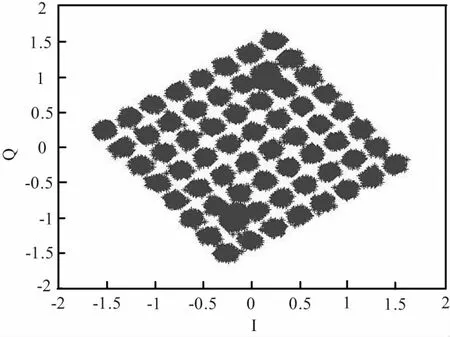

定时恢复之后星座图如图7所示,可以看出定时恢复良好,星座点已分离,只剩余相位偏差。

图7 定时恢复之后星座图

4 结束语

本文主要采用多路并行处理、前馈定时恢复结构以及数字滤波平方算法,完成了毫米波千兆调制解调器中的定时同步研究。从工程实现角度,设计了调制端的数据帧结构和解调端的并行定时恢复实现方式,分析了算法对采样时钟稳定度的要求。该研究解决了千兆突发传输的快速定时同步问题,以及实现复杂度与硬件处理能力间的矛盾,已在实际中得到成功应用。