扇出型晶圆级封装技术及其在移动设备中的应用

郭昌宏,李习周

(天水华天科技股份有限公司,甘肃 天水 741000)

扇出型晶圆级封装即Fan Out WLP或FOWLP(英文全称为Fan-out Wafer Level Packaging),其采用拉线出来的方式,成本相对便宜,FOWLP可以让多种不同裸晶,做成像WLP制程一般埋进去,等于减一层封装,假设放置多颗裸晶,等于省了多层封装,有助于降低成本。此时唯一影响IC成本的因素就是裸晶的大小。

对于目前和下一代移动的设备,需要超薄和高密度封装技术的支持。扇入封装类型被称为晶圆片级芯片规模封装(Wafer Level Chip Scale Packaging,简称WLCSP),即晶圆级芯片封装方式,以前一直是智能手机的首选技术,该封装提供相对较小的外形尺寸和占地面积。但不足之处是WLCSP往往只有有限的I/O数量(约200根),而且最小封装尺寸为0.6 mm。在处理音调缩小时,CSP由于可用于I/O布局的区域仅限于裸片,所以面临表面处理挑战。然而,扇出封装作为该技术没有这种限制,允许将I/O重新分配到芯片表面以外的模具上反过来支持更薄的封装到0.4 mm[1,2]。

1 FOWLP技术简介

晶圆级封装可分为扇入型和扇出型,如果封装后的芯片尺寸和产品尺寸在二维平面上是一样大,芯片有足够的面积把所有的I/O接口都放进去,就采用扇入型。如果芯片的尺寸不足以放下所有I/O接口时,就需要扇出型,当然一般的扇出型在面积扩展的同时也加了有源和/或无源器件以形成SiP。

1.1 FOWLP发展的促进因素

轻、薄、短、小已经成为电子消费品的发展方向,这样既能省掉材料及工序,又能减少元器件尺寸的晶圆级封装工艺步骤。随着技术变得越来越先进和创新,智能手机越来越薄,并且采用更大、更高清晰度的显示器,同时提供更高速度的连接和更好的整体功效。所有这一切只是为了满足我们对更快、更高科技设备的永不停止的需求,并具有最长的电池寿命。先进的封装技术,特别是FOWLP,使制造商能够通过使用封装创新克服关键的处理难题来实现这些功能。

1.2 FOWLP工艺流程

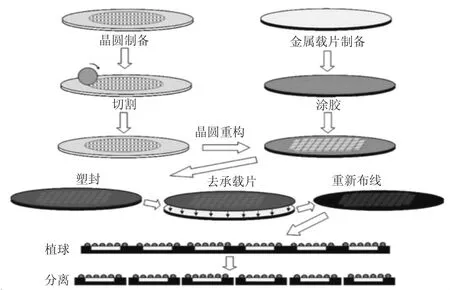

FOWLP的工艺步骤主要有晶圆的制备及切割、制模等,其工艺流程如图1所示。

图1 FOWLP工艺流程图

1.3 FOWLP技术特点

从技术特点上看,WLP主要分为扇入型(Fan-in)和扇出型(Fan-out)两种。传统的WLP封装多采Fan-in型,应用于引脚数量较少的IC。但伴随IC信号输出引脚数目增加,对焊球间距(Ball Pitch)的要求趋于严格,加上印刷电路板(PCB)结构对于IC封装后尺寸以及信号输出引脚位置的调整需求,扇出型封装方式应运而生。扇出型封装采取拉线出来的方式,可以让多种不同裸晶,做成像WLP工艺一般埋进去,等于减一层封装,假设放置多颗裸晶,等于省了多层封装,从而减小了封装尺寸和降低了成本。FOWLP技术完成凸块后,不需要使用封装基板便可直接焊接在印刷电路板上。

比倒装芯片球栅阵列(FC-BGA)封装,FOWLP技术优势非常明显。对于无源器件如电感、电容等,FOWLP技术在塑封成型时衬底损耗更低,电气性能更优秀,外形尺寸更小,带来的好处就是散热性能更佳,在相同的功率分配下工作温度更低,或者说相同的温度分布时FOWLP的电路运行速度更快。

在FOWLP技术中,铜互连形成在铝PAD上,应用于扇出型区域以制造出高性能的无源器件如电感和电容。与直接封装在衬底的片式(On-chip)电感器相比,厚铜线路的寄生电阻更小,衬底与塑封料间的电容更小,衬底损耗更少。以3.3 nH的电感为例,65 nm的CMOS采用On-chip封装方式其品质因子Q为12,而FOWLP则可达到高峰值42。电感与塑封料越接近损耗因子越小,Q值越高。当然,如果电感直接与塑封料接触性能最佳。

FOWLP封装方式中“消失的”的基板层减小了整体尺寸,切断了芯片通往基板的热流通路径。总体来讲,FOWLP的热电阻比传统多芯片组件(MCM)低约14%。(前者为28℃/W,后者为32.5℃/W),从而带来最大9℃的温度差异。

2 FOWLP在移动设备中的应用

移动设备,尤其是智能手机在我们的日常生活中无处不在。它不再被认为是手机,而是可携带的个人电脑。据报道,将近80%的智能手机用户平均全天花费132 min的时间进行通信。支持如此高水平的活动,智能手机必须提供最佳的性能。

2.1 可靠性

对于微处理器,最佳性能表现为优化的可靠性,包括热性能和电气性能。产品或组件的可靠性性能最终决定了设备的使用寿命,以及它能够在一段时间内快速,并一致地同时执行多项任务。因此,任何封装的一个关键指标就是电气性能。如果将多个芯片嵌入单个FOWLP中,与其他封装技术相比,整个电气路径更短,从而实现更快的信号传输。

此外,可以实现更多与印刷电路板(Printed Circuit Board,PCB)的物理连接更好的热流,这对热性能至关重要。功率耗散对于有效地去除使用IC时产生的热量是必要的,因为功耗较差导致的过热会导致IC故障和破坏。这在热处理成为问题的移动设备中尤为重要。

如前所述,在FOWLP中,凸块不依赖于芯片表面,因此通过实施更多的RDL来扩大电气连接可以实现更高的I/O密度。在最先进的扇出封装中,为了最大限度地提高I/O密度,最多可以同时使用四个 RDL(Redistribution Layer),从而有助于提高电气和散热性能,包括功耗[3]。

2.2 I/O密度

RDL用作I/O布局的重新路由并启用更高的I/O数量。高I/O密度通常会有更好的电气性能,因为更多的输出会导致芯片之间更快的电信号,并将电短路带来的风险降至最低。较高的I/O密度也使封装能够并行执行更多操作。因此,高I/O数量允许封装更复杂及高速的芯片。

2.3 更多功能

智能手机为用户提供更多功能更强大的存储空间,触摸屏,语音识别,高性能CPU,更长的电池寿命以及运动传感器。然而,这种趋势对IC和封装制造商构成了挑战:如何在薄型智能手机中融入更多功能?答案是整合,有多种方法可以使用FOWLP来实现这一点。通过嵌入来实现异构和均匀集成更多的集成电路和被动元件在同一个封装体内,并且利用更复杂的元件封装架构。一个示例是多芯片封装,其中多种功能的多个管芯嵌入同一封装内的模制化合物中。另一种实现更高集成度和功能的方法是使用封装级封装,如台积电在最新iPhone型号中使用的信誉良好的FOWLP封装(APE上的DRAM)。还有许多其他扇出式封装技术采用2D,2.5D或3D架构以实现最大程度的集成[4]。

2.4 更小的外形

下一代智能手机需要更密集的封装,这可通过晶体管扩展(摩尔定律)或使用创新封装技术的高级集成来实现。通过模具嵌入的实施,结合精细特征使用晶圆处理的可能性,FOWLP将形成高密度封装所需的RDL数量降至最低,同时不会受到过度的成本损失。由于RDL可以在整个覆盖模具区域形成,因此可以完全不需要IC衬底或内插器,这相对于传统封装技术而言大大降低了形状因数。通过集成,特别是通过在同一封装体内嵌入多个裸片并使用创新的封装架构,外形因素可以进一步降低。FOWLP技术可使封装厚度减少20%。Yole Développement估计,与标准倒装芯片封装相比,FOWLP提供的封装外形尺寸减少至少40%[5]。

2.5 FOWLP存在的问题

技术优势和市场预测表明,FOWLP会成为下一代移动设备首选的先进封装技术。虽然FOWLP可满足更多I/O数量之需求。然而,如果要大量应用FOWLP技术,首先必须克服各种挑战问题:

(1)焊接点的热机械行为。因FOWLP的结构与BGA结构相似,所以FOWLP焊接点的热机械行为与BGA的结构相同,FOWLP中焊球的关键位置在硅晶片面积的下方,其最大热膨胀系数不匹配点会发生在硅晶片与PCB之间。

(2)晶片位置精确度。在重新建构晶圆时,必须要维持晶片从拾取及放置(Pick and Place)于载具上的位置不发生偏移,甚至在铸模作业时,也不可发生偏移。因为介电层开口,导线重新分布层与焊锡开口(Solder Opening)制作,皆使用光学光刻技术,掩模对准晶圆及曝光都是一次性的,所以对于晶片位置之精确度要求非常高。

(3)晶圆的翘曲。人工重新建构晶圆的翘曲(War page)行为也是一项重大挑战,因为重新建构晶圆含有塑胶、硅及金属材料,其硅与胶体之比例在X、Y、Z三方向不同,铸模在加热及冷却时热胀冷缩会影响晶圆的翘曲行为。翘曲是基于扇出技术的关键挑战。当使用较薄的封装时,除了异质材料和更多铜层之外,晶圆弯曲在加工之后发生。晶圆弯曲是晶圆上应力分布不均匀并影响成品率的结果。为了克服这个问题,必须优化晶圆制造工艺和扇出设计流程。

(4)胶体的剥落。在常压时被胶体及其他聚合物所吸收的水分,在经过220~260℃回流焊(Reflow)时,水份会瞬间气化,进而产生高的内部蒸气压,如果胶体组成不良,则易有胶体剥落的现象产生。

(5)模具移位。模具移位是另一个工艺难题,它是指放置在载体晶圆上和包覆成型过程中模具轻微移动。然而,对于基于晶圆的技术来说,模具移位是一个挑战,随着对面板格式的期望过渡,模具移位变得更加关键,因为处理大方形格式一致和精确模头定位的设备尚未得到验证。基于面板和面板的扇出封装的主要关注点,模具移位影响产量[6]。

3 结束语

FOWLP被描述为一种颠覆性技术,FOWLP技术优势众多:通过嵌入方式提高可靠性和更多的RDLs;通过更多功能和更高级别的集成多芯片嵌入和复杂的架构;通过减小形状因子创新的架构;无衬底嵌入技术降低了制造成本。FOWLP被视为实现这些功能的理想技术选择,它改变了封装外形。外包半导体装配和测试供应商(OSATS),集成设备制造商(IDM)和代工厂都将进一步采用[7]。