基于TEC-XP16教学机的扩展指令研究

宗德才, 王康康

(1.常熟理工学院 计算机科学与工程学院,江苏 常熟215500;2.江苏科技大学 数理学院,江苏 镇江 212003)

0 引言

“计算机组成原理”是计算机专业重要的核心基础课之一,在整个计算机专业教学中起着承上启下的作用[1]。该课程具有涉及面广、抽象性强和学习难度大的特点,其实验教学有助于对抽象理论的理解,因此,必须对该课程实验教学环节给以足够的重视[2]。

目前,我校“计算机组成原理”实验教学内容主要是基于清华大学计算机系研制的TEC-XP16 计算机实验系统而开展进行的。与大多数高校一样,该实验教学内容,主要停留在验证性实验部分,为了使学生更好地掌握计算机的各个组成部件的工作原理,理解指令的执行流程,系统地建立计算机整机概念,培养学生的设计、创新能力,培养学生对计算机系统的分析、应用、设计及开发能力,需要开发一些设计性实验。为此,我们在该实验系统上,以扩展六条指令为例介绍了在TEC-XP16教学机组合逻辑控制器中扩展指令的主要过程,并以扩展SWRR指令为例,详细介绍了如何在控制器的源文件中添加扩展指令的控制信号的逻辑表达式、编译控制器的源文件、对MACH器件进行编程、编写程序验证扩展指令是否正确的整个过程。以此作为TEC-XP16实验系统的设计性实验。

1 组合逻辑控制器的组成及其原理

根据指令步骤标记线路和控制信号产生线路不同的组成和不同的运行原理,有两种控制器:组合逻辑控制器和微程序控制器。

组合逻辑控制器采用组合逻辑线路、依据指令及其执行步骤直接产生控制信号。

微程序控制器采用存储器电路把控制信号存储起来,依据指令执行的步骤读出要用到的信号组合。

TEC-XP16 教学机中同时实现了微程序和组合逻辑两种控制器[3]。

组合逻辑控制器由程序计数器PC、指令寄存器IR、节拍发生器Timer 和控制信号产生部件CU 4 部分组成[4]。PC用于提供待读出指令在主存储器中的地址,IR 用于保存从主存储器中读出的指令内容,Timer 用于给出并维护指令执行步骤的编码(节拍状态编码),控制信号产生部件用于依据指令内容(在IR中)和指令执行所处的操作步骤(节拍状态编码),用组合逻辑线路产生计算机本操作步骤中各个部件所需要的控制信号。TEC-XP16 教学机中的组合逻辑控制器主要是由 MACH 器件实现的。

在教学机中,组合逻辑控制器发出的32位控制信号中控制运算器的控制信号有23位I8I7I6、I5I4I3、I2I1I0、A3A2A1A0、B3B2B1B0、SST2SST1SST0、SSHSCI1SCI0,控制内存或I/O接口的控制信号有3位_MIO 、REQ、_WE,控制内部总线数据来源的有3位DC1_2、DC1_1、DC1_0,控制专用寄存器接收的控制信号有3位DC2_2、DC2_1、DC2_0[5]。

2 设计组合逻辑控制器的扩展指令

在TEC-XP16教学机中,两种控制器的主要功能线路都集中到一片高集成度CPLD 器件(MACH芯片)中实现,在完成扩展指令的实验中,可以不对 MACH 芯片之外的电路作任何变动,全部操作都集中到修改描述 MACH 芯片功能的 ABEL 或 VHDL 语言的程序代码,执行编译和下载操作以及运行调试这样几步工作。MACH 器件内部实现的电路,都是通过设计描述其功能的逻辑表达式体现出来的,这些逻辑表达式的分段清晰,实现的功能彼此独立,可读性比较强,设计与变更设计容易,不必过多处理功能线路之间的布线连接,可以保证更高的实验效率。设计描述MACH 芯片所实现功能的程序源代码是设计控制器的主要工作[5]。

在现有的 TEC-XP16 教学机中,描述控制器功能的ABEL 语言源文件只实现了组合逻辑控制器一种控制器,并且只实现了29条基本指令。本文在此基础上设计实现了六条扩展指令:

ADD1 DR,SR、MVRT DR,SR、NOT DR、LDRA DR,[ADR]、SWRR DR,SR、SWRM DR,[SR]。

2.1 设计条件

(1) 硬件条件:TEC-XP16 教学机、PC机、Lattice USB 下载电缆HW-USB-2A;

(2) 软件条件:Lattice ispLEVER Classic 2.0软件、WinPcec软件;

2.2 扩展指令的具体过程

在TEC-XP16教学机的组合逻辑控制器中扩展指令的具体过程如下:

(1)确定这六条扩展指令的格式和功能,如表1所示。

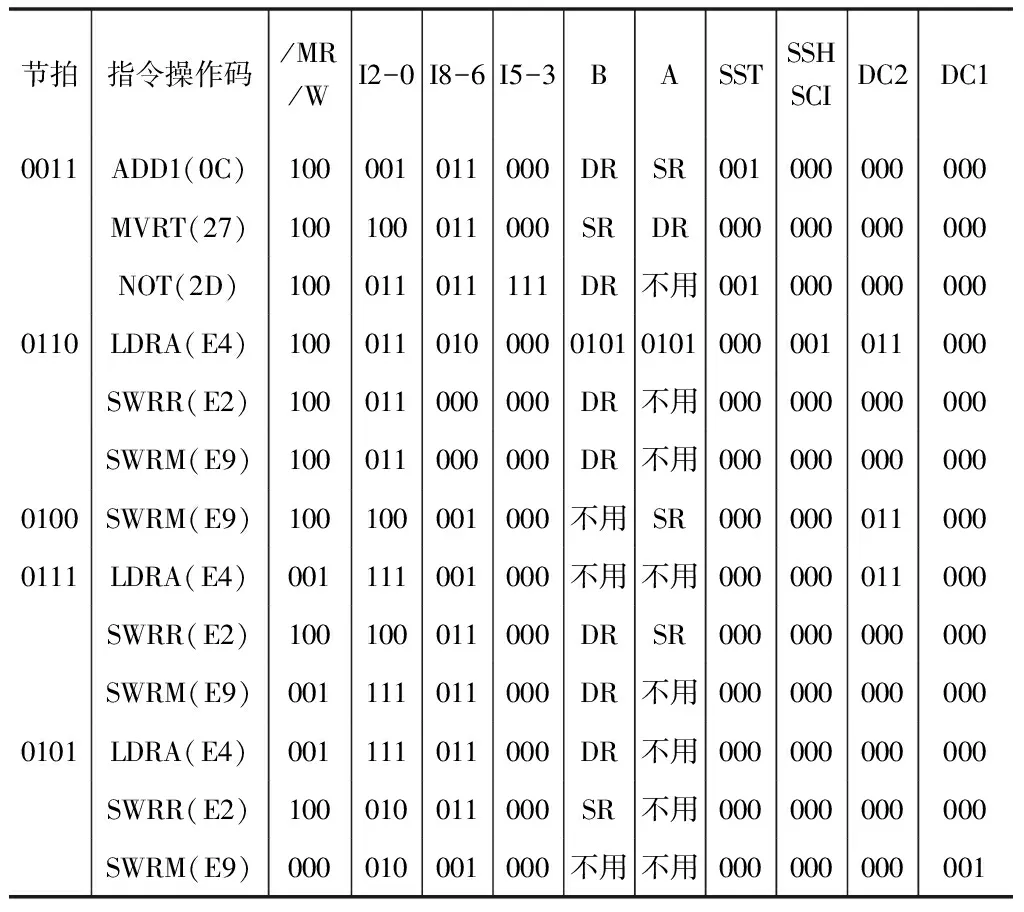

(2)划分指令的执行步骤并设计每一步的执行功能,设计节拍状态的取值,如表2所示。

指令ADD1属于A组指令,实现的功能是DR+SR→DR,实现的功能与ADD指令相同,但是操作码与ADD指令不同。执行A组指令只需一个节拍即可完成,0011节拍完成DR+SR→DR。

指令MVRT属于A组指令,实现的功能是DR→SR。执行A组指令只需一个节拍即可完成,0011节拍完成DR→SR。

指令NOT属于A组指令,实现的功能是/DR→DR,即将DR寄存器内容每一位取反。执行A组指令只需一个节拍即可完成,0011节拍完成/DR→DR。

指令LDRA属于C组指令,所对应的二进制指令为1110 0100 DR0000 ADR,实现的功能是DR←[ADR],即读出教学机主存中地址为ADR的内存单元中的内容送至DR寄存器。执行C组指令需要三个节拍: 0110节拍完成PC→AR,PC+1→PC,0111节拍完成MEM→AR,即读出教学机主存中以寄存器R5(教学机中PC即R5)的内容为地址的内存单元中的值ADR送至寄存器AR,0101节拍完成MEM→DR,即读出教学机主存中地址为ADR的内存单元中的内容送至DR寄存器。

表1 六条扩展指令的指令格式与功能

表2 六条扩展指令的执行步骤表

指令SWRR属于C组指令,实现的功能是DR与SR的值互换。执行C组指令需要三个节拍:0110节拍完成DR→Q,0111节拍完成SR→DR,0101节拍完成Q→SR。

指令SWRM属于D组指令,实现的功能是DR与[SR]的值互换,即将DR寄存器的值与教学机主存中以寄存器SR的内容为地址的内存单元中的值互换。执行D组指令需要四个节拍:①0110节拍完成DR→Q,0100②节拍完成SR→AR,③0111节拍完成MEM→DR,即读出教学机主存中以寄存器SR的内容为地址的内存单元中的内容送至DR寄存器,④0101节拍完成Q→MEM,将寄存器Q中的内容写入教学机主存中以寄存器SR的内容为地址的内存单元中。

(3)根据表2,在指令执行流程表中填写节拍状态以及每个节拍状态下各个控制信号的状态值,如表3所示。注意:表3中指令操作码用十六进制数表示。

(4)在现有的MACH器件的ABEL语言源文件中添加所设计的扩展指令的控制信号的逻辑表达式,编译适配后下载到 MACH 器件中。

表3 六条扩展指令的执行流程表

(5)写一个包含所设计的扩展指令的程序,通过运行该程序检查执行结果的正确性,验证设计的扩展指令是否正确。

在控制器的ABEL源文件中扩展指令时,先添加一条扩展指令的所有控制信号的逻辑表达式,然后再添加第二条扩展指令的所有控制信号的逻辑表达式。以此类推。这样做的目的是便于调试、易于发现错误。

3 SWRR扩展指令的实现

下面将以SWRR指令为例,介绍在组合逻辑控制器的ABEL源文件中添加扩展指令的控制信号的逻辑表达式,编译控制器的ABEL源文件,对MACH器件编程,编写程序验证扩展指令是否正确的整个过程。

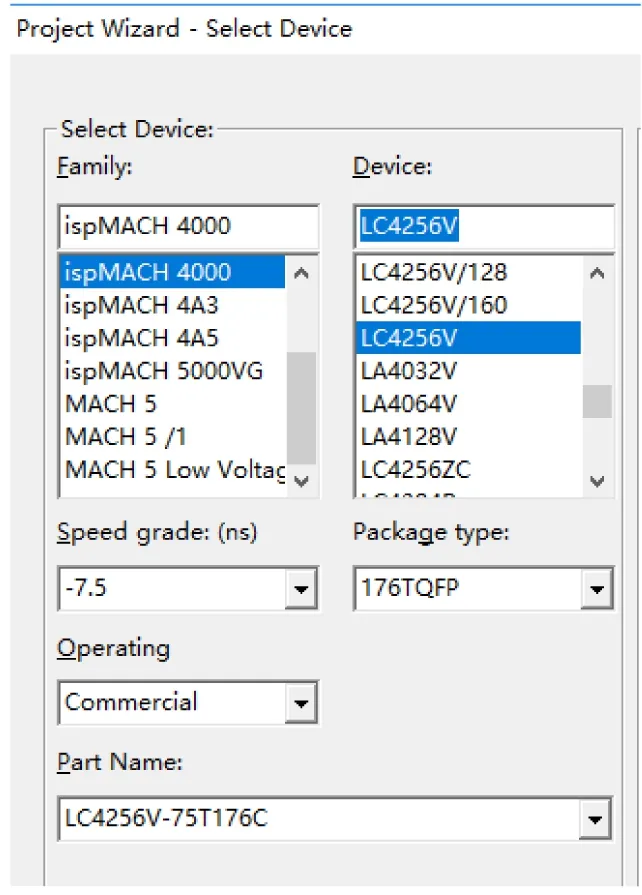

(1)启动Lattice ispLEVER Classic 2.0中的ispLEVER Classic Project Navigator软件,新建一个项目,项目名称必须是lc4256。

(2)选择器件类型,如图1所示。

(3)单击“Add Source”按钮,添加控制器源文件m256c.abl,如图2所示。然后,单击“完成”按钮。

(4)右键单击m256c.abl文件,选择“Open”命令。在文本编辑器中打开m256c.abl文件,如图3所示。

(5)在文本编辑器中修改m256c.abl控制器源文件。

图1 选择器件类型

图2 添加源文件

图3 打开源文件

在CALR=(IR==[1,1,1,0,0,0,0,0]);后面加一行代码:SWRR=(IR==[1,1,1,0,0,0,1,0]);

依据表3指令执行流程表的内容修改组合逻辑控制器32位控制信号的逻辑表达式。

在m256c.abl文件中,某个控制信号前面有!符号的,表示只有当某条指令在某个节拍该信号为0时,才需要将该条指令的操作码和节拍状态编码加入其逻辑表达式;某个控制信号前面无!符号的,表示当某条指令在某个节拍该信号为1时,才需要将该条指令的操作码和节拍状态编码加入其逻辑表达式。

例如,!_MIO控制信号,只有当某条指令在某个节拍/M信号为0时,才需要将该条指令的操作码和节拍状态编码加入其逻辑表达式。从表3可看出,SWRR指令在其三个节拍中/M信号都是1,所以!_MIO表达式不需修改。REQ控制信号,当某条指令在某个节拍R信号为1时,才需要将该条指令的操作码和节拍状态编码加入其逻辑表达式。从表3可看出,SWRR指令在其三个节拍中R信号都是0,所以REQ表达式不需修改。同理,_WE控制信号的逻辑表达式不需修改。

从表3可看出,SWRR指令在0111节拍时I2信号为1,所以在I2控制信号的逻辑表达式中要增加SWRR指令的操作码和0111节拍状态编码,即当节拍为0111、操作码为11100010(由SWRR=(IR==[1,1,1,0,0,0,1,0]),此时SWRR为1)时,I2控制信号为1,IR13为1表示扩展指令,#为或运算,&为与运算。

I2=C_M&((T==[0,0,1,1])&(MVRR#JR#JRC#

JRNC# JRZ#JRNZ)#

(T==[0,1,1,0])&(LDRR#IN_#OUT)#

(T==[0,1,1,1])&(SWRR)&IR13#

(T==[0,1,0,0])&(MVRD#LDRR#POP#JMPA#RET#STRR#PUSH#IN_#OUT)#

(T==[0,1,0,0])&CALA);

从表3可看出,SWRR指令在0110节拍和0101节拍时I1信号为1,所以在I1控制信号的逻辑表达式中要增加SWRR指令的操作码和0110、0101节拍状态编码,即当节拍为0110、0101,操作码为11100010(由SWRR=(IR==[1,1,1,0,0,0,1,0]),此时SWRR为1)时,I1控制信号为1。

I1 = C_M&((T==[0,0,0,0])#

(T==[0,0,1,1])&(INC#DEC#SHL#SHR)#

(T==[0,1,1,0])&(MVRD#JMPA#STRR#POP# POPF#PUSH#PSHF#RET#IN_#OUT#CALA)# (T==[0,1,0,0])&(MVRD#LDRR#POP#JMPA#RET#IN_)#

(T==[0,1,1,0])&(SWRR)&IR13#

(T==[0,1,0,1])&(SWRR)&IR13#

(T==[0,1,0,0])&(CALA)#

(T==[0,1,1,1])&(CALA)#

(T==[0,1,0,1])&(CALA));

从表3可看出,SWRR指令在0111节拍和0101节拍时I0信号为0,所以在I0控制信号的逻辑表达式中要增加SWRR指令的操作码和0111、0101节拍状态编码,即当节拍为0111、0101,操作码为11100010(由SWRR=(IR==[1,1,1,0,0,0,1,0]),此时SWRR为1)时,I0控制信号为0。

!I0 = C_M&((T==[0,0,1,0])#

(T==[0,0,1,1])&MVRR#

(T==[0,1,1,0])&LDRR#

(T==[0,1,0,0])&(POPF#STRR#PUSH#PSHF#OUT)#

(T==[0,1,1,1])&(SWRR)&IR13#

(T==[0,1,0,1])&(SWRR)&IR13#

(T==[0,1,0,1])&CALA);

从表3可看出,SWRR指令在其三个节拍中I8信号都是0,所以I8控制信号的表达式不需修改。

从表3可看出,SWRR指令在0111节拍和0101节拍时I7信号为1,所以在I7控制信号的逻辑表达式中要增加SWRR指令的操作码和0111、0101节拍状态编码,即当节拍为0111、0101,操作码为11100010(由SWRR=(IR==[1,1,1,0,0,0,1,0]),此时SWRR为1)时,I7控制信号为1。

I7 = C_M&((T==[1,0,0,0])#

(T==[0,0,0,0])#

(T==[0,0,1,1])&(ADD#SUB#AND#OR#XOR_#

MVRR#INC#DEC#SHL#JR#ADD1)#

(T==[0,0,1,1])&JRC&C#

(T==[0,0,1,1])&JRNC&(!C)#

(T==[0,0,1,1])&JRZ&Z#

(T==[0,0,1,1])&JRNZ&(!Z)#

(T==[0,1,1,0])&(MVRD#JMPA#POP#PUSH#

PSHF#RET#CALA)#

(T==[0,1,0,0])&(MVRD#LDRR#POP#JMPA#RET#IN_)#

(T==[0,1,1,1])&(CALA)#

(T==[0,1,0,1])&(CALA)#

(T==[0,1,1,1])&(SWRR)&IR13#

(T==[0,1,0,1])&(SWRR)&IR13#

(T==[0,0,1,1])&MVRD#

(T==[0,1,0,1])&(CALA));

从表3可看出,SWRR指令在0110节拍时I6信号为0,所以在!I6控制信号的逻辑表达式中要增加SWRR指令的操作码和0110节拍状态编码,即当节拍为0110、操作码为11100010(由SWRR=(IR==[1,1,1,0,0,0,1,0]),此时SWRR为1)时,I6控制信号为0。

!I6=C_M&((T==[0,0,0,0])# (T==[0,1,1,0])&(MVRD#JMPA#POP#POPF#RET#CALA)#

(T==[0,1,1,0])&(SWRR)&IR13# (T==[0,1,0,0])&CALA#

(T==[0,1,0,1])&CALA);

从表3可看出,SWRR指令在其三个节拍中I5信号都是0,所以I5控制信号的表达式不需修改。同理,I4和I3控制信号的表达式不需修改。

从表3可看出,SWRR指令在0110节拍和0111节拍时B口地址(B3 B2B1 B0)为IR的DR字段(IR7 IR6 IR5 IR4),在0101节拍时B口地址(B3 B2B1 B0)为SR(IR3 IR2 IR1 IR0),所以在B3控制信号的逻辑表达式中要增加SWRR指令的操作码,0110、0111节拍状态编码和IR7,以及0101节拍状态编码和IR3。同理,在B2控制信号的逻辑表达式中要增加SWRR指令的操作码,0110、0111节拍状态编码和IR6,以及0101节拍状态编码和IR2;在B1控制信号的逻辑表达式中要增加SWRR指令的操作码,0110、0111节拍状态编码和IR5,以及0101节拍状态编码和IR1;在B0控制信号的逻辑表达式中要增加SWRR指令的操作码,0110、0111节拍状态编码和IR4,以及0101节拍状态编码和IR0。

从表3可看出,SWRR指令在0111节拍时A口地址(A3 A2 A1 A0)为IR的SR字段(IR3 IR2 IR1 IR0),所以在A3控制信号的逻辑表达式中要增加SWRR指令的操作码,0111节拍状态编码和IR3。同理,在A2控制信号的逻辑表达式中要增加SWRR指令的操作码,0111节拍状态编码和IR2;在A1控制信号的逻辑表达式中要增加SWRR指令的操作码,0111节拍状态编码和IR1;在A0控制信号的逻辑表达式中要增加SWRR指令的操作码,0111节拍状态编码和IR0。

从表3可看出,SWRR指令在其三个节拍中SST2、SST1、SST0、SSH、SCI1、SCI0、DC2_2、DC2_1、DC2_0、DC1_2、DC1_1、DC1_0信号都是0,所以这些控制信号的表达式不需修改。

(6)保存m256c.abl文件。

(7)在左侧源文件窗口中单击m256c.abl文件,双击Compile Logic任务项,即对源文件m256c.abl进行编译。

(8)在左侧源文件窗口中点击器件图标,在右侧窗口中双击JEDEC File任务项生成lc4256.jed文件。完成后以绿色的“√”标记。若有警告信息,则以黄色的“!”标记,警告信息一般并不影响JEDEC文件的使用。

(9)启动Lattice ispLEVER Classic 2.0中的ispVM System软件,弹出主界面。

(10)将教学机左下方五个黑色的控制开关拨为10100(1表示往上拨,0表示往下拨)。

(11)通过Lattice USB 下载电缆HW-USB-2A连接PC机与教学计算机上MACH芯片,打开教学计算机电源。

(12)执行Options、Cable and I/O Port Setup…命令,设置Cable为USB接口,因为我们用的是USB ispDOWNLOAD Cables。

(13)通过ispVM System软件主界面的SCAN按钮找到在线编程器件。

(14)右击所找到的编程器件LC4256V,选择“Edit Device”,在“Device Information”窗口中选择Device为 LC4256V(B) ,通过Browse按钮选择已编译好的JED文件(lc4256.jed),单击OK按钮。

(15)重新回到ispVM System软件主界面,点击GO命令进行下载编程。编程成功后,关闭编程窗口。

(16)关闭教学计算机电源,拔下下载编程电缆。

(17)将教学机左下方五个黑色的控制开关拨为00110(1表示往上拨,0表示往下拨),启动WinPcec16软件,然后打开教学机电源,先按RESET键,后按START键,启动教学机监控程序。

(18)在WinPcec16软件中编写一个包含扩展指令SWRR的教学机程序,该程序将R0寄存器内容与R1寄存器内容作交换,程序运行结果表明扩展指令SWRR是正确的,如图4所示。注意:扩展指令必须用E命令输入。

4 结语

通过对TEC-XP16 教学机组合逻辑控制器扩展指令整个过程的研究,开设这样的设计性实验,学生可以从根本上理解计算机各组成部件的工作原理以及各个组成部件之间的联系,使其形成一个完整的计算机整机概念。这有益于提高学生的设计能力和创新能力,培养学生分析问题和解决问题的能力,激发学生学习的主动性和积极性。

图4 包含扩展指令SWRR的教学机程序的运行结果