一种应用于多通道模数转换器的串行输出接口设计

穆敏宏,叶 凡,任俊彦

(复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

如今,模数转换器(Analog to Digital Converter, ADC)在现代混合信号系统中已经不可或缺.随着现代混合信号系统中数字电路部分的速度越来越快,数据吞吐量越来越高,普通的单通道ADC已经无法满足系统要求,多通道ADC替代单通道ADC已经是一个不可逆转的大趋势.但是,多通道ADC的输出引脚数相比于单通道ADC来说是成倍增加的,因此在芯片封装引脚资源极为有限的情况下,多通道ADC通常需要配合着对应的串行输出接口同时使用.为了适应目前ADC界的发展趋势,高速串行输出接口的设计是目前国内外的研究热点,一款符合输出速率要求的串行接口可以有效地减少引脚输出数目,降低芯片的封装成本,简化后期印制电路板的设计.

目前,国内外对串行接口(Serial Interface)的研究焦点主要集中在低压差分信号(Low-Voltage Differential Signalig, LVDS)以及电流模逻辑(Current Mode Logic, CML)上.二者相比,LVDS功耗较低,但速度较慢,目前主流的LVDS接口速度普遍在1~2Gb/s左右[1-2],而CML则以些许功耗为代价,换取了较快的速度,传输速率可以达到10Gb/s以上[3],更适用于高速光通信ADC的输出需求.在高速串行接口领域,我国与国外有着较大的差距.BM公司开发的HSS(High Speed SerDes)IP硬核,采用了CML接口,传输速率可以达到2.5~11.1Gb/s.Xilinx公司的GTH速度最高到16.3Gb/s,GTY更是达到30Gb/s.而目前,我国接口电路方面较为领先的国防科技大学,自主研发的串口芯片传输速率还停留在5Gb/s左右.

本文针对多通道ADC的具体项目应用,对输出接口进行了设计优化[4],提出一种新的并行扰码发生器设计方法,并在65nm CMOS工艺下完成其电路实现,考虑了电源非理想性的影响后,通过系统仿真以及版图后仿真结果得出,该输出电路能够适用于4Gb/s速率的数据传输.

1 系统架构

本文针对基金项目设计的串行输出接口整体结构如图1所示,主要应用于一个8Gb/s、6bits时间交织模数转换器(Time-Interleaved ADC, TIADC)的数据输出.TIADC由6通道构成,每个通道都有自己的采样保持电路,以1.33Gb/s的速率输出6bits数据.串行输出接口主要包含4部分: 扰码电路、并转串电路、时钟电路、CML输出电路.

在高速接口中,当输出数据流中出现连续的0或连续的1时,数据无法自定时,且直流分量会随着数据流内容的变化而变化,低频内容占主导地位,不利于接收端的接收,因此高速传输的数据需要进行加扰,使其0和1的个数大致相等且分布具有随机性.扰码电路由多路选择器、扰码发生器与异或门构成,可以将ADC的输出与伪随机序列(Pseudo-Random Binary Sequence, PRBS)进行异或从而输出加扰信码,也可以直接输出PRBS本身作为同步头.

图1 串行输出接口电路整体架构Fig.1 Architecture of serial interface

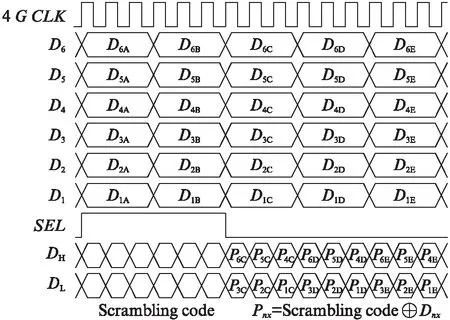

图2显示了单通道的时序,当数据选通信号无效时,系统的各通道输出均为相同的PRBS数据流,因此我们可以在接收端以相同的PRBS数据流作为标定,来同步对应的解码数据流,当解码数据流同步完成后,数据选通信号有效,加扰信号经过接收端解码数据流的解码,即能恢复原始输出数据.经过加扰的6bits数据随后分成两路进入并转串电路,并转串电路的作用是将多路低速并行信号转换为一路高速串行信号.本设计中,每一单个通道的ADC其6bits输出分为2路,每路3bits,并转串单元输入1.33Gb/s×3bits并行数据,输出4Gb/s×1bit串行数据,时钟模块为其提供3路等相位间隔的1.33G数据合并时钟.最后,由CML驱动电路将CMOS信号转换为低摆幅的CML差分信号,经传输线传输至接收端.由于串口要用于上G赫兹的高速电路,因此设计串口时,电路的速度是首要的考虑因素.

本设计对串行结构中的时钟电路进行了设计优化,采用延迟锁相环(Delay-Locked Loop, DLL)替代了传统并转串输出电路中的锁相环(Phase-Locked Loop, PLL).DLL与PLL的结构对比如图3所示.DLL中除了一个大反馈环外就只有延迟链,输出信号是输入信号的延迟,二者同频率且有一个固定的相差.而PLL中除了反馈环外还需要一个环形振荡器,由于环形振荡器在内部自起振,因此其远比DLL要复杂.DLL相比于PLL精度更高,且可以排除温度、电压变化带来的影响,用DLL替代PLL能够使整个设计的难度降低,面积、功耗、性能等都具有一定优势.

图2 单通道输出数据时序Fig.2 Output signal sequence of single channel

图3 DLL与PLL的结构图Fig.3 Architecture of DLL and PLL

2 电路实现

2.1 扰码

为平衡数据流的直流偏置,本设计进行并行加扰处理.在发射端,将要传输的信号与本地产生的扰码序列进行异或运算,得到加扰序列{bk+Sk1};在接收端,将接收到的加扰数据与本地产生的扰码序列进行异或运算,得到解扰序列{bk+Sk1+Sk2}.从数学上来看,只要Sk1与Sk2完全相同,解扰序列就与原先的信号相同.

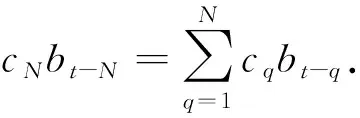

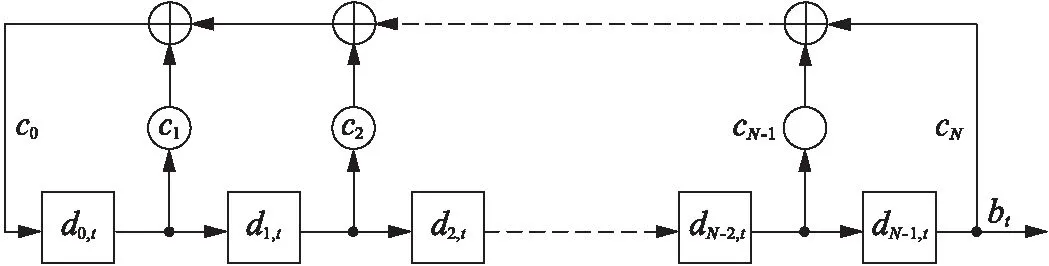

图4所示的N级线性反馈移位寄存器所对应的特征多项式为:

(1)

该系统产生的伪随机序列的递推公式为:

(2)

图4 N级线性反馈移位寄存器Fig.4 N-stage linear feedback shift register

如图5所示,加扰方式有两种: 串行加扰(Serial Scrambler)和并行加扰(Parallel Scrambler)[5-8].串行加扰先将频率为fb的低速并行数据转为频率为M×fb的串行数据,然后再以M×fb的频率对高速串行数据进行加扰,而并行加扰则先以fb的频率对频率为fb的低速并行数据进行加扰,然后再将加扰后的数据串行化.由于触发器状态翻转速度的限制,串行加扰并不适用于高速应用.并行加扰中,扰码发生器一次输出M位连续的扰码,同时对多路进行加扰,大大降低了触发器的速度要求,且最终的串行输出数据与串行加扰结果相同,对接收端无任何影响.

图5 串行加扰与并行加扰的结构图Fig.5 Architecture of serial scrambler and parallel scrambler

设计并行扰码发生电路主要有两种方法: 矩阵法[9]与序列空间法[10].矩阵法设计简单,但结构单一,速度较慢;序列空间法能够实现较快的电路结构,但其理论复杂,设计困难.本文在矩阵法与序列空间法的基础上进行修改,提出了一种新的设计方法,并命名为基元迭代法.以下就以基于最简扰码PRBS5的6路并行扰码器为例介绍基元迭代法的设计方法.PRBS5的特征多项式为f(x)=x5+x3+1,是5阶线性反馈系统,至少需要5个寄存器,设0、1时刻扰码发生器的各状态为B0、B1,则:

B0=[b0b1b2b3b4b5],

B1=[b6b7b8b9b10b11b12],

(3)

图6 基于PBRS5的扰码发生器电路结构Fig.6 Architecture of scrambling code generator based on PBRS5

定义不同数目的系统基元可以得到不同的电路结构,在此定义其中前7个码b0、b1、b2、b3、b4、b5、b6为基元,对B1的任意码元bi,都可以通过式(2)反复迭代,最终变化为各基元的组合,得到:

B0=[b0b1b2b3b4b5],

B1=[b6b2⊕b4b3⊕b5b4⊕b6b0⊕b4b1⊕b5],

B2=[b2⊕b6… … … … …].

(4)

由于B1是B0的下一状态,因此可以通过其基元表达式直接求得电路结构(见图6).

表1 不同设计方法实现的扰码发生电路性能比较

实际运用中,各种不同的系统对扰码发生器的需求都不尽相同.由于本文最终设计的输出接口运用于光通信项目,因此相比于硬件成本,扰码发生器的最高工作频率才是侧重点.电路的最高工作频率取决于电路的关键路径延时,因此如何求解出关键路径延时最短的电路结构是本文设计扰码发生器的首要问题.表1比较了矩阵法、序列空间法以及基元迭代法所设计的电路结构,假设触发器为8个等效门大小,异或门为2个等效门大小,可以看到,基元迭代法设计的电路关键路径最短,以面积换取了速度.

在本设计中实际采用的是目前10Gb/s以下串行总线最常用的扰码序列PRBS7,其特征多项式为f(x)=x7+x6+1.由于本设计需要实现3∶1的并串转换,因此需要设计3路并行扰码发生器,其通过基元迭代法设计出的电路结构如图7所示.

图7 基于PBRS7的扰码发生器电路结构Fig.7 Architecture of scrambling code generator based on PBRS5

2.2 并转串电路

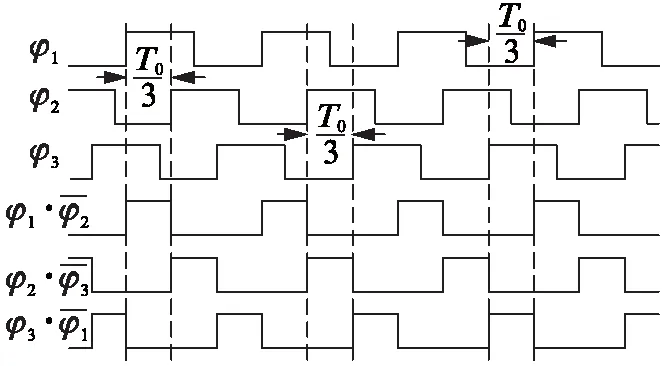

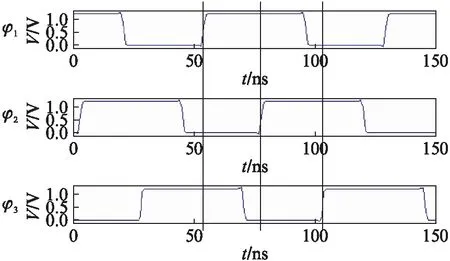

并转串电路主要有串行结构、并行结构与树型结构.各结构能达到的最高速度相仿,但树型结构的输入只能是为2N路,并不适用于本设计的3路并串转换;而并行结构相比传统的串行结构,高速模块大大减少,所有电路都工作在1.33GHz的输入数据频率,具有较低的功耗.因此本设计所采用的并转串电路如图8所示,采用并行结构.并转串电路由DLL与逻辑电路构成,其中DLL将输入的1.33GHz数据时钟φref转化为3个1.33GHz等相位间隔的时钟φ1、φ2、φ3,如图9所示.然后多相时钟经过逻辑电路,得到输入信号D1、D2、D3的选通信号,最后通过与门、或门将数据合并.出于后续电路的兼容性考虑,本设计采用了带有传输门的线或结构.

2.3 延迟锁定环(DLL)

DLL在系统中负责产生并转串电路所需的多相位时钟,其工作的稳定性非常重要.DLL如图10所示,由鉴相器、低通滤波器以及压控延时链(Voltage-Controlled Delay Line, VCDL)构成.本设计中,鉴相器选用鉴频鉴相器,低通滤波器选用电荷泵加RC通路,VCDL选用带正反馈耦合的差分VCDL,其结构如图11所示,共30级,从第5、15、25级的输出得到所需的多相位时钟φ1、φ2、φ3.

图8 并转串电路Fig.8 Architecture of multiplexer

图9 φ1、φ2、φ3的相位关系Fig.9 Phase relationship of φ1、φ2、φ3

图10 DLL结构框图Fig.10 Architecture of DLL

图11 VCDL电路图Fig.11 Architecture of VCDL

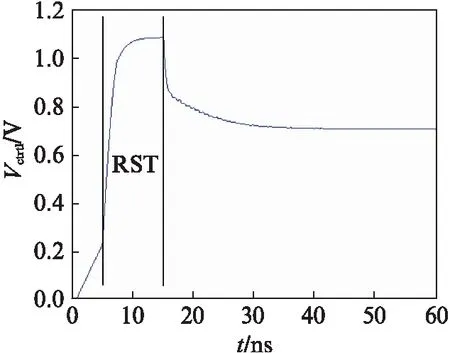

为得到相位依次相差2π/3的多相位时钟φ1、φ2、φ3,DLL的输出信号Vdll必须与输入参考信号Vref同频率,且相位恰好相差2π.如图12所示,若Vdll的上升沿先于Vref的上升沿进入鉴相器,则认为φref>φdll,此时,控制电压Vctrl会降低以使φref=φdll;反之控制电压Vctrl则会上升.通过合理设置Vref与Vdll的复位时间,可以确保Vdll的上升沿先于Vref的上升沿进入鉴相器,从而使控制电压单向(向下)变化.如图13所示,随着Vctrl的下降,VCDL的延时会逐渐变大,若要确保Vdll与Vref相位相差2π,则在Vctrl下降的过程中必须存在某一个控制电压值所对应的延时恰好等于输入参考信号的周期T0.

图12 电压变化原理图Fig.12 Principle of voltage variation

图13 VCDL的电压延时特性曲线Fig.13 Characteristic of voltage delay of VCDL

假设前级电荷泵输出的初始电压为Vctrl_0,最低电压为Vctrl_min,Vref的周期为T0,则VCDL在控制电压V下的延时t(V)需要满足下式:

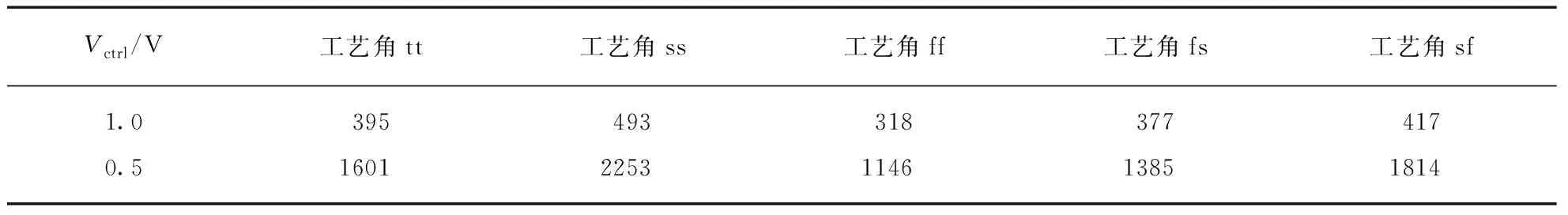

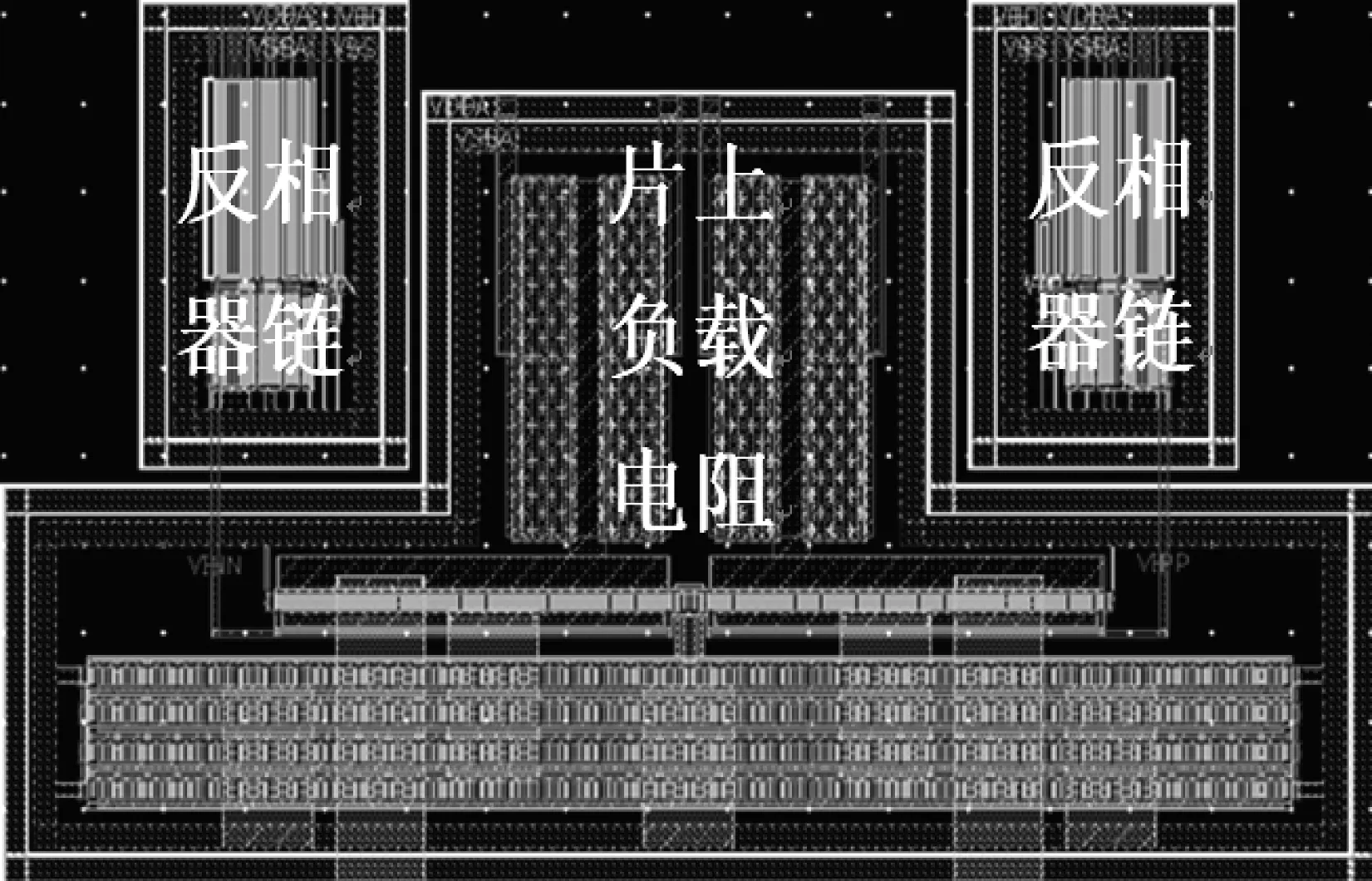

t(Vctrl_0) (6) 由于工艺偏差会导致阈值电压及其他一些参数的改变,不同工艺角下单位Vctrl变化所引起的VCDL延时变化都不尽相同,因此,在设计时需要进行大量仿真以确保各工艺角下,6通道的VCDL都能满足式(6)从而确保DLL能正常工作.本设计中,Vctrl_0为1V,Vctrl_min为0.5V,Vref的周期为T0为750ps.表2为VCDL在各工艺角下的版图后仿真,可以看到,电路在各工艺角下均满足t1V<750ps 表2 各工艺角下不同控制电压的延时 常用的输出驱动电路有4种结构: ECL、PECL、LVDS与CML.由于CML相比ECL、PECL具有低功耗,结构简单的优点,相比LVDS具有传输速率高的优点[11],因此本设计采用CML接口电路.CML可以在较低的电源电压下以低摆幅点对点高速传输数据,结构如图14所示.CML从结构上来看类似于一个共源级运放,由尾电流管控制总电流大小,通过差分输入来控制输入对管的导通状态,差分输出的幅度大小由负载电阻与尾电流的乘积决定.CML的传输特性曲线如图15所示,其输出摆幅为RIss.CML结构简单,工作时不需要外接电阻,可以通过负载电阻(一般是50Ω)直接对传输线进行阻抗匹配.本设计中,负载电阻取值为50Ω,因此不再需要做阻抗匹配.此外,由于CML是差分结构,因此具有较高的噪声抑制能力;输入对管一直工作在开关状态,因此在版图设计时并不需要像运放那样进行复杂的对称匹配.在电路的实际设计中,由于CML的输入对管尺寸较大,因此在输入前端往往会增加反相器链来增强前级数字电路的驱动能力. 图14 CML电路Fig.14 Architecture of CML 图15 CML传输特性曲线Fig.15 Transmission characteristic of CML 当CML电路处于全切换状态时,导通的输入管处于饱和区,因此电路的等效输出电阻就是上拉电阻R,等效输出电容为寄生电容与负载电容之和,其传输延时如式(7)所示: Tdelay=ln 2×R(Cload+Cself). (7) 在CML的设计中,尾电流越大,各MOS管的尺寸也越大.而当Cload远大于Cself时,CML的传输延时与MOS管尺寸无关,因此尾电流大小只影响输出信号的摆幅.CML设计指标为差分输出摆幅400mV,对应的尾电流大小为8mA. 本论文采用65nm CMOS工艺设计了一个基于DLL的串行输出接口,实现了1.33GHz时钟下3∶1并转串,使多通道ADC能够串行输出量化数据.单通道数字模块电路(扰码发生器、并串转换电路、DLL)的版图面积为72μm×97μm(见第602页,图16),功耗1.9mW;单个CML输出电路(包括输入驱动链)的版图面积为85μm×53μm(见第602页,图17),功耗为9.6mW.本设计的仿真验证分为两个部分: 其一是电路各部分的功能正确与否;其二是DLL与CML的输出信号质量如何. 首先验证DLL能否锁定以及其生成的多相位时钟φ1、φ2、φ3是否正确.图18(见第602页)显示了DLL的锁定过程,在复位过程中,DLL的控制电压Vctrl被置位到1.2V,随后进入锁定过程,控制电压Vctrl先通过电荷分配被置位到1V,最终Vctrl稳定在706mV左右,锁定完成.如图19(见第602页)所示,DLL锁定后,各多相位时钟间相位间隔都为T/3,功能正确实现,能用作并串转换电路的控制信号. 图16 数字电路版图Fig.16 Layout of digital circuit 图17 CML版图Fig.17 Layout of CML 图18 DLL锁定过程Fig.18 Locking process of DLL 图19 DLL多相位时钟后仿Fig.19 Post-layout simulation of DLL multi-phase clock 然后再验证并行扰码发生器与并串转换电路的功能是否正确.并行扰码发生器的后仿结果如图20所示,图中标识出的部分逻辑序列为“101 001 111 101 000 011”(顺序为S0,S1,S2不断循环),符合PBRS7的递推关系,功能正确.串转换电路的后仿结果如图21所示,并行数据与串行数据一一对应,转换功能正确.最后将电路的输入信号、扰码序列与加扰后输出的后仿结果提取到Matlab中进行计算比较,结果显示6通道1.33Gb/s×3bits转4Gb/s×1bit均正常工作,解扰后的数据与原始数据相同. 图20 并行扰码发生器后仿Fig.20 Post-layout simulation of PRBS 图21 单通道并串转换电路后仿Fig.21 Post-layout simulation of single-channel multiplexer 在本设计中,DLL最重要的性能指标是输出时钟的抖动,时钟边沿的抖动会直接影响后级并转串电路的信号位宽.对设计进行性能仿真时,系统的输入为伪随机码.DLL输出的时钟眼图如图22所示,时钟周期为750ps,最大峰峰值抖动为515fs,满足并转串电路对时钟的要求.CML的后仿条件如图23所示,在电源端串联了1nH电感、10Ω电阻,并联2pF电容等效电源噪声;在输出端加入了输出pad,串联了1nH电感、10Ω电阻等效邦定线;采用1pF对地、差分100Ω负载(CML片上负载电阻为50Ω,因此单端输出阻抗为50Ω,自动实现阻抗匹配).图24为CML的输出信号眼图,在4Gb/s输出情况下,差分输出摆幅为400mV,眼图端正,眼高359mV,眼宽232ps,码间串扰越小,噪声容限为174mV,0点变动宽度为18ps.整个系统符合应用要求. 图22 DLL时钟抖动Fig.22 Jitter peak to peak of DLL 图23 CML后仿条件Fig.23 Test bench of post-layout simulation of CML 图24 CML输出眼图Fig.24 Eye diagram of CML 表3 不同设计方法实现的串行输出接口性能比较 本文采用65nm CMOS工艺设计了一款适用于高速多通道模数转换器的串行输出接口,包含扰码、并串转换、DLL与CML等模块,并实现了1.33Gb/s×3bits到串行4Gb/s×1bit的并串转换输出.相比于传统串行扰码发生器的结构,本文所提出的一种新的并行扰码发生器设计方法,能缩短关键路径的延时;同时,我们还对串行输出接口进行了设计优化,即采用DLL替代了PLL,这样不仅降低了温度、电压波动带来的不良影响,还使得面积、功耗等性能均有提升;此外,还对DLL的输出进行简单逻辑运算以替代传统并行并串转换电路中的非交叠时钟,既简化了设计,又提升了系统的稳定性.

2.4 电流模逻辑(CML)

3 仿真验证

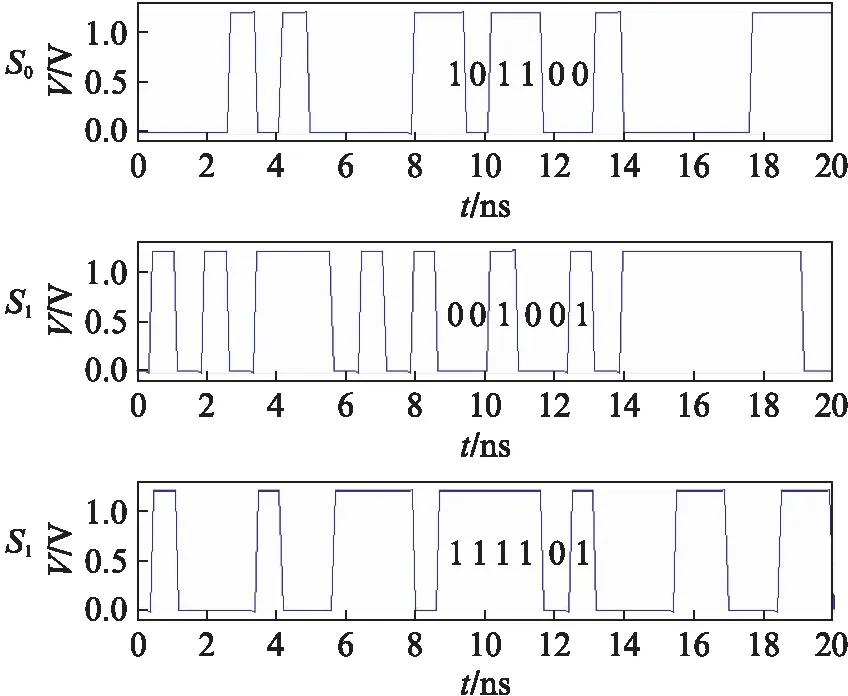

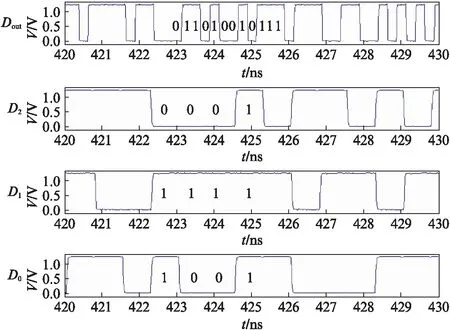

3.1 功能仿真

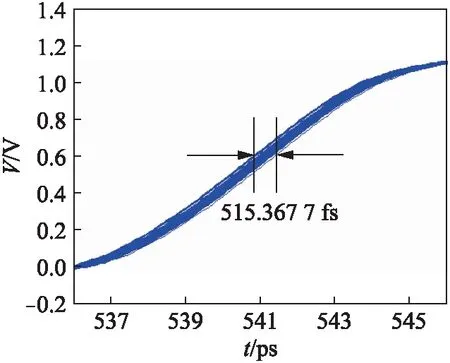

3.2 性能仿真

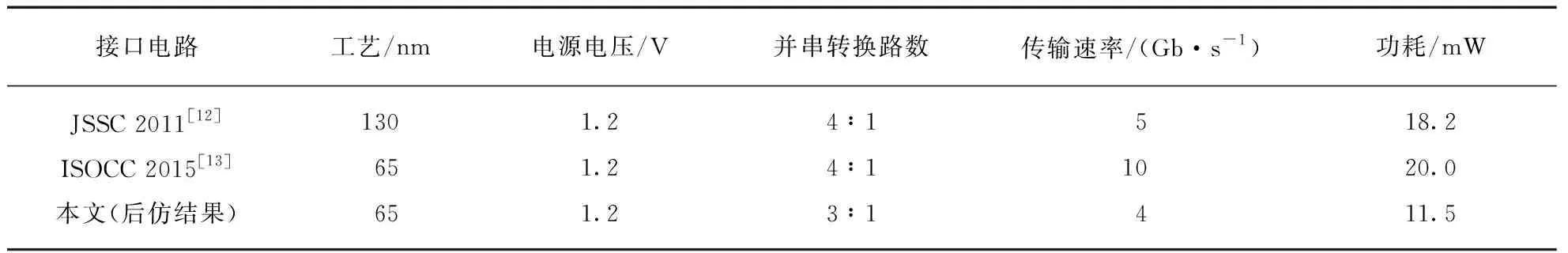

4 结 论