Type C Gen2对绞线的线缆设计*

林清寿,李必禄,何小明

(安费诺电子装配(厦门)有限公司,福建 厦门 361009)

0 引 言

2013年12月,USB3.0推广团队公布了下一代USB连接器Type-C的渲染图。随后,在2014年8月开始进行大规模量产。新版接口的亮点在于更加纤薄的设计、更快的传输速度(最高10 Gb/s)以及更强悍的电力传输(最高100 W)。Type-C双面可插接口最大的特点是支持USB接口双面插入,正式解决了“USB永远插不准”的世界性难题,实现了正反面随便插[2]。2015年3月9日,在美国举行的苹果新品发布会上,全新MacBook首次在笔记本电脑上将电源接口、USB接口、DP接口、HDMI接口与VGA接口统一用一个Type C接口来承载,是Type C技术第一次在消费级笔记本电脑上的应用[3]。

随着Type C接口的广泛适应,与它配套使用的USB数据线也必须更细和更轻便。Type C兼容USB2.0/3.0/3.1接口,并通过E-Marker芯片技术自动识别电子产品所需的电压和电流,输出电流2~5 A。封装有E-Marker芯片的Type C有源电缆,DFP和UFP利用PD协议可以读取该电缆的属性,包括电源传输能力、数据传输能力和ID等信息。在Type C外模尺寸不变的情况下,如何解决带E-Marker芯片的全功能Type C cable assembly的SI性能和可制造性问题成为重点。本文基于polar SI 9000仿真软件对整条Type C线缆链路按产品实际制程的要求进行阻抗较为精确的仿真并采用新的制程工艺成功解决Type C Gen 2的SI性能及可制造问题。

1 Type C线缆结构

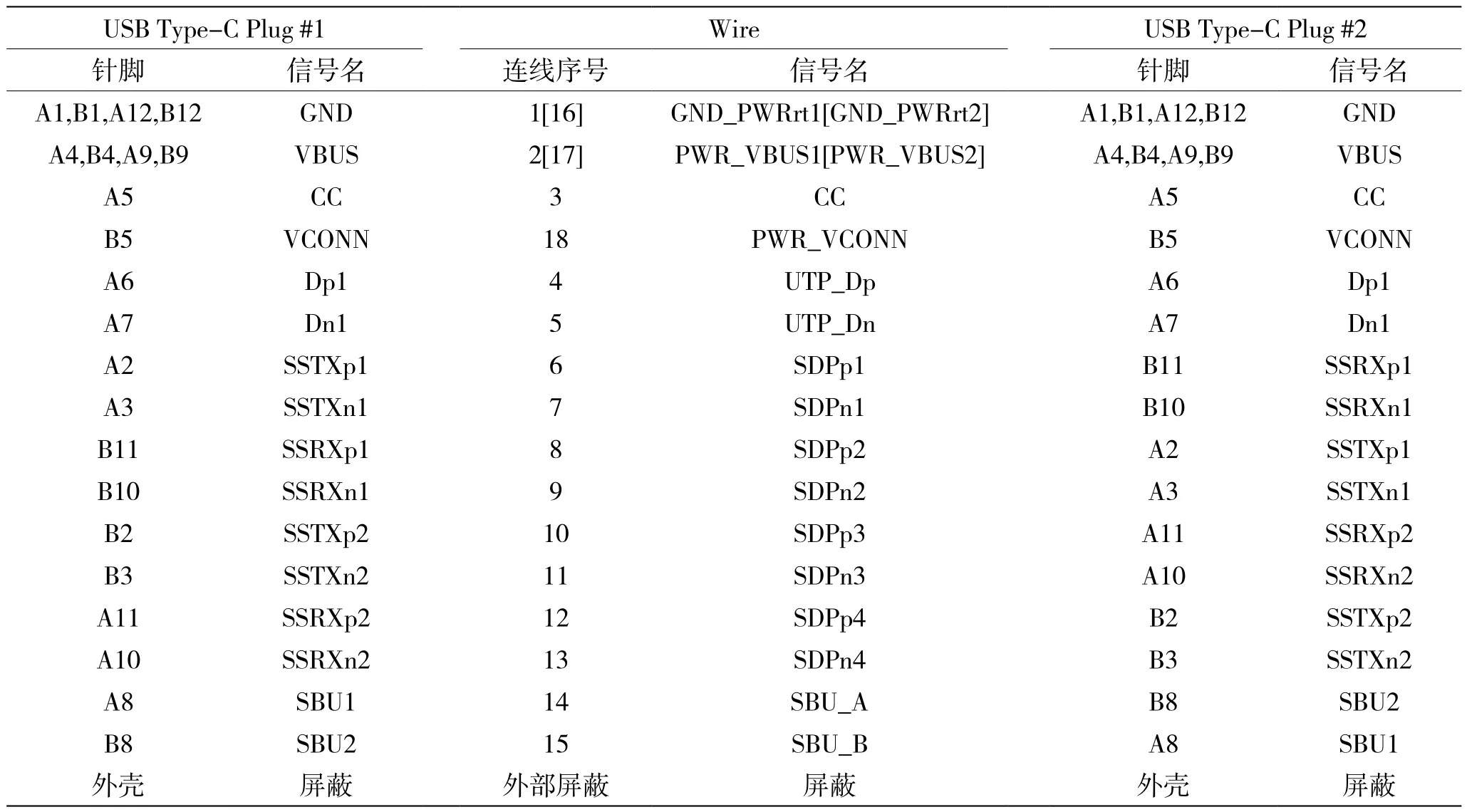

Type C cable assembly产品图纸外形图如图1所示。它的内部组成为Type C连接器+PCBA+Raw Cable+PCBA+Type C连接器,如图2所示。全功能Type C线缆的标准接线表,如表1所示。

图1 Type C cable assemble产品图纸外形

图2 Type C连接器+PCBA+Raw Cable+PCBA+Type C连接器

表1 全功能Type C线缆的标准接线

2 Type C线缆链路的阻抗控制设计

为了更好的成本管控,目前大多数厂商采用镀锡对绞线来制造Type C Raw cable。正常来说,Raw线材性能只要管控好衰减和ILD参数,即可满足Type C的SI性能要求。因此,Type C PCBA的设计和制程加工才是整个Type C SI性能的瓶颈。Type C Cable性能好不好,主要看整个链路的阻抗是否连续平稳且在规范要求的范围(76~96 Ω)内。如果阻抗在整个链路都比较平稳,那它的IMR/IRL性能较好;反之,IMR/IRL性能会Fail。当然,阻抗是否连续平稳不仅会影响IMR/IRL的性能,而且影响衰减、串扰等SI参数。因此,Type C线缆最关键的一点是阻抗控制。

影响Type C整条线缆阻抗连续性主要有6个区域:

(1)Type C连接器本身的阻抗;

(2)Type C连接器与PCBA焊接的SMT区域;

(3)PCBA板上阻抗线的区域;

(4)PCBA焊线区域;

(5)开线口区域;

(6)SR铆压区域。

2.1 Type C PCBA的阻抗设计

Type C接头本身的阻抗一般设计为85 Ω。由于Type C连接器阻抗仿真及制造比较复杂,因此本文主要针对Type C-连接器与PCBA焊接的SMT区域、PCBA板上阻抗线、PCBA焊接区域、开线口区域以及SR铆压区域做设计仿真及分析。Type C连接器与PCBA焊接的SMT区域、PCBA阻抗线和PCBA焊线区域的阻抗与PCBA设计关系密切。考虑到后工段的加工工序会对这3个区域造成阻抗下降的影响,要特别注意PCB板材的选型、阻抗设计和叠层结构等。考虑到客户可能需要无卤的材质,推荐的板材是EM888K。

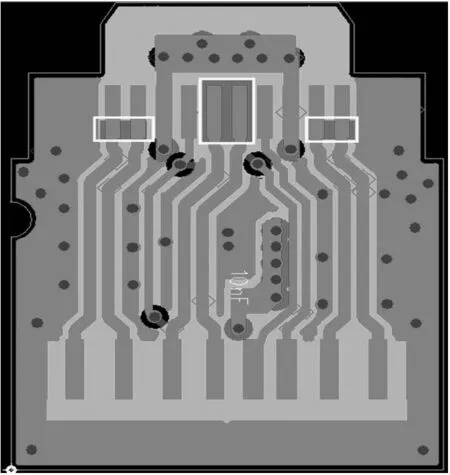

Type C连接器SMT工序和后工段的内模工序会导致该区域的阻抗下降10 Ω左右。因此,针对PCBA SMT区域的焊盘要做特别设计,需要上下两面焊盘采用内层错开挖空的方式,如图3所示。另外,对钢网的开口和厚度也要做特别的规定。钢网的开口大小跟焊盘面积一样,钢网厚度建议为0.08 mm。

图3 上下两面焊盘采用内层错开挖空的方式

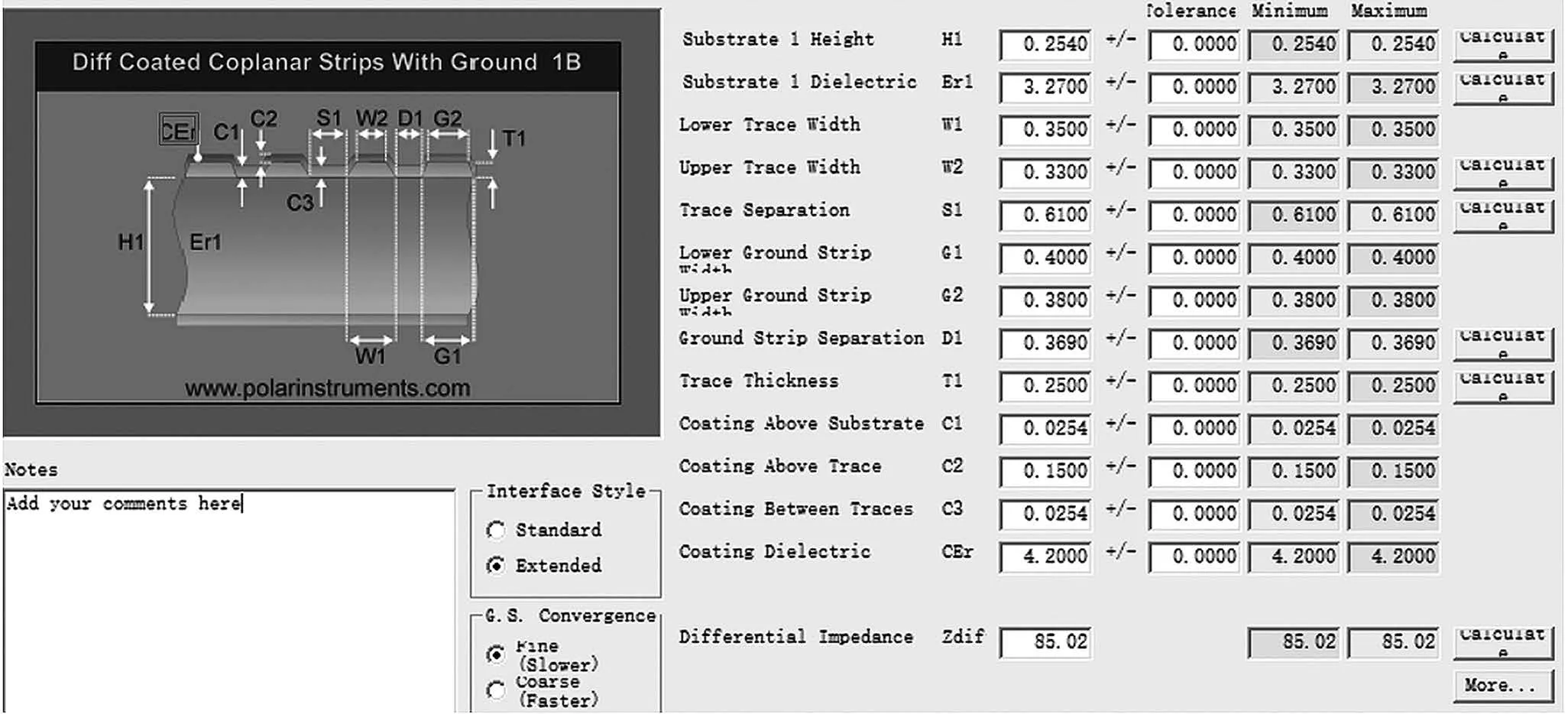

基于后工段内模工序会造成PCBA板上阻抗线阻抗下降的影响,将阻抗线中值设计为92 Ω进行补偿。PCBA来料按(92±7) Ω的公差来管控。叠层结构和PCBA阻抗线仿真,如图4所示。

图4 叠层结构及PCBA阻抗线仿真

2.2 开线口区域的阻抗控制

针对PCBA焊接区域,要考虑焊线、涂UV胶及内模工序会使该区域的阻抗下降。因此,设计时需同时该区域焊盘区域的阻抗要将线材、UV胶及内模综合因素等。经过焊线、涂UV胶及内模工序 后的仿真基本可以稳定在85Ω左右,如图5所示。

图5 经过焊线、涂UV胶及内模工序后的仿真

2.3 SR铆压高度控制

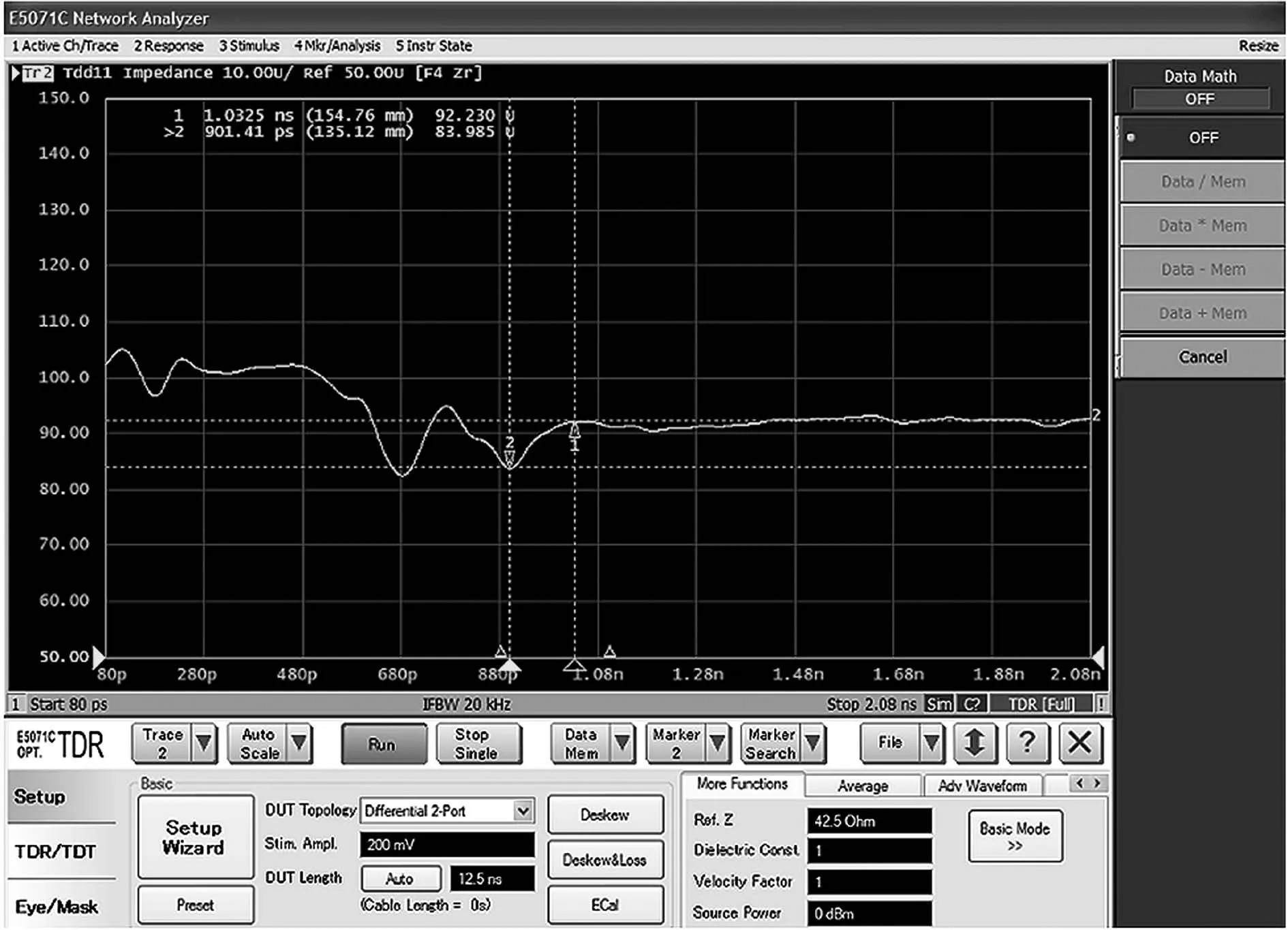

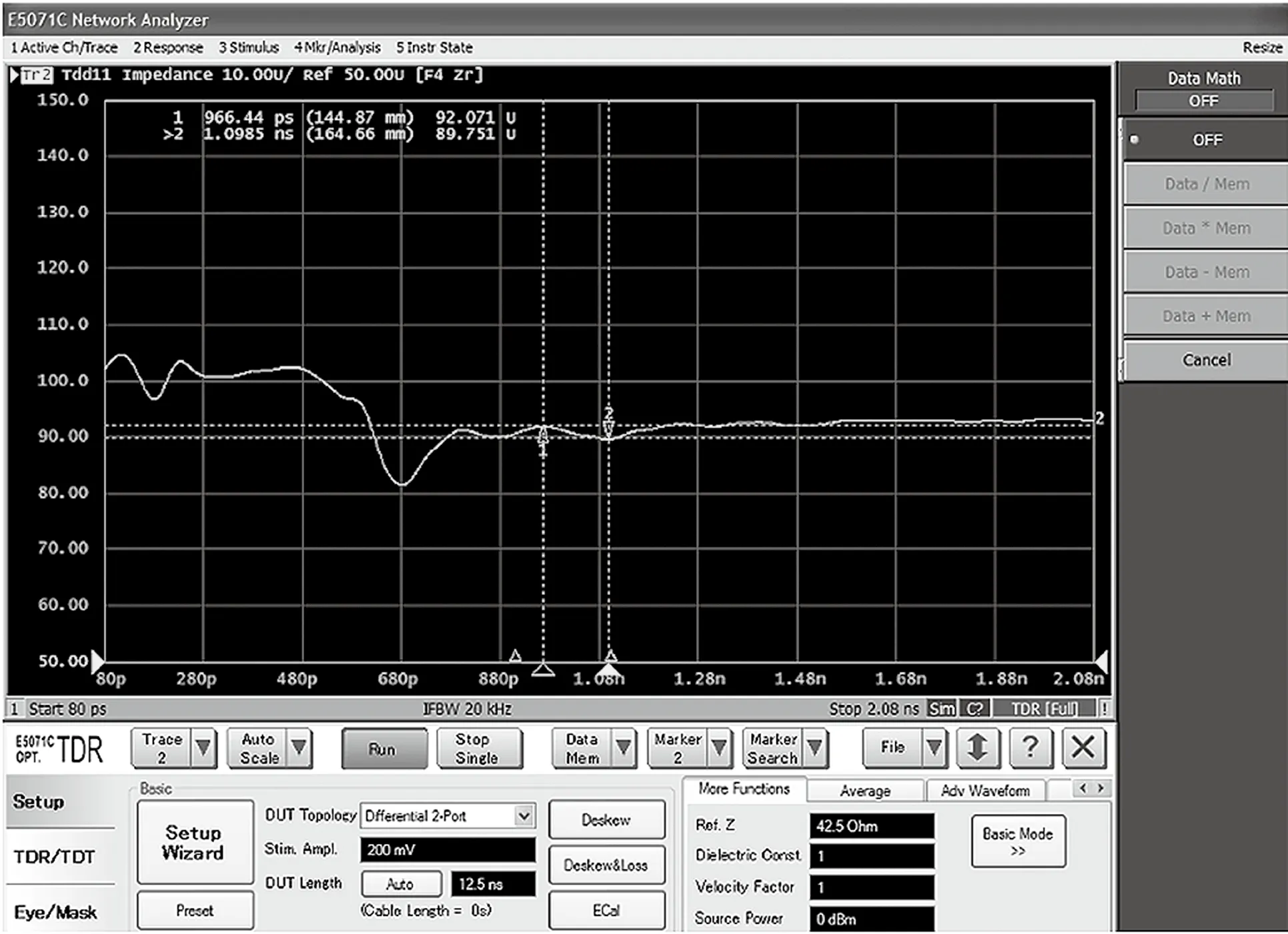

最后,要控制好SR铆压高度,因为线材铆压过紧会使差分线受到挤压造成阻抗下降。因此,控制铆压高度也是非常重要的。要根据线材的外被OD设置不同的铆压高度。图6是铆压过紧造成阻抗跌落的曲线。通过上述6个区域的阻抗控制,比较理想的阻抗线如图7所示,且该条Cable通过了Type C Gen 2的SI性能测试。

图6 铆压过紧造成阻抗跌落的曲线

图7 比较理想的阻抗曲线

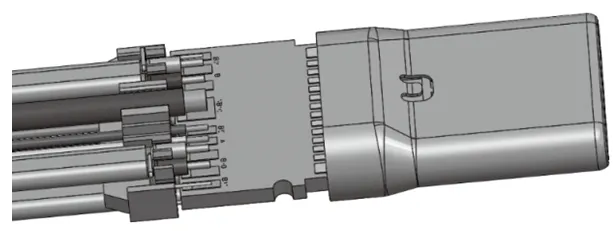

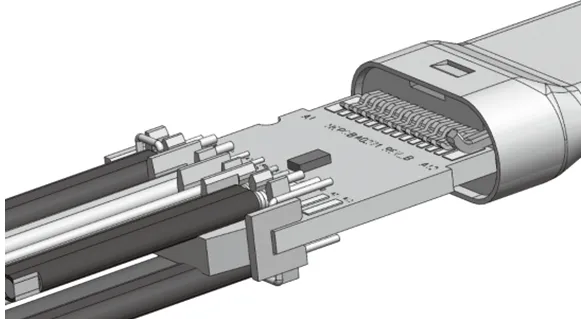

3 新的线夹工艺

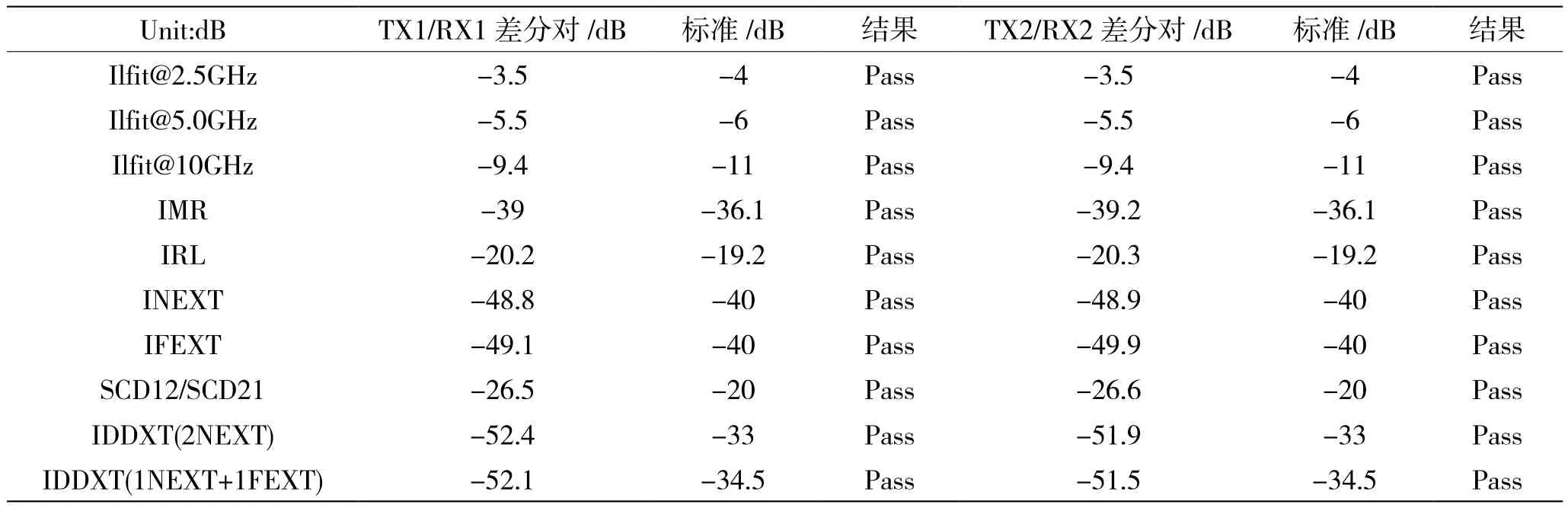

Type C线缆的另外一个难点是可制造性不好。为了方便大批量生产,引入线夹工艺,即在焊接前先将线摆进线夹再hot bar焊接的方式。引入线夹会增加高速差分对铝箔开口的长度,导致top面和bot面高速差分对在开线口区域的串扰增加。经过多次改善和验证,终于找到了一种彻底解决串扰的线夹工艺。图8的线夹方式是最常用的线夹工艺,开线口阻抗不好控制,且高频串扰特别是INEXT参数会出现不良。为了解决这个串扰不良,验证将线夹厚度由0.8 mm增加1 mm,验证结果仍不能完全解决Type C串扰的问题。另外,Type C Gen2要求衰减更严格。随着镀锡Raw线材OD增大,整体的Cable OD也相应变大,制造变得越来越困难,制程对串扰的影响也变得越来越大,产品的制程工艺变得越来越困难,产品的良率也变得越来越差。为了从根本上解决Type C高频串扰的问题,将线夹设计更改为如图9所示的方式,即将线夹套进PCBA,以保证上下面的线夹开线口区域通过PCB板的地平面隔离,有效降低开线口阻抗和改善高频串扰。实际1M Type C Gen 2线缆成品的测试结果如表2所示。

图8 线夹方式

图9 线夹设计更改

表2 实际1 M Type C Gen 2线缆成品的测试结果

4 结 语

本文提出通过polar SI 9000仿真软件,结合Type C线缆实际制造工艺,模拟仿真整条Type C线缆链路的阻抗,同时采用改进的线夹工艺来解决Type C Gen 2 IMR/IRL、串扰问题,并同步解决了大批量生产问题。实际制造的产品通过USB协会的认证结果表明,通过实际模拟和控制整条链路的阻抗和采用新型线夹工艺,对Type C高速线缆开发具有重大意义。