数据丢包对DC/DC无线并联均流系统的影响

承良超,葛芦生,陈宗祥,刘雁飞

(安徽工业大学电气与信息工程学院,马鞍山243000)

由于计算机、通讯等的广泛应用,其要求组建大容量、安全可靠、不间断供电的电源系统,而开关电源并联系统利用多个模块共同承担负载功率,使得功率器件承受的热应力和电气应力减小,提高了系统的可靠性,同时也缩短了开发周期、降低了生产成本。但在DC/DC并联功率变换器的各个模块间通过物理连线来实现信息传递会引发多种问题:第一,并联子模块间物理连线作为一种单点失败源,任意损坏点都有可能导致整个系统的失败[1];第二,互联线易引入噪声与干扰,降低系统性能,限制转换器模块的放置地点;第三,附加在控制器与变换器间的连接电缆会使电源系统的易维护性极大降低[1-2]。因此,需要一种模块间无附加互联线的动态均流信息传递策略,即无线并联系统,它提高了分布式供电系统的可靠性和灵活性[3]。

目前,对并联变换器无线控制进行了一些相关研究。文献[4]中Tuladhar和Jin提出一种信号注入技术实现强制均流;文献[5-6]中Mazumder等提出一种无线脉宽调制PWM(pulse width modulation)技术以实现并联DC-DC变换器均流控制。而在无线并联系统应用中,当产生新均流信息时,系统将删除上一次未发出信号。此外,由于数据损坏或信道干扰等因素,都可能导致发送端数据与接收端不一致,甚至数据无法完成传输,该现象称为数据包丢失。一般而言一个周期内,数据包丢失的判断依据是数据接收端当前时刻并没接收到正确的数据包,那么多大的丢包概率会对系统的稳定性产生影响,或者说丢包率与系统稳定性有何关系,接收到所有或者部分传递信息是否为控制系统稳定的必要条件,这些都需要进一步研究。

本文主要基于主从均流法设计出的无线DC/DC均流平台(如图1所示),采用由Nordic公司推出的2.4 GHz无线系统芯片nRF24LE1,首先建立了离散时间系统下的丢包模型,然后结合本实验平台对DC/DC系统稳态条件下的数据包丢失概率进行了估算,最后通过实验验证了不同丢包率对主从模块的影响,以及对比了理论计算的最大丢包率与实际实验效果。

图1 高频DC-DC无线并联系统Fig.1 High-frequency DC-DC wireless parallel system

1 离散时间系统数据包丢失的模型建立

网络控制中出现的通信带宽不足或信道干扰等问题会导致数据包丢失,导致系统稳定性能下降。通常采用两种方法分析数据包丢失:①只考虑数据包丢失,将其看作有一定发生概率的事件;②在不忽略时延的情况下,将数据包丢失定量为数据包之间传输时间的允许度。

本文中模型建立只对信号采样端与控制器之间有网络连接且发生数据包丢失,忽略网络传输延迟,控制器输入的变量信号可以表示为

式(2)结合系统控制方程,可得到离散化系统模型为

定义一个新的状态变量:z(k)=[xT(k),T(k-1)]T,结合式(1)和式(3)可得

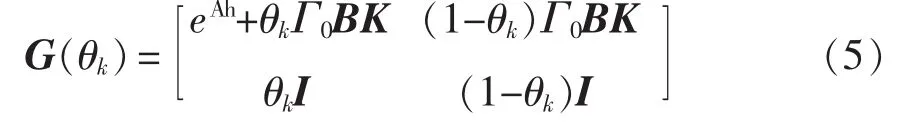

其中,

由于θk∈{0,1},闭环系统会有两种情况发生:E1:θk=0 和 E2:θk=1。假设序列{θk,k=1,2,…}是遍历的,则存在θk∈R,使得。由此可见,当θk∈{0,1}时,θ0∈{0,1}。这样数据包丢失可以看成一种事件的发生概率,其值用θ0表示。式(4)可以表示为

文献[7]的研究结论如下:

引理1若构建一系列非线性方程的设定为真,且有

则系统的式(4)几乎每个解都渐进收敛到原点。

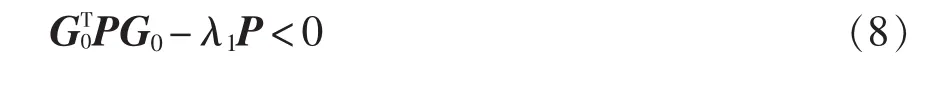

引理 2若(A,B)是可控的,那么(eAh,Γ0B)可控,这样设计矩阵K可采用线性系统理论使eAh+Γ0BK的特征根处于单位圆内;同时G0是一个稳定矩阵,即G0的特征根处于单位圆内,考虑如下线性矩阵不等式

其中,λ1∈[0,1)。假设:对于 λ1∈[0,1),存在一个正定矩阵使得不等式(8)成立,则取

2 系统稳定下数据包丢失概率范围估算

本文研究的是基于主从均流控制的双Buck并联系统,利用上述方法计算在此系统稳定的情况下系统所能允许的主从间最大数据丢包率。本模型只考虑主从模块间数据包丢失的影响,而忽略网路延时对系统的影响。

为了分析数据包丢失对双路Buck并联系统稳定性的影响,首先要建立此并联系统数学模型。根据并联Buck系统的系统框图,可以得出带有PI控制器的系统等效框图,如图2所示。

图2 带PI控制器的双Buck并联系统等效框图Fig.2 Equivalent block diagram of double-Buck parallel system with PI controller

根据图2,系统的状态空间方程为

系统反馈控制方程为

式中:x(t)为系统状态量,x(t)=[iL1iL2vcζ1ζ2ζ3]T,其中,iL1和iL2分别为两并联模块各自的电感电流,vc为并联系统的输出电压,ζ1、ζ2和 ζ3分别为主模块电压环PI控制器、电流环PI控制器和从模块电流环 PI控制器的中间状态量;u(t)为系统输入量,u(t)=[d1d20 0 0 0]T,其中,d1、d2分别为主、从模块开关信号的占空比;

本文中设计的主从模块Buck电路参数为:电感 L1=L2=330 μH,电容 C1=C2=200 μF,线路阻抗 r1=r2=0.5 Ω,负载 R=3 Ω,输入电压 Vin=10 V,输出电压Vm=1;设计的主从模块PI控制器参数为:电压环中,KP1=Kpv=0.56,KI1=Kiv=528;电流环中,KP2=KP3=Kpi=0.106,KI2=KI3=Kii=410。此处为可以忽略传输延时,取电流参考值的发送周期为8 ms。

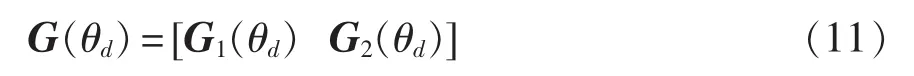

由式(5),可以算出数据包丢失的增广矩阵为

计算结果为

取λ1=0.5,利用Matlab中的LMI工具箱求解式(8)可得

因此可解出 λ2,由式(7)得,θ0的最小允许值为 0.906 5,最后得出 θd允许的最大值为 1-θ0=0.093 5。也即当θd<0.093 5时,本方案下的系统渐进稳定。

3 数据包丢失对并联系统影响的实验研究

由于在上述PI以及系统参数下,系统可以达到比较好的稳定状态,可通过对系统进行不同丢包率的实验来观察具体的实验效果。

前文所述的理论前提是没有考虑控制系统的传输延时,而本实验中对其进行了两方面的实验。首先在慢速网络下进行实验,使网络延时对于均流信息的传输不产生干扰,验证本文从控制理论方面考虑时的最大丢包率;然后在快速网络下观察给定丢包率对该无线并联系统的影响,并对慢速和快速网络状态下的现象进行分析。

3.1 慢速网络下对丢包率的验证实验

通过降低系统主从间均流信息的传输速率,则可暂时忽略延时而着重考虑数据丢包现象,其中数据传输延时约为250 μs,设置数据包传输周期为8 ms,人为设置固定丢包率 θd,如 θd=0.5,表示10 个数据包有5个发生了数据包丢失。

图3是数据包传输周期为8 ms时不同θd下并联系统输出电压及主从模块输出电流波形(采集的是电流经过运放后的电压)。图3表明:当θd=0.5时,在稳态条件下,输出电压出现不稳定现象,主从电流出现较大波动,系统出现振荡;当θd=0.1时,系统经常不定时出现环流现象,但很快能重新恢复均流;当θd=0.07时,系统稳定运行。由此可知系统稳定时允许的最大数据丢包率与理论计算结果 (θd<0.093 5)基本吻合。

从以上实验可以得知,在慢速网络下,当数据丢包越大时,系统越趋于不稳定,当丢包达到一半时系统已经处于不均流状态,由于在慢速网络下数据更新速率已经很慢,当丢包率变高时,系统已经不能得到均流所必需的信息,所以使系统处于不稳定状态。这3种实验可以基本证明系统丢包对系统产生影响的界限以及影响后的效果。

图3 数据包传输周期为8 ms时并联系统不同丢包率下电流稳态波形Fig.3 Steady-state current waveforms of parallel system at different packet loss rates when the data transmission cycle is 8 ms

3.2 快速网络下丢包率对系统影响

当速率提高时,传输延时相对于整个系统来讲也就不能忽略,在实验验证过程中,需要将传输延时考虑进去。快捷网络下的系统数据包传输周期提高到 300 μs,数据传输延时约为 250 μs(传输延时主要与数据的打包与解包相关,而传输速度对于其影响很小)。

图4为数据包传输周期为300 μs时不同θd下并联系统主从模块输出电压电流波形。从实验结果来看,当θd=0.8以及θd=0.9时,系统在暂态过程中无法保持很好的一致性,会出现很大的波动,两者无法达到很好的跟随效果,但在稳态时,两种丢包率下都可以达到比较好的均流效果,通过这两个实验可以很好地证明在快速网络状态下的系统丢包可能产生的影响。

由上述实验可知,在快速网络下,数据丢包对整个系统的影响相对于慢速系统来说,要相对较小。因为在快速网络状态中,数据的更新速率更快,在相同丢包率的情况下,两者之间所接收到的数据量是不同的,快速网络所接收到的数据量更多,对于更高速率状态下的丢包率由于受限于网络延时的影响,不再更深入地讨论。

图4 数据包传输周期为300 μs时并联系统不同丢包率下的电流稳态波形Fig.4 Steady-state current waveforms of parallel system at different packet loss rates when the data transmission cycle is 300 μs

4 丢包解决方案的初步提出

基于上述对丢包进行了实验验证,本文提出了一种对丢包率较小情况下的补偿方案,如图5所示,图中,c(k)为本次接收的信息,e(k)为本次寄存器更新的信息,d(k)为寄存器中上一周期信息。在无线传输中,数据主要被打包在数据帧中,一旦数据丢包发生,接收模块中当系统在相应时间段内需要进行采集和计算时没有检测到相应数据包,检测模块发出数据丢包的信号,将接收模块中在寄存器缓存的上次接收到的均流信息输出,替代从模块当前时刻的均流信息。

该方法适用于较小丢包率情况下系统所采用的方式。当数据在稳态时发生数据丢包率较大以及暂态过程发生较小丢包率的问题下,通过上一周期的数据均可以得到比较好的补偿,因为在稳定状态和暂态丢包率较小情况下数据变化幅度较小,在短时间内均可以得到补偿;但在系统发生比较大跃变时,由于系统数据会产生较大变化,上次储存值与本周期值有较大改变时很难进行补偿。

因此,在初步提出丢包率较小情形下的补偿方案后,需要去解决丢包率较大情形下发生的问题,这在后期研究中需要对其丢包情况进一步分析。

图5 丢包率较小的补偿方案Fig.5 Compensation scheme with smaller packet loss rate

5 结语

本文首先建立了离散时间系统下的数据丢包的模型,并对基于无线主从均流策略及全数字控制的双Buck变换器并联系统稳定下的数据包丢失概率的范围进行了估算;并在考虑网络传输速率的前提下对并联系统进行了实验,在慢速网络下对其实验结果进行了分析,验证了理论估算的系统稳定下允许的最大丢包率以及在不同丢包率情况下对系统所产生的具体影响;后在快速网络下分析了数据包丢失对系统动态、稳态性能的影响,并对在慢速和快速系统下进行了一定对比和总结。通过对这些影响的分析,可以有针对性的解决在无线并联DC/DC系统中遇到的数据丢包问题,对后期的研究具有重要意义。