GaN 衬底上Hf0.5Zr0.5O2薄膜的阻变性能与机理研究

(电子科技大学电子薄膜与集成器件国家重点实验室,四川成都 611731)

阻变存储器[1-2](Resistive Random Access Memory,RRAM)是利用材料的阻变特性进行数据存储的一种非易失性存储器。在外加电场的作用下,阻变材料的电阻值可以在不同的阻值状态下稳定翻转,这种现象就是阻变。RRAM由于具有能耗低、存储密度高、操作速度快、抗疲劳特性好等优点,具有广泛应用前景,被认为是最有可能取代Flash器件的新型非易失性存储器。早期的阻变研究中,二元氧化物由于在开关比、操作速度、疲劳特性等方面有明显的优势,受到研究者的广泛关注。特别是HfOx由于有低至ns的操作速度和超高循环写入次数[3],被认为是未来RRAM器件中最有前景的应用材料。

随着研究的进一步深入,一些铁电相关的阻变器件也逐渐成为研究的热点。近年来在[4]、PZT[5]、BiFeO3[6]、BiTeO3[7]等传统铁电材料中均观察到了阻变现象。铁电相关阻变主要有铁电隧道结、基于铁电薄膜的铁电FET、铁电薄膜相关阻变器件等不同类型。

传统过渡金属氧化物阻变存储器中,阻变机理通常可以用存储介质中氧化还原反应形成的导电细丝的导通与断开来解释。在阻值发生翻转的过程中,电流(阻值)通常会存在一个明显的突变。与此不同的是,在铁电极化调制的阻变器件中,阻变行为的发生通常与铁电极化有关,是基于铁电材料的本征极化特性来实现的,其电流表现为一个逐渐变化的过程,该过程通常可以用铁电极化对界面势垒的调制来解释。因此相比其他类型阻变器件,铁电阻变器件操作速度快,抗疲劳特性、数据保持特性好。

目前对铁电阻变材料的研究主要集中在铁电隧道结[8]。由于铁电材料与半导体材料的晶格不匹配,传统铁电薄膜材料在半导体材料上的生长难度很大,薄膜质量难以保障,器件的数据保持性难以提高。若想得到性能良好的铁电阻变器件,需要采用结构简单、制备容易的铁电薄膜。研究者发现,通过对HfO2材料的掺杂,可以实现铁电性。这些在Si-HfO2、Al-HfO2、HfO2-ZrO2等材料中都得到了验证[9-11],这类材料在Si基上生长工艺简单,容易获得良好的铁电-半导体界面。本文选取HfOx和ZrOx的固溶体[12-13]Hf0.5Zr0.5O2(HZO),采用脉冲激光沉积法(PLD)在n-GaN衬底上生长HZO薄膜,结合铁电极化和电流电压曲线对集成结构的阻变特性进行了研究;通过对其电流电压曲线的拟合,对该集成结构的铁电极化阻变机理进行分析。

1 实验

采用脉冲激光沉积技术在n-GaN衬底上沉积了HZO薄膜,衬底温度为550℃,氧分压20 Pa。所用激光源为德国Lambda Physik公司生产的Complex 201型KrF准分子激光器(λ=248 nm),激光能量为120 mJ,脉冲激光频率为2 Hz。为了便于电学性能的测试,利用电子束蒸发工艺,在n-GaN衬底和HZO薄膜上分别制备了Ti/Al/Ti/Au欧姆电极和 Ni/Au点状上电极,面积约为2.5×10-4cm2。采用原子力显微镜(AFM)对HZO薄膜表面形貌进行了表征。使用美国Radiant Technologies公司生产的RT2000标准铁电测试仪对薄膜的铁电性能进行测试,采用Agilent 4156C型精密半导体分析仪测试薄膜的电流-电压(I-V)特性曲线。

2 结果与分析

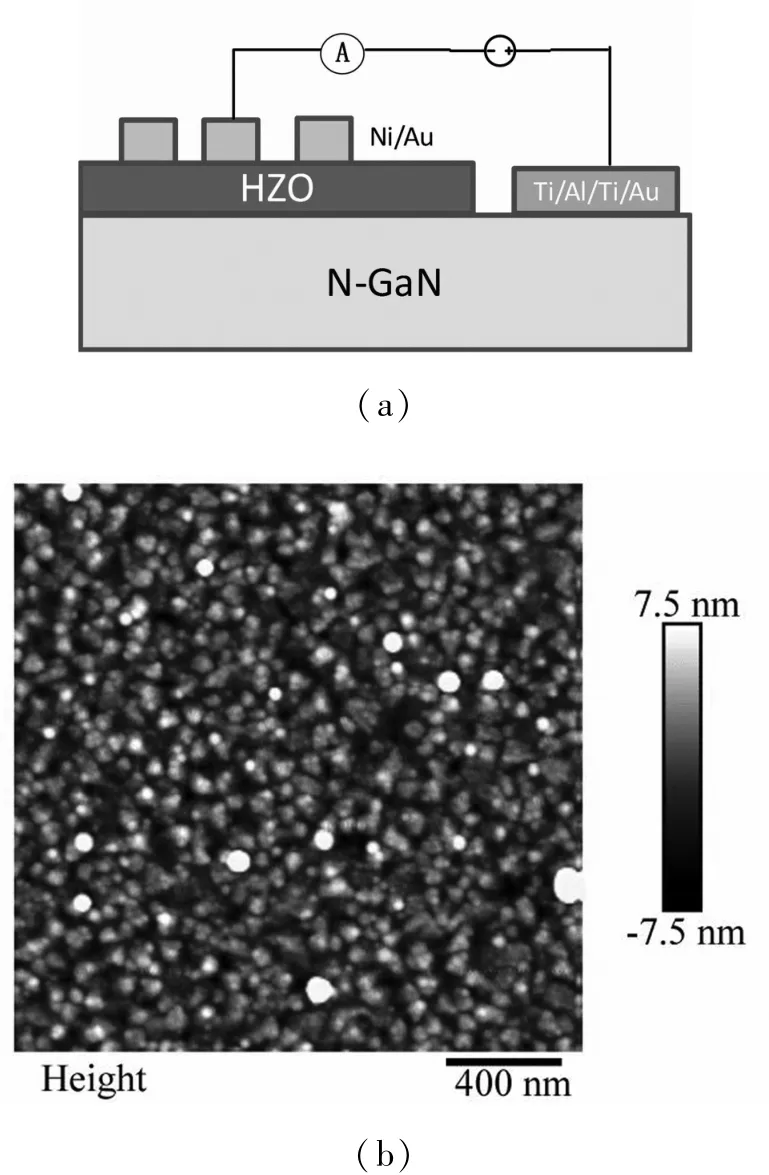

HZO阻变存储器结构示意如图1(a)所示,其结构包括n-GaN衬底、Ti/Al/Ti/Au层构成的欧姆电极、HZO薄膜层、Ni/Au层构成的上电极。图1(b)为HZO薄膜的AFM表面形貌测试图,从图中可以看出晶粒大小一致,均匀饱满,表面平整度高,薄膜结构致密。实现了HZO薄膜的高质量生长。

图1 (a)HZO阻变存储器示意图;(b)HZO薄膜AFM图Fig.1 (a)Stacking configuration of the HZO film;(b)AFM images of HZO film

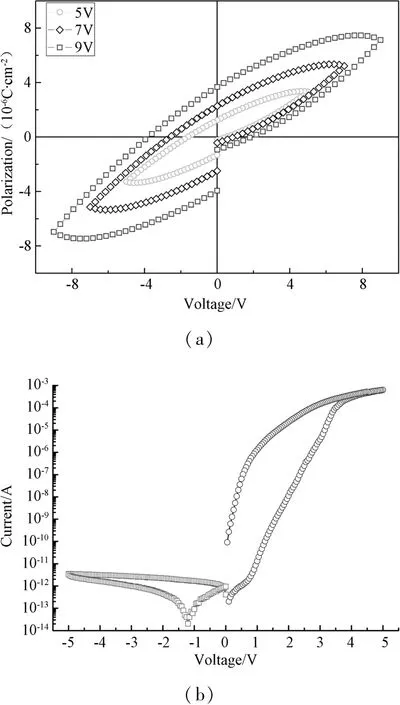

图2 (a)为HZO薄膜在不同操作电压下的电滞回线。从图中可以看出,随着操作电压的升高,HZO薄膜剩余极化强度(Pr)逐渐增大。在操作电压为5 V时,HZO薄膜的剩余极化强度约为3×10-6C/cm2,在9 V时约为7×10-6C/cm2。表明该集成结构具有良好的铁电极化特性。

集成结构在外加电场条件下的电流电压特性曲线如图2(b)所示。测试过程中样品下电极接地,对样品上电极施加Double模式直流扫描,即电压由0 V开始,扫描过程至5 V时再反向扫描至0 V。当外加正向电压从0 V逐渐增大,薄膜电流增大,电阻减小,HZO薄膜从高阻态变为低阻态,此过程为set过程;在从5 V到0 V扫描过程中,器件依然保持在低阻态。在低阻态时对薄膜样品施加负偏扫描电压,电压逐渐升高,样品从低阻态又变为高阻态,此过程为reset过程;在随后的-5 V到0 V的过程中,电流相对较低,器件保持为高阻态。通过施加不同极性外加电压,器件的阻值状态可以在高低阻态间稳定翻转,而在同极性电压的作用下,器件阻态保持不变,表现出明显的非易失性双极性阻变特性。从图2(b)中可以看出,HZO阻变薄膜不需要forming过程即可完成阻态的转变。由于阻变器件的forming过程往往需要较高的电压来实现,使器件存在硬击穿的风险,因此forming-free的铁电阻变器件通常表现出更良好的可靠性。

图2 (a)HZO薄膜在不同电压下的电滞回线;(b)操作电压为5 V时的I-V曲线图Fig.2 (a)P-E hysteresis loops at different operation voltages;(b)I-V hysteresis curves of HZO film with operation voltage of 5 V

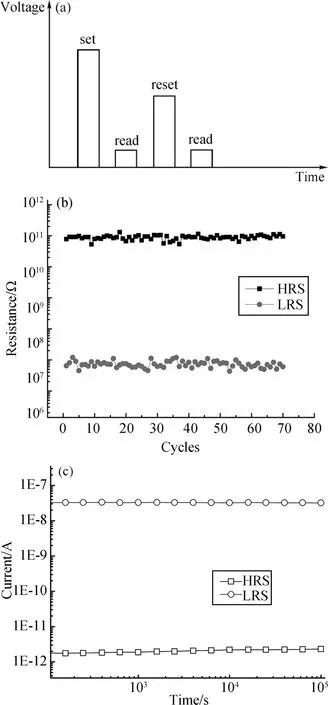

为了进一步探索铁电阻变器件的应用前景,对其抗疲劳特性和数据保持特性进行了测试。抗疲劳特性是指器件在连续重复擦写操作后开关比仍保持稳定的特征。测试过程中分别对器件进行set和reset操作,随后再用0.5 V脉冲电压对薄膜阻值状态进行检测。图3(a)为抗疲劳测试过程中的脉冲时序。图3(b)为薄膜的抗疲劳特性的测试结果。从图3(b)中可以看出,样品的低阻态阻值在107Ω左右波动,波动范围较小;高阻态阻值在1011Ω左右波动,阻值分布很稳定。高低阻态间有明显的隔离,开关比超过了104,80次翻转后窗口保持同一个数量级,器件仍保持稳定。数据保持特性也是非易失性存储器件的一个重要参数,是指在断电状态下器件保存数据不丢失的持续时间。图3(c)为薄膜数据保持特性的测试结果。测试时同样先对薄膜分别进行set和reset操作,再用0.5 V脉冲电压读取样品电流值随时间的变化关系。从图3(c)可以看出,对于HZO薄膜样品,在105s内,其高低阻态的电流随时间基本没有变化,即高低阻态的阻值随时间基本没有变化,为阻变器件数据的稳定保存提供了保障。

图3 HZO薄膜的(a)抗疲劳测试示意图;(b)抗疲劳特性;(c)数据保持特性Fig.3 (a)Schematic diagram of endurance test;(b)Endurance cycles of the HZO film;(c)Retention times of the structure

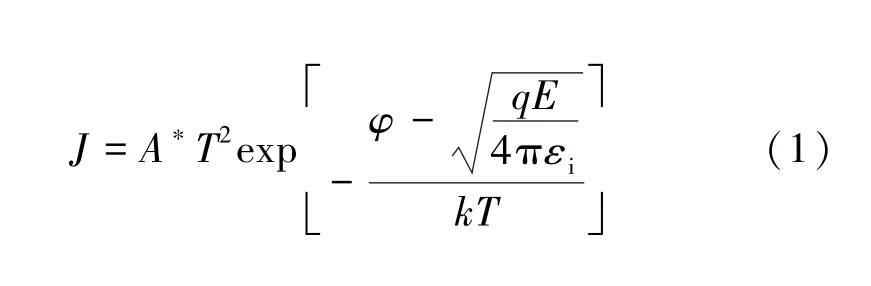

从图2可知,HZO薄膜样品阻值状态是一个逐渐变化的过程,可以推测出其导电机制并非导电细丝型,而可能为界面调控阻变机制,由界面肖特基势垒高度的变化调控阻值的变化。为了进一步阐明其导电机制,对薄膜样品的I-V曲线进行肖特基方程拟合。式(1)为肖特基发射模型中电流密度随外加电场的变化关系[14]。

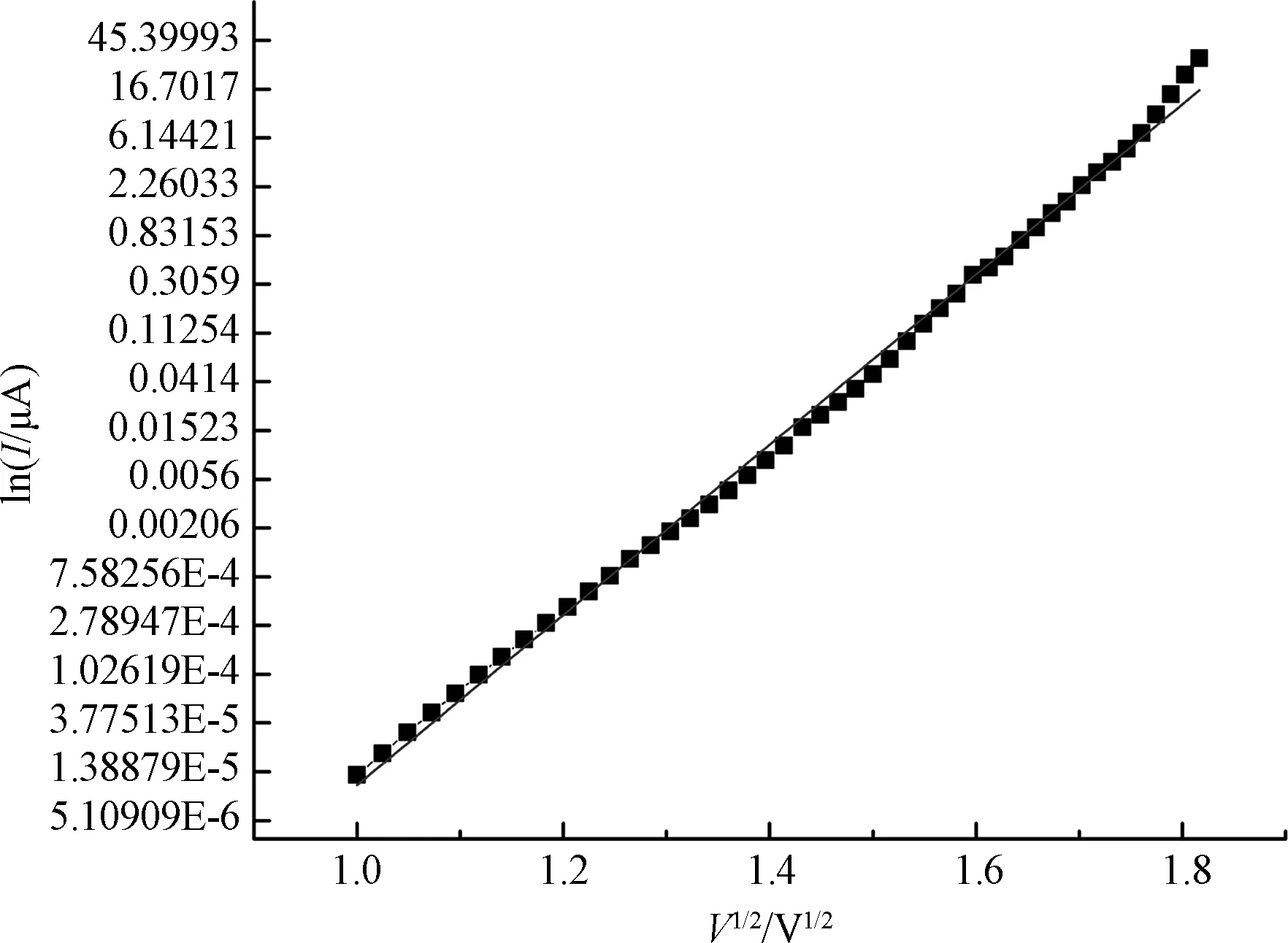

式中:A∗为理查逊常数;T为温度;φ为势垒高度;k为波尔兹曼常数;εi为材料的介电常数;E为电压值。从上式可知肖特基方程中lnJ与E1/2保持着线性关系。对HZO薄膜样品高阻态时的I-V曲线图进行肖特基拟合,其lnI∝E1/2关系曲线如图4所示。从图中可以看出,HZO薄膜的lnI与E1/2基本上满足线性关系,由此可知,HZO薄膜的导电机制满足肖特基发射机制。

图4 HZO薄膜的lnI-E1/2曲线示意图Fig.4 Schematic diagram of lnI-E1/2curve of HZO film

在HZO-GaN异质集成结构中,高低阻态的变化由铁电薄膜-半导体层界面处的极化耦合效应决定。外加电压调控集成结构的极化方向及强度,铁电层与半导体层间的耦合效应决定该界面处载流子的耗尽或积累,使集成结构产生不同的电流状态,从而使集成结构在高阻态与低阻态之间转换。

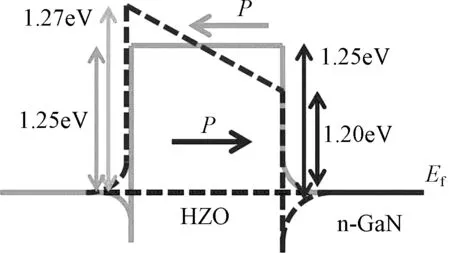

通过对薄膜I-V曲线的肖特基拟合计算,得到四种不同电阻状态下的集成结构界面肖特基势垒,并基于此,构建了界面肖特基势垒的示意图,如图5所示。由此可知,铁电极化调控集成结构界面处载流子的浓度,即为调控界面处的肖特基势垒高度。正偏电压范围内,铁电极化为负向极化时,能带向上弯曲,势垒变高;正向极化时,能带向下弯曲,势垒变低。

图5 HZO薄膜I-V曲线中的势垒示意图Fig.5 Four different Schottky barriers in I-V curves of HZO film

3 结论

本文采用PLD技术在n-GaN衬底上制备了HZO/n-GaN异质结构。通过P-E电滞回线的测试证实该结构具有良好的铁电极化特性,薄膜在不同极性外加电压的作用下,表现出明显的双极性阻变特性。该薄膜的电阻开关特性良好,开关比可达4个数量级。此外,该异质结构还表现出良好的抗疲劳特性和保持时间特性,使其作为RRAM器件有着良好的应用前景。将HZO薄膜的I-V曲线进行拟合,该曲线符合肖特基发射模型,说明该薄膜的导电机制为肖特基势垒发射机制,该薄膜的阻变行为是由铁电极化调控薄膜界面处势垒高度的变化而导致的。