一种新型的可编程遥测收发机设计

罗 亨,齐建中,王 乐,宋 鹏

(北方工业大学 电子信息工程学院,北京 100144)

0 引言

未来各种新型的遥测体制,需要突破无线电通信、计算机等技术的界限,形成技术上的统一,对平台可编程、可重复配置等技术提出了更复杂的设计要求。因此,新型的遥测发射机/接收机必须具备体积小、集成度高、软硬件区别更加模糊、可编程参数更全面等技术特征[1]。文献[2-3]通过一些具有单一功能和固定指标的器件设计了特定波段的遥测系统,从中可以看出,现阶段的系统设计大都基于简单器件+PC处理器架构,整套系统体积大、成本高,工作场景、工作制式受到限制[4],无法满足当今各种可编程、小体积、实时、高速等需求[5]。

本文提出了一种基于可编程的射频芯片(AD9361)+片上可编程系统(SOC)的硬件平台设计方案,在实现该方案时,一方面通过设计AD9361和SOC的外围电路来研制硬件板卡,另一方面通过设计配置程序和基带调制程序来实现软件设计。该板卡的射频频段可以涵盖70 MHz~6 GHz[6],通过软件配置,可以实现任意频率的选择,其通用性、软件可定义性满足了新型遥测体制的应用需求。

1 硬件设计

1.1 系统基本架构

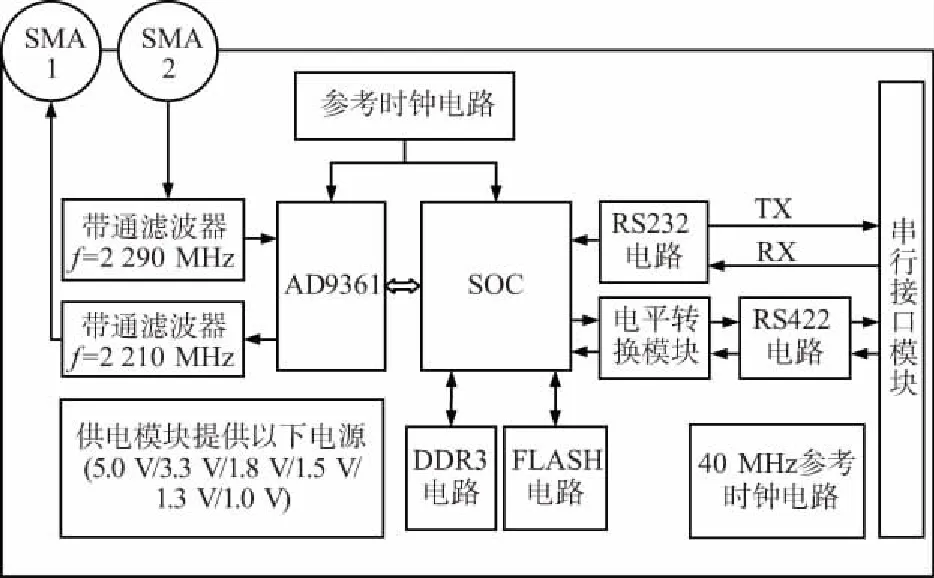

遥测收发机的硬件终端板卡提供一个通用的信息传输平台,其核心主要由射频部分和基带部分2部分组成。射频部分包括射频电路、模拟与数字相互转换电路和数字信号处理。射频电路主要实现对射频信号的滤波、放大和上下变频等功能;转换电路实现对中频信号的模数转换(ADC)、将数字信号转换为中频的数模转换(DAC)、数字滤波和抽取/插值等功能;数字信号处理部分主要完成高速数字信号处理。基带部分采用SOC,实现码型变换、数据加解扰、调制解调、信道编解码、扩频解扩以及与PC机数据指令交互等功能。遥测收发机的硬件框图如图1所示。其中给出了主要的芯片型号、功能以及连接关系。平台的组成除了射频部分和基带部分外,还有时钟电路、接口电路和电源模块。

射频部分主要由一片集成的射频捷变收发器AD9361和2个介质滤波器完成射频信号的接收和发射,2个介质滤波器分别把发射和接收的带宽限定在特定的应用频段,AD9361则完成对发射信号和接收信号的上下变频和对中频信号的滤波、放大、模数数模转换、抽值插取以及数字滤波等。

基带部分由一片XC7ZO30芯片通过数字数据接口同时完成对数字基带发射信号的编码、调制和对数字基带接收信号的解调、解码,并完成对数据的存储和读取。

时钟电路为系统提供稳定的时钟。

接口电路通过RS232接口和RS422接口完成与外界的通信和数据传输。

电源模块为系统各个部分提供稳定的电压,使之能够正常启动和工作。

图1 遥测收发机硬件组成

1.2 射频部分

1.2.1 射频芯片AD9361

使用AD9361作为射频模块能够实现全双工直接变频收发机的设计,并且能够通过SPI总线对AD9361的内部寄存器读写其值来完成对芯片的配置,可配置的关键参数如表1所示[7]。

AD9361内部集成了混频、滤波、放大、ADC和DAC等模块,整体是一个直接变频无线电结构[8]。信号方面,AD9361有4个发射端和6个接收端,发射和接收可设为差分或单端;控制方面,主要是由SPI总线与内部寄存器通信;接口方面,由并行数据接口与SOC通信。AD9361有FDD和TDD两种全双工模式可选[9],适用于各种新型的遥测体制。

表1 AD9361可配置关键参数

参数最小值典型值最大值本振频率/MHz706 000通道带宽/MHz0.256发射幅度/dBm-760ADC工作频率/MHz10.5245.76672DAC工作频率/MHz10.5245.76672采样率/MHz0.215.36125

1.2.2 射频前端设计

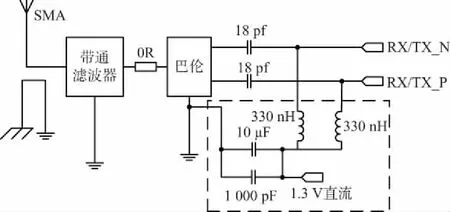

射频前端由一对SMA接口、一对巴伦和一对介质滤波器构成,电路如图2所示。其中,虚线部分框出的是发射部分与接收部分的区别,接收射频前端没有这部分电路。加入这部分电路的原因在于发射部分需加入一个上拉电压来驱动发射的功率,使之灵敏度最高能达到-105 dBm,动态范围达到110 dB。1.3 V直流上拉加在电感与电容之间,能隔绝射频信号,也能达到上拉的作用。

图2 射频前端原理

SMA连接天线接收和发射射频信号;带通滤波器把频率限定在应用的频段,本文应用的频段为发射2.21 GHz,接收2.29 GHz,所以两款带通滤波器的中心频率分别与发射频率和接收频率对应,带宽均为20 MHz,其中,中心频率2 290 MHz的带通滤波器的带外抑制在2 210 MHz衰减≥40 dB,而中心频率2 210 MHz的带通滤波器的带外抑制在2 290 MHz衰减≥40 dB,2种滤波器的带内插损均≤4.0 dB。

巴伦的型号为TCM1-63AX+,是一款射频变换器,其工作频率范围为10~6 000 MHz,可以覆盖AD9361的70~6 000 MHz全频段。作用如下:① 单端信号和差分信号间的互相转换,在接收端,把接收进来的单端信号转换为差分信号,在发射端,把要发射的差分信号转换为单端信号;② 由天线理论知,在偶极天线和同轴电缆之间加巴伦可以扼制掉同轴线外的高频电流,这是由于偶极天线属于平衡型天线,同轴电缆属于不平衡天线,这二者如果直接相连会使得高频电流流过同轴线缆的外皮,从而影响天线的辐射。

1.3 SOC和AD9361的接口实现

SOC和AD9361需要在硬件上实现数字信号的传输,即AD9361的时钟接口、数字接口和控制接口能与SOC的专用IO以及GPIO直接相连[10],故需要根据2个芯片的供电特性定义特定的引脚约束和电平标准。

一方面,在接口设计的过程中,由于ADI已经定义好了AD9361的每个引脚的功能,而SOC的GPIO是按照一定的规则去约束来实现[11],所以,将SOC与AD9361连接的每对连线约束在相应BANK的IO口上,时钟信号需要接在标注有CC的SOC管脚上[12]。另外,考虑到PCB走线的问题,在电路设计时,需要在PCB上走出等长、等间距的差分时钟线。

另一方面,由于AD9361和SOC之间需要实现数字信号的传输,故需要定义相同的电平标准。由于AD9361的电平标准只有高电平1.8 V和2.5 V可选,而SOC的GPIO有高电平1.3 V、1.8 V、2.5 V和3.3 V等多种电平标准可选[13],本文选择了1.8 V高电平的电平标准。因此,AD9361的数字接口电源采用LDO电源1.8 V供电[14],而SOC中与AD9361通信的BANK采用DCDC电源1.8 V供电,并且在引脚约束文件中把定义好的引脚约束到LVCOMS1V8标准[15]。

2 软件设计

2.1 软件框架

软件的设计上以底层HDL驱动为主,分为4个部分:寄存器配置程序、SPI驱动、数字数据接口时序和单音信号的产生。寄存器配置程序至关重要,对AD9361内部多达1 014个内部寄存器进行有规律的读写配置,使AD9361能够工作在应用所需的指标上。SPI驱动部分用于对AD9361的内部寄存器的读写,读取并控制AD9361的工作状态,使之能够工作在应用所需要的频段内。数字数据接口时序部分完成的是SOC与AD9361之间数据的交换,便于基带数据的处理。单音信号产生程序为射频信号提供单音数据,经过本振合成后发射出去。

2.2 关键寄存器的配置字

由于AD9361的寄存器多达1 014个,且有部分寄存器需重复多次读写,一一配置将使工程效率大打折扣,多数寄存器的配置字可以直接用ADI的官方软件生成,而剩下的一些关键寄存器则需要按照要求逐一配置。

2.2.1 RF频率控制字

RF频率控制字控制AD9361内部的RFPLL频率,使射频前端工作在所需的频段范围。RF频率控制字分为整数部分和小数部分,公式如下:

(1)

式中,fRFPLL为所需的射频频率(MHz);fREF为参考时钟的频率(MHz)。Floor为向下取整,Round是取小数。求得的整数部分Ninterger和小数部分Nfractional存入相应的寄存器即可。

2.2.2 基带频率控制字

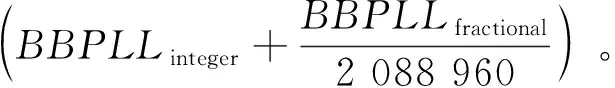

基带频率控制字控制AD9361内部的BBPLL频率,BBPLL可以为ADC、DAC、插值抽取滤波器、数字滤波器以及数字接口提供时钟,使之工作在所需基带频段。基带频率控制字的计算公式为:

(2)

(3)

(4)

同样地,BBPLL的频率控制字也分为整数和小数部分,fBBPLL是所需的BBPLL频率(MHz),fREF为参考时钟频率(MHz)。fOUT为BBPLL的真实频率,可通过CLK_OUT管脚输出,用示波器或频谱仪查看频率控制字是否设置正确、BBPLL是否锁定。

2.2.3 TX功率衰减控制字

TX功率衰减控制字是一个9 bit的二进制字,TX1功率衰减控制字存放在寄存器0x73[D7:D0]和0x74[D0],TX2功率衰减控制字存放在寄存器0x75[D7:D0]和0x76[D0],总共分为360档,精度为0.25 dB/LSB,故衰减幅度的范围为0~89.75 dB。

2.2.4 FIR数字滤波器设计

通过对寄存器0x60~0x65这6个寄存器的重复n次配置,可以生成一个FIR数字滤波器,其中n是FIR滤波器的阶数,其值等于FIR数字滤波器的抽头Taps-1。

Taps=16×(numberoftaps)。

(5)

Taps的最大值为128,也就是说FIR滤波器的抽头数最多有128个,FIR滤波器最高有127阶,0x60~0x65这6个寄存器按阶存入FIR滤波器的系数(cofficients),系数可以用Matlab设计好所需频段的滤波器生成后产生。

2.3 SPI驱动程序设计

SPI驱动程序主要分为读命令和写命令。写命令遵循一种24位格式。前6位用于设置总线方向和需要传输的字节数[16]。接下来的10位数据为写入的地址。最后8位是将被传输至指定寄存器地址(MSB至LSB)的数据。读命令遵循相似的格式,区别在于,前16位在SPI_DI引脚上传输,最后8位从AD9361中读取,如果是4线模式,则在SPI_DO引脚上完成,如果是3线模式,则在SPI_DI引脚上完成。中间5位(第22~18位,其中最高位为第23位)全部默认为0,对读写不影响[17]。

SPI驱动程序主要分为5个状态:idle、调取命令字和地址字、判断读或者写、读寄存器和写寄存器。命令字和地址字事先存在一个命令表中,该命令表包含AD9361所有寄存器的初始化状态。程序的状态机如图3所示。

图3 SPI驱动程序状态机

2.4 数字数据接口程序设计

数字数据接口分为发送接口和接收接口2部分,分别用于向AD9361发送基带数据和从AD9361接收基带数据,既可以工作在FDD模式,也可以工作组TDD模式,2个接口独立工作,互不影响[18]。

接口数据格式是I、Q两路混合传输,如果只用参考时钟的一个边沿触发时序的话,将无法实现先接收I路后接收Q路,而且还无法分离出I、Q两路的数据,此时,有2种可选方法:一种是使用一个2倍于参考时钟频率的时钟,另一种方法是使用XILINX提供的官方DDR原语[19]。其中,发送路径采用ODDR原语,接收路径采用IDDR原语。本文使用第2种方法,混在一路的I、Q两路信号被IDDR分离出来,而分离的I、Q两路信号又被ODDR有序地混合在了一起,这样将便于SOC对信号的处理。

2.5 单音信号发生器

单音信号发生器的原理为DDS信号发生器[20],可以产生任意频率的单音信号。单音信号的频率由频率控制字控制,公式如下:

(6)

式中,FCW为频率控制字;N为信号的位宽,由于AD9361数字接口的位宽为12 bit,故N=12;fdds为单音信号的频率;fclk为数字接口的采样频率。

3 系统测试与验证

根据硬件设计指标,最终完成的遥测收发机硬件实物图如图4所示。

图4 硬件实物

遥测收发机硬件平台静电测试以及电源模块测试完成后,需要对遥测收发机硬件平台的收发功能进行测试。发射和接收的通路测试方案如图5所示。

图5 发射和接收的通路测试方案

发射部分,1 MHz的正弦波经过数字数据接口发送到AD9361,本振设置为2 210 MHz,信号由AD9361的滤波、插值、DAC、上变频、放大后,经过带通滤波器发射出去,在实时频谱分析仪上得到单音频谱如图6所示。

接收部分,由矢量信号发生器产生2 291 MHz的单音被遥测收发机接收,经带通滤波器后由AD9361把接收到的射频信号进行滤波、下变频、ADC、抽取后,再用chipscope采集信号在PC上显示基带信号波形,如图7所示。

图6 发射频谱

图7 接收下变频信号波形

从图6可以看出,发射信号在1 MHz单音信号和2 210 MHz的本振信号上变频后,在实时频谱分析仪上显示出一个2 211 MHz的单音频点,说明发射部分调试通过。

从图7可以看出,接收到的2 291 MHz单音信号经过2 290 MHz的本振信号下变频后,得到的1 MHz正弦信号波形在chipscope上绘制出来,说明接收部分调试亦通过。

测试结果表明,该硬件平台功能完善,既可以实现发射,又可以实现接收,且收发之间不会互相干扰,而且该平台具有很大的灵活性,可以通过软件配置寄存器来改变信号的频率、幅度和速率等。

4 结束语

提出了一种新型的、可以用软件定义的无线电遥测收发机平台的设计方案,并由此完成该平台的硬件实现和底层驱动的实现。通过加载系统测试验证,结果表明了该板卡的优越性,具备可编程和可重新配置的技术特征,可被应用于新体制下的无线电遥测遥控系统。今后可以在该平台上设计SOQPSK、ARTM CPM等新型遥测体制的发射机和接收机,还可以通过增加天线来实现MIMO-OFDM通信系统的设计,具有极大的应用潜力。