一种MCU可测性优化设计

范学仕,刘云晶

(中科芯集成电路股份有限公司,江苏无锡 214072)

1 引言

MCU设计采用IP核的复用技术,大大缩短了复杂芯片的设计周期,提高了设计产量并加快了产品的面世速度,在消费电子、工业控制、医疗设备以及人工智能等领域得到广泛应用[1-3]。MCU具有高集成度和复杂度,使得各IP的I/O端口集成至MCU内部,无法通过MCU芯片引脚直接对各IP进行访问和控制,降低了内嵌IP的可控性和可观性,因此需要内建DFT(Design for Testability,可测性设计)以保证芯片的可控性和可观性[4-6],DFT设计方法与技术成为MCU测试领域的研究热点[7]。

针对MCU的测试方法主要分为两类:基于ATE的外部测试方法[8-9]和基于BIST的内部测试方法[10-11]。

基于ATE的外部测试方法,由被测电路、ATE和ATE存储器3个基本构件组成。该方法将芯片测试数据(包括测试激励和测试响应)存储在ATE的存储器中,由ATE将测试激励注入到被测电路,捕捉被测电路实际响应与测试响应比较,输出测试结果。该方法利用ATE强大的存储和运算能力,采取更为精确的测试评估规则,有效提高芯片的测试故障覆盖率,但同时测试成本较高。

基于BIST的内部测试方法,BIST电路主要包括测试激励生成器、测试访问控制电路和响应特征分析器。当进入BIST测试模式时,由测试激励生成器产生测试向量,经过控制电路传到被测电路,最后由响应特征分析器进行响应分析,得出测试结果。这种测试方法将测试激励的生成、测试访问及测试响应分析在芯片内部采用BIST硬件电路实现,从根本上解决了对于外部ATE设备的依赖,降低了测试成本,但增加了芯片的面积,提高了芯片硬件开销。

本文在测试成本、故障覆盖率和硬件开销之间寻求平衡,将测试资源划分技术[12]和测试端口复用技术[13]引入基于ATE的测试方法中。在控制时间成本的基础上,采用基于ATE的外部测试方法,设计了数字逻辑SCAN链和模拟IP测试模式;在控制芯片硬件成本的基础上,设计了MBIST电路,对Memory进行测试;为更高效地下载程序和功能验证,设计了支持标准SPI协议的通用测试接口;同时结合端口复用技术,对整个可测性设计进行优化,设计了测试模式控制模块,实现多个IP同时测试,以降低成本、提高测试效率。

2 可测性设计与实现

2.1 可测性总体设计

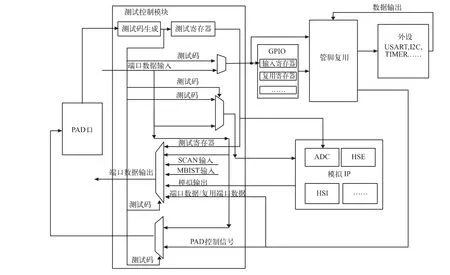

可测性设计总体结构如图1所示,包含具体的控制信号和数据通路。测试控制模块实现对整个测试模式的控制管理,针对不同的测试模式,由测试码生成模块生成不同的测试码,选择进入相应的测试模式。管脚复用模块实现了不同测试模式下相同端口的复用,可以保证在不同封装形式下均可以进行测试。测试寄存器完成对ADC和IO口进行测试。SCAN、MBSIT、各模拟IP的测试通路也在图1中给出,具体介绍将在下文展开。

图1 可测性设计总体结构

为防止芯片在正常使用中误入测试模式以及便于研发人员对芯片进行调试,本文设计了独特的测试模式进入方式,基本屏蔽了用户误入测试模式的可能性,同时也保证研发人员对芯片的调试、失效分析以及其他特殊操作,具体进入方式如图2所示。在上电复位以后,端口1为低电平,可以屏蔽锁定模块端口2的复位信号,此时密钥在端口4时钟驱动下,通过端口3输入到密钥判断锁定模块,密钥匹配后进入测试模式。重新上电复位或者将端口1拉高后按键复位都可以退出测试模式。在测试模式锁定之前,可以将端口2保持低电平输入,让其他逻辑处于复位状态;测试模式锁定后,继续通过端口3打入相应的测试码到移位寄存器,可分别进入各个模块的测试模式。进入相应的测试模式之后释放端口1~4,可作其他输入输出。

图2 测试模式锁定原理图

在内部复位已结束、外部复位使能的条件下,将某个管脚拉低(端口1,屏蔽端口2的复位作用)、另外两个分别作为时钟输入(端口4,归零模式,上升沿有效,共100个周期)和数据输入(端口3),串行输入50 bit的密钥和50 bit的测试模式选择码,电路即进入指定的测试模式;在外部复位结束后,时钟输入被屏蔽、移位寄存器处于保持状态(即寄存器不复位),3个外部输入端口可作其他用途。具体时序图如图3所示。根据不同测试项目输入不同测试码,电路即进入相应的测试模式。

图3 测试模式锁定时序图

2.2 SCAN设计

本文通过在时序单元上增加可测性逻辑,在触发器输入端添加一个2选1选择器MUX,将其替换成扫描触发器,该触发器可工作于正常和扫描测试两种不同模式,SCAN设计如图4所示。

图4 SCAN基本结构

扫描测试模式下扫描使能信号SE为高电平,选择扫描输入SI作为扫描触发器的输入信号;正常工作模式下,SE信号为低,扫描触发器选择原始输入DI作为输入信号。SCAN链用以扫描移入测试向量、捕获并扫描移出测试响应等测试数据,并且输入输出直接连至芯片管脚,实现可控和可观,降低测试向量产生复杂度、提升测试效率。

本文采用Synopsys公司Design Compiler进行SCAN设计,采用Tetramax进行测试码生成。考虑到全扫描测试带来的测试生成困难、测试时间过长、测试成本增加等问题,本文对Vcore区域进行扫描链设计,共一条链,故障覆盖率为87%,总测试码为1100000行。对于未进行扫描链设计的部分,在相关IP测试项中已经包含,可以保证无遗漏。

2.3 MBIST设计

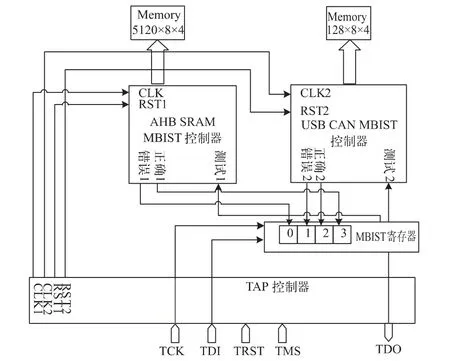

BIST通过在待测电路内部集成测试向量生成、输出响应分析和测试逻辑控制等可测性设计硬件,使待测电路具有自测试能力,在测试时从外部施加必要的控制信号,即可运行内建自测硬件,选择一系列内部生成的测试向量,来检查被测电路的缺陷和故障,其结构如图5所示。

图5 MBIST电路总体架构

TAP(Test Access Port,测试访问接口)是一个通用端口,用来引入控制信号到边界扫描器件并且为边界扫描提供串行的输入(TDI)、输出(TDO)信号。TAP控制器是一个16位的状态机,可以通过TMS和TCK对TAP控制器进行编程以控制其状态,控制进入指令寄存器和数据寄存器的数据流。TAP控制器是MBIST的测试控制中心,每一个SRAM的测试都由TAP来控制。指令寄存器对要执行的指令进行译码,同时可以选择访问相应的数据寄存器。

TCK提供测试时钟CLK。而BIST控制器的复位是由JTAG控制器内部信号产生的。控制信号“测试1/2”是BIST控制器的使能,而在非测试模式下,SRAM的控制器使用的是SRAM IP的CK端时钟,由独立时钟源提供。

MBIST寄存器指令解析器可以直接对2个BIST控制器分别发出指令,因此可以按顺序打开测试使能。测试的结果如测试完成情况、成功与否也将由其综合后,等待TAP控制器发出读取MBIST寄存器的指令,将测试结果以串行的方式输出给TDO。

2.4 模拟IP测试模式设计

本文涉及的模拟 IP主要包括 ADC、HSI、LSI、HSE、LSE、PLL、PVD、LDO、PAD等。由于芯片封装类型的不同,有100/64/48/36只管脚,为保证所有封装的可测性,结合管脚复用技术,以36只管脚为基础,针对各IP分别设计测试模式,可实现各IP的单独测试和共同测试。

各模拟IP的测试模式结构如图6所示,输入测试密钥之后输入IP对应的唯一测试码,根据TEST_MODE_SEL信号选择进入相应的IP测试模式,从端口输入待测信号,测试IP之后再将结果从端口输出。

考虑到 HSI、LSI、HSE、LSE、PLL 的数据均包含频率信号,结合管脚复用技术,设计测试模式管理模块,将这几种测试模式结合到一起,可根据需求自行选择其中一个或多个IP进行测试。PVD和LDO均包含电压信号,可同时测试。ADC支持各通道输入测试,并将转换结果串行输出,同时支持内部参考基准电压和温度传感器的转换输出。PAD的每个控制信号(输入/输出使能、模式选择、上/下拉使能)均可自行配置,灵活高效。除此之外,为测试不同内核工作电压下IP的性能,可联合LDO测试模式进行测试。

图6 模拟IP测试模式结构

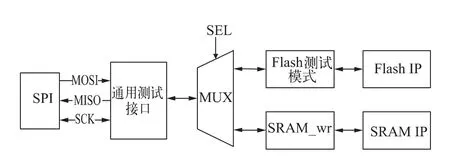

2.5 通用测试接口设计

考虑到芯片FLASH测试、出厂相关配置信息的烧录,以及量产时更高效地烧录用户程序,本文基于标准SPI协议设计了通用测试接口和FLASH测试模式,可以直接与标准SPI进行通信,方便操作,提高烧录效率,降低成本。此外,该通用测试接口可直接将测试程序下载到SRAM,并屏蔽FLASH的读写保护,可以更加快捷迅速地进行功能测试、功耗分析等。其整体结构如图7所示。

图7 通用测试接口连接结构图

通用转换接口支持FLASH 32/64位读、编程、页擦除、全擦除等基本操作和32位SRAM读写操作。SPI采用单主机全双工模式,由MOSI口(芯片管脚)串行输入数据至通用测试接口,由M ISO读出数据至SPI主机,SPI主机非必需,测试过程中可直接由测试及通过管脚进行操作。为防止数据错乱,不可同时通过通用测试接口进入FLASH和SRAM测试模式。具体工作流程如下:

(1)输入测试密钥,芯片测试模式锁定;

(2)输入FLASH或SRAM的测试码,进入相应测试模式;

(3)输入FLASH/SRAM的IP解锁指令;

(4)输入具体操作指令(读、编程、页擦除、全擦除等);

(5)输入操作地址、个数、数据等信息;

(6)执行操作,等待测试结果;

(7)复位,退出测试模式。

3 结果及分析

为验证本文的可测性设计,本文搭建了MCU实验平台,集成了ARM公司Cortex-M 3的32位低功耗处理器、AHB总线、Flash控制器、ISSI的64位某型Flash、32位SRAM及相关外设和IP模型。

图8 进入FLASH测试模式时序图

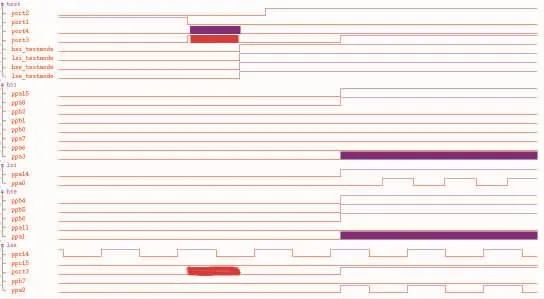

图8 以进入FLASH测试模式为例,说明进入测试模式的时序,Port1拉低屏蔽port2的复位信号,此时在port4时钟的驱动下,由port3输入50位测试密钥和50位FLASH测试模式测试码,匹配正确之后,flash_test_mode信号拉高,进入FLASH测试模式。仿真结果与图3一致。

图 9 以同时进入 HSI、LSI、HSE、LSE 测试模式为例说明模拟IP测试模式管理模块以及管脚复用的情况。由图9可知,4个不同的IP可以同时测试,互不干扰,分别从不同管脚(ppa0~ppa3)输出时钟频率,port3既作为测试模式数据输入,又在LSE测试模式作为相关控制信号,互不冲突。

图9 同时进入HSI、LSI、HSE、LSE测试模式时序图(隐去测试密钥)

图10 FLASH测试模式编程操作时序图

图10 以FLASH测试模式编程操作说明通用测试接口模块工作时序。向FLASH 0x102地址写入64’hfbaa_f000_d004_f8df,在SCK的驱动下,由MOSI按LSB优先原则,每次8位传输这64位数据。同时M ISO反馈FLASH当前状态,空闲输出8’hf0,繁忙输出8’h0f。通过目前商用下载器(JLINK、ULINK 等),每次只可进行16位数据操作,因此通过该通用测试接口下载程序,至少可以提升4倍的下载速度,有效降低成本。

在实际测试过程(中测和成测)中,选用TR6836型测试机进行测试,测试项25项,测试指标50余项,总计测试时间2~3 s,测试结果表明设计的正确性。

4 结论

为降低测试成本,提高测试效率,本文将测试资源划分技术和测试端口复用技术引入基于ATE的测试方法中,基于ATE外部测试和基于BIST内部测试的优点,进行可测性设计,并在实际芯片中得到验证。在控制时间成本的基础之上,采用基于ATE的外部测试方法,设计了数字逻辑SCAN链和模拟IP测试模式;在控制芯片硬件成本的基础之上,设计了MBIST电路,对Memory进行测试;为更高效地下载程序和功能验证,设计了支持标准SPI协议的通用测试接口,结果表明整个下载/测试效率提高至少4倍;同时结合端口复用技术,对整个可测性设计进行优化,设计了测试模式控制模块,实现多个IP同时测试,进一步降低成本。