一种NMOS管体区漏电特性的研究*

李 路,乔 明

(电子科技大学,成都 610054)

1 引言

在高压栅驱动集成电路中,通常需要10~25 V的CMOS器件结构[1-5],电路中高压器件及高压隔离岛占据整个芯片面积较少,中等电压的逻辑控制部分占据了较大面积。随着超大规模集成电路特征尺寸的缩小,将更小的线宽用于高压电路中成为趋势,同时给工艺要求带来更大的挑战[6]。

本文基于0.35μm BCD工艺,制备了用于高压栅驱动集成电路的25 V的CMOS结构,流片结果显示NMOS管反向有较大漏电流产生。针对失效结果进行了仿真分析,找到失效原因,并提出了改进方案,结合方案中新的工艺改进,最终流片结果符合电路应用要求。

2 NMOS的测试仿真分析

2.1 NMOS测试分析

如图1为NMOS结构图,其主要工艺为:(1)P型衬底上注入并高温推结形成N型埋层NBL;(2)生长N型外延层N-epi;(3)注入P型材料推结形成PW;(4)注入N型材料推结形成N-drift;横向隔离采用结隔离技术。

图1 NMOS结构图

图2 (a)为NMOS反向耐压测试曲线,流片测试结果显示,低压NMOS管关态静态电流出现过大的问题,在漏压为20 V时漏电已达1 nA量级。为了明确找出漏电路径,对每个端口的电流进行监测,如图2(b)所示。可以看出,当漏极电压大于10 V时,随着漏压增加,漏电流和体区电流Ibulk也逐渐增加,两者几乎相等。此时源级IS和Vb端电流很小,可以忽略。直到漏压等于36 V左右,器件发生击穿,源级电流剧烈增加,和漏极电流几乎保持相等。结果可初步判定漏电主要来自bulk端体区。

图2 NMOS漏电监测曲线图

2.2 NMOS仿真分析

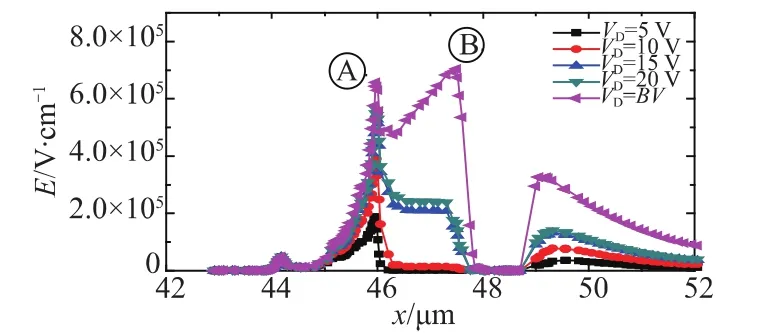

本文采用Tsuprem4工艺仿真,为了方便监测电流,将源电极和体区电极分开。耐压仿真方式为Vb=Vg=Vbulk=Vsub=0 V,扫漏极Vd电压。经过仿真发现,器件表面出现两个电场尖峰,如图3所示。A点位于表面x=45.98μm处,B点位于表面x=47.55μm处(为最终击穿点)。

图3 NMOS仿真结构

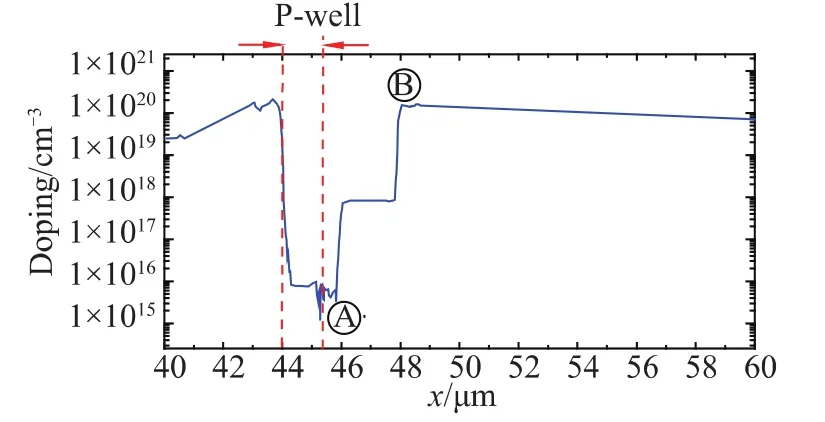

从图4表面掺杂浓度分布图可以看出,A点正处于P-well与N-drift的冶金结处,而B点处于N-drift与N+的交界处。

图4 NMOS表面掺杂浓度分布

图5 给出了器件表面电场随着漏极电压增加的变化情况。可以看出,两个尖峰电场值随着漏压增加而增加。特别注意尖峰A,在漏压仅仅5 V时,尖峰电场值就达到了2×105V/cm,在击穿时最终超过6×105V/cm。可以解释为表面46μm附近,杂质浓度变化巨大,且N型掺杂杂质浓度过大,临界击穿电场会相应地增加。另外,在高漏压时可以看出,B点电场超过A点,最终在此处击穿。

图5 同漏极电压下表面电场分布

图6 (a)显示了器件表面碰撞电离产生率IIG随着漏极电压增加的变化情况。由于IIG与电场强度相关,所以其分布与电场分布趋势一致,随着漏压增加IIG增加。A点处的IIG始终大于B点处。图6(b)显示了不同漏极电压下表面空穴电流密度分布。可以看出,在漂移区A点附近,空穴电流密度显著高于其他地方,且随着漏极电压的增加而增加。空穴电流主要来自于漂移区里的碰撞电离产生的电子空穴对。

图6 同漏极电压下表面IIG分布与空穴电流密度

为了对空穴电流进行监测,进行了矢量仿真。图7(a)为漏极电压15 V时的空穴电流矢量图,可以看出,漂移区中产生的电子空穴对形成空穴电流,经过沟道进入体区P-well,最终流进体电极,形成体电流。图7(b)为击穿时空穴电流矢量图,其空穴电流路径与15 V漏极电压时有明显不同。击穿时,空穴电流流向了N-drift下方的P-well区和P-type区,然后流向体区。

3 NMOS的改进方案

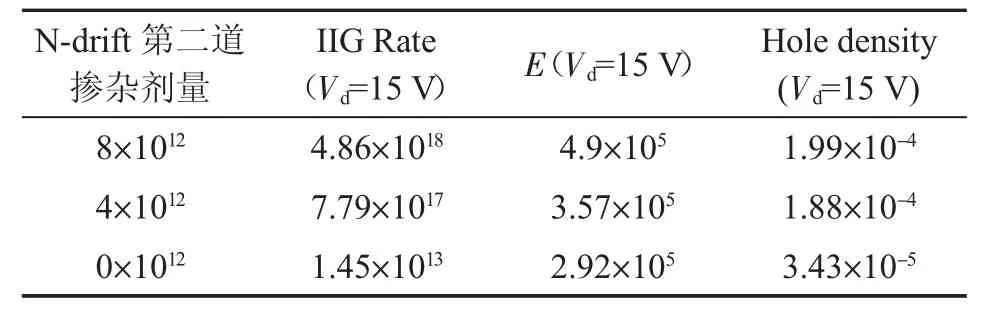

综上分析,并结合测试结果,找到了NMOS漏电的原因,是由于P-well/N-drfit结处电场过大,引起弱的电子空穴碰撞电离,导致漏极静态电流和体区电流增加。针对此原因,改进工艺将降低N-drift的浓度,改进方案将N-drift工艺中第二步注入剂量(8×1012cm-2)降低,见表1。

图7 空穴电流矢量图

表1 不同N-drift掺杂剂量结果

图8 改进后NMOS反向耐压测试曲线

如图8所示,改进后的NMOS漏电问题得到解决,其在漏压为25 V时的漏电流为1×10-12A,达到设计要求。

4 结论

通过仿真测试,分析出了NMOS管漏电的路径主要来自体区BULK端的空穴电流,漏电原因认定为体区内局部电场过高导致电离漏电,通过降低N-drift第二次注入的剂量,NMOS管的漏电问题得到改善。测试结果表明,改进后的NMOS管在Vd=25 V时反向漏电流IDS量级为0.001 nA,满足应用要求。