12位单斜ADC的设计*

陈科全,唐 鹤,郑炯卫,杨 磊,甄少伟,张 波

(电子科技大学,成都 610054)

1 引言

近年来,由于便携式电子产品需求的迅速增长、视频技术的迅速发展以及CMOS工艺制造技术的不断进步,CMOS图像传感器有了很大的发展。而ADC作为CMOS图像传感器中的重要组成部分,它对整个图像传感器的图像质量和运行速度等方面都有着决定性的影响。当今研究的图像传感器中涉及到的ADC分为3类,即像素级ADC、列级ADC和芯片级ADC。单斜ADC作为列级ADC的一种,相对于芯片级ADC,其对ADC速度要求降低;相对于像素级ADC,其提高了填充因子和图像传感器的光电转换效率[1]。

本文提出的单斜ADC结构简单,共用斜坡发生器和计数器的工作方式使得芯片面积小、功耗低,非常适用于对于列宽要求严格的图像传感器;但其缺点是速度慢,对于N位单斜ADC,实现一次模数转换需要2N个时钟周期,转换时间随ADC精度呈指数型增加。提高单斜ADC的速度有两种改进方式可供参考:多斜坡单斜ADC[2]和两步单斜ADC[3]。

2 整体电路结构设计

图1给出了该ADC的电路结构框图,该电路核心模块包括斜坡发生器(ramp generator)、比较器(comparator)、斜坡输出缓冲器(buffer)、计数器(counter)、寄存器(register)和锁存器(latch)。其中斜坡发生器、计数器和缓冲器可共用,比较器、寄存器和触发器每列各一个(只画出了3列)。

图1 单斜ADC电路结构框图

图2 给出了一个3位单斜ADC的工作原理图,工作过程为:计数器在外部时钟的控制下产生数字码,该数字码既是斜坡发生器的输入也是寄存器的输入;比较器依次比较斜坡发生器的输出Vramp与ADC输入Vpixel的大小,比较结果为触发信号Vfall;最后由Vfall控制寄存器保存下对应的计数器输出码,这个数字码就是单斜ADC的输出[4]。

图2 3位单斜ADC工作原理

本设计中采用了一种新型的轨到轨输入比较器,使单斜ADC能够转换满摆幅的输入信号。

3 关键模块设计

在整个ADC中,核心模块包括比较器和斜坡发生器,这2个模块的性能直接影响到整个ADC的性能。

3.1 比较器

比较器可分为静态比较器和动态比较器两类。静态比较器和开环运放类似,电路中一直存在静态电流,功耗大且速度慢;动态比较器只有瞬态电流,功耗较小,由于正反馈其速度较快,但是需要时钟来控制。基于对比较器功耗和速度的考虑,选择采用了动态比较器。

比较器设计中需要考虑的一个关键问题就是失调电压,失调电压主要是由输入对管阈值电压失配和宽长比失配引起的,而一般动态比较器的失调电压为毫伏量级,远大于一个LSB,会严重影响ADC的线性度,因此需要对比较器的失调电压进行校准[5]。同时,随着ADC输入电压量化范围的扩大,由于单斜ADC的输入端就是比较器的输入端,这就要求比较器在大输入电压范围内还能正常工作,然而对于一般的比较器有着阈值电压的限制,当输入电压小于或大于某些值后,比较器输入管不能正常开启,无法得到比较结果。因此本文中的比较器采用了一种新结构,在输出失调存储技术的基础上进行改进,使得比较器同时具有失调校准功能和在轨到轨输入范围内正常工作的能力。

图3给出了新型比较器的电路结构,比较器工作分为两个阶段:复位阶段和比较阶段。工作状态由时钟控制的开关状态来决定,开关S1、S2断开,开关S3~S8闭合时比较器工作在复位阶段,此时采用输出失调存储技术来消除前置放大器的失调电压[6],同时对采样电容进行充电,图4所示为比较器工作在复位阶段的等效电路图。开关S1、S2闭合,开关S3~S8断开时比较器工作在比较阶段,此时将比较器输入信号转换为共模电平恒定的差分信号,经前置放大器AV放大后比较出结果,图5所示为比较器工作在比较阶段的等效电路图。

图3 新型比较器电路结构

该比较器的失调电压来源主要有两部分,前置放大器的失调电压和锁存器的失调电压,其中前置放大器的失调电压VOSA采用输出失调存储技术来消除,在复位阶段时,VOSA通过前置放大器放大AV倍后存储在电容C3、C4上,此时电路表现为零差分输入零差分输出。当开关S5~S8断开后,如果不考虑开关S5与S6和开关S7与S8电荷注入引起的失配,由前置放大器、电容C3和C4构成的电路就表现为零失调电压。

图4 复位阶段等效电路

图5 比较阶段等效电路

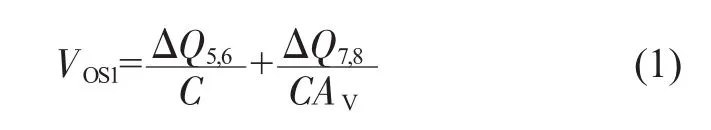

假设电容 C1、C2、C3和 C4的电容值相等且都为C,开关S5和S6注入到电容C1和C2上的电荷失调量为ΔQ5,6,开关S7和S8注入到电容C3和C4上的电荷失调量为ΔQ7,8,开关S5~S8引起的失调等效到比较器输入端为:

这个失调电压很小,可以忽略。而锁存器的失调电压VOSL等效到比较器输入端要除以前置放大器增益 AV,即:

这样大大减小了锁存器的失调电压VOSL。比较器校准后总失调电压为:

若忽略掉值很小的VOS1,校准后比较器的失调电压就是VOS2,只需要调节前置放大器的增益,就可以将比较器的失调控制在需要的范围以内。

该比较器轨到轨输入是通过对输入电压进行转换来实现的,这个转换过程与失调校准同时进行。如图4,复位阶段电容C1和C2存储的电荷分别为:

电阻R1和R2相等,则:

如图5,比较阶段电容C1和C2存储的电荷分别为:

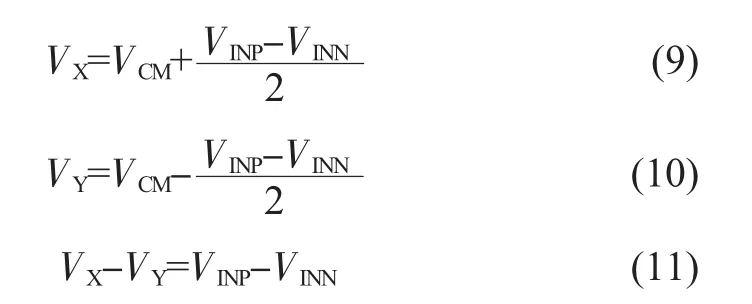

比较器工作状态从复位阶段变到比较阶段后,开关S5、S6断开,前置放大器输入端结点X、Y处无电荷泄放通路,C1、C2存储的电荷量保持不变,即Q1=Q1′,Q2=Q2′,得到:

由公式(9)、(10)、(11)可以看出,对于任意输入信号,最终输入到前置放大器的信号共模电平均为电压VCM,VCM的值由前置放大器共模输入范围决定,这样保证了前置放大器增益恒定,比较器输入范围不会受前置放大器共模输入范围限制,从而实现了轨到轨输入。

3.2 斜坡发生器

斜坡发生器产生的斜坡信号是界定输入信号大小的基准,其线性度直接影响到整个ADC的性能。斜坡发生器的本质是DAC,DAC的种类有很多种,电容型DAC因为匹配好、功耗低而被广泛采用。传统的二进制加权电容阵列所需的单位电容随位数增加呈指数型增加,因此该单斜ADC采用了分段电容结构斜坡发生器,减少了单位电容数量,速度更快、功耗更低、芯片面积更小。

图6给出了12位斜坡发生器的电路结构图,由高8位二进制加权DAC(MSB)和低4位二进制加权DAC(LSB)通过桥接电容连接构成,单位电容个数只有28+24-1,远小于传统DAC所需的单位电容个数212。

图6 斜坡发生器电路结构

可以采用分段电容结构实现DAC的一个关键点在于要保证与桥接电容相邻的两位权重比为2,图6所示的分段方式使得每一位都具有正确的权重,虽然会引入增益误差,但是对斜坡信号的线性度无影响;也可采用其他分段方式,可根据噪声、匹配、寄生电容等多方面综合考虑进行选择[7]。

4 仿真结果

该电路基于0.18μm标准CMOS工艺,使用Cadence进行设计仿真。ADC工作电源电压为1.8 V,消耗总电流约为4 mA,芯片面积900μm×1900μm。为了分析ADC的动态性能,在4.88 kHz采样频率下,输入2.33 kHz满摆幅正弦信号,在ADC输出中取64个点进行快速傅里叶变换,得到输出信号的频谱图。图7为tt工艺角下频谱图,其他仿真条件结果在表1中给出。分析表1数据可以看出,ADC最低有效位数为11.51,可满足性能需求。该结果是在tt下而不是ss下得到,其原因在于,斜坡发生器所用单位电容在ss下的值大于tt下的值(这是由工艺模型决定的),对于电容阵列DAC而言,单位电容越大,寄生电容带来的影响就越小,因此ss工艺角下斜坡发生器输出的斜坡信号线性度更好,ADC的有效位数就更大。

图7 tt工艺角下频谱图

表1 ADC动态参数

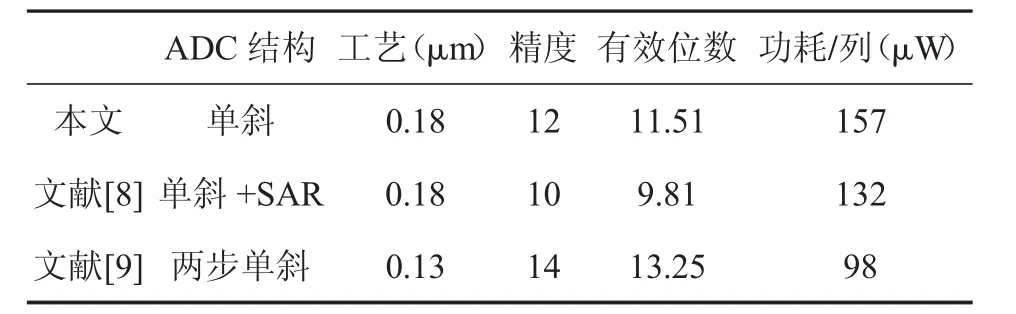

表2 列级ADC性能对比

表2对比了本文ADC与其他列级ADC的参数,其中工艺对ADC精度有一定影响。由于本文单斜ADC中采用的轨到轨输入比较器结构较为复杂,与文献[8]、[9]相比,每列功耗高很多,但是ADC输入信号范围可达到满摆幅,这是其突出点。

5 结论

本文介绍了一种12位单斜结构列级ADC,其斜坡发生器采用了分段电容结构,以提高速度、降低功耗、减小面积;为满足高精度需求,对比较器进行了失调校准,同时增大比较器的有效输入范围至轨到轨,扩大了ADC的输入量化范围。最终ADC电路整体功能正常,有效位数达到了11.51位,满足激光焦平面成像电路的应用场合。