一种无运放输出可调的带隙基准电压源设计

杜士才,方 芳,李 娟

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

1 引言

基准电压源是集成电路设计中非常重要的单元模块,常被用作参考电压、偏置电压等,其温度特性是影响系统控制精度的主要因素,对电路性能有显著的影响。作为系统参考源,通常要求其有较小的温漂系数、较好的电源抑制能力,并满足系统的功耗要求。

传统带隙基准电压源通常采用运算放大器进行钳位,然而运放的失调电压会直接影响基准电压的精度。因此,本文采用无运放结构产生PTAT电流,进而产生与温度无关的基准电压。

2 带隙基准基本原理

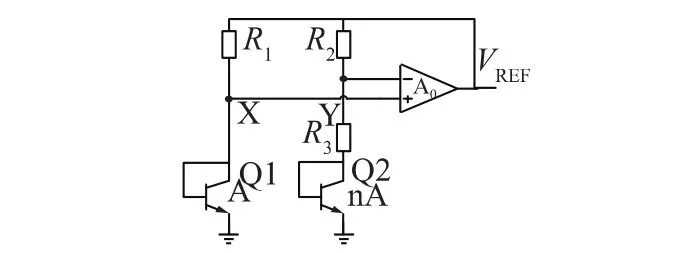

图1为一种传统的带隙基准电路结构。电阻R3上的电流为PTAT电流。

图1 采用运放的带隙基准电路

考虑到运放的钳位作用,使得节点X、Y的电位相等,从而保证电阻R1与电阻R2上的电流相等。从而,带隙基准输出电压如式(2)所示:

该结构要求运放具有增益高、失调电压小的特点。考虑到运放本身的频率补偿会使环路稳定性变差,因此环路补偿较复杂,增加了电路的设计难度。

图2 无运放的带隙基准电路

图2 为传统无运放的带隙基准电路,通过电流镜使A、B两点电位相等。虽然没有使用运放,但由于沟道调制效应,同样会造成基准电压精度降低。

3 电路结构及分析

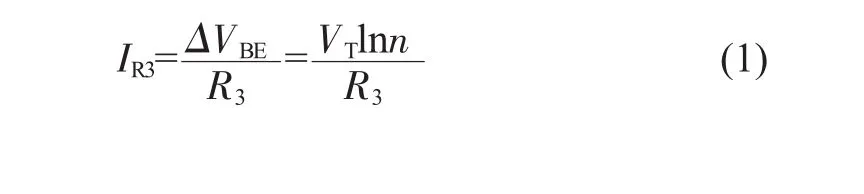

在典型的带隙基准电压源的基础上,设计了如图3所示的带隙基准电压源,包括PTAT电流产生电路、基准电压产生电路和上电启动电路。

图3 新型无运放的带隙基准电路

3.1 PTAT电流产生电路

PTAT 电流产生电路由 MP1、MP2、Q1、Q2以及 R1组成,其中MP1、MP2的宽长比相同。MP3对A点进行钳位,使A、B两点电压均为一个VSGP,避免了沟道长度调制效应对电流精度的影响,从而保证I1=I2。Q2与Q1的发射结面积之比为10∶1,电阻R1上的电流即为PTAT电流:

3.2 基准电压产生电路

Q1、Q2、Q3、Q4晶体管类型相同,且 VBE1=VBE3=VBE4,因此I1=I3=I4。考虑到MP1与MP2为良好的镜像,从而有I1=I2,因此,I1=I2=I3=I4。这4条支路的电流都被汇总到电阻R2上,忽略基极电流,从而C点电压即为与温度无关的基准电压。

输出级采用分压电阻采样结构,从而最终输出带隙基准电压为:

因此,通过调整电阻R3、R4可以调整输出的基准电压值。

此外,该带隙基准引入了钳位电路(MP6、MN1)用来稳定直流工作点。MP6的栅极接输出带隙基准电压,从而X点的电位为VX=VREF+VSGP-VGSN,可保证带隙基准的核心电路工作在一个稳定的电压下,从而使直流工作点在宽输入电压范围内仍然保持稳定,减小了MP1与MP2管的沟道长度调制效应,进而提高了电源抑制比。

该结构包含多个反馈环路。带隙基准核心电路中包含 3 个环路:Loop1(Q1-MP1-MP2-MP3-MN5)为负反馈环路,Loop2(Q2-MP3-MN5)为正反馈环路,Loop3(Q3-MN5)为负反馈。为使环路稳定,正反馈的环路增益需小于负反馈的环路增益。X和Y接一个补偿电容C1,引入一个零点,提高电路稳定性。

3.3 启动电路

启动电路如图3虚线框中所示,由MP8~MP9、MN2~MN4构成。启动过程如下:当各支路电流均为0时,PMOS栅极电压为高,NMOS栅极电压为低,MP8为倒比管,导通电阻很大。当电源电压上电后,由于MP8栅极接地,MP8导通,使得MN2的输入为高,这样使得MN5的栅极电压由高变低,进入到正常工作状态。当MP4的输入降低到一定会程度时,MP9导通,MN3导通,使得MN2的输入变为低电平,关断,启动电路停止工作。

4 仿真结果

电路选用TSMC 0.18μm BCD工艺,采用Spectre进行仿真验证。

带隙基准电压的温度特性曲线如图4所示。其中,第一条曲线为C点电压的温度特性曲线,第二条曲线为输出基准电压的温度特性曲线,两条曲线的变化趋势相同。通过调整电阻R3与R4的比值可以调整输出的基准电压大小。在-55~125℃范围内,输出基准电压约为1.249V,变化量为1.3m V,温度系数为5.8×10-6/℃。

图4 温度特性

图5 为基准电压随电源电压变化波形图。其中,第一条曲线为C点的电压曲线,第二条曲线为输出基准电压曲线。仿真结果表明,在电源电压1.7 V时,带隙基准即可工作,工作电压范围为1.7~6 V。在2~6 V的电源电压范围内,输出电压变化7.74 mV,线性调整率为0.155%。

图5 基准电压随电源电压变化波形图

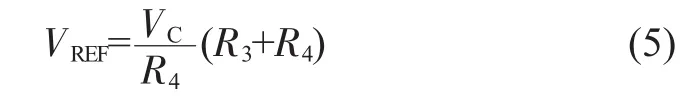

图6 为输出带隙基准电压在不同电源电压下的PSRR仿真结果。电源电压2 V时,电源抑制比为44.48 dB;电源电压4 V时,电源抑制比为53.40 dB;电源电压6 V时,电源抑制比为53.36 dB。

图6 电源抑制比

图7 为典型条件下带隙基准的上电过程。电源电压从0 V开始,经过20μs上电到5 V,带隙基准输出电压在25μs时达到稳定,可实现快速上电。

图7 上电过程

随着电源电压的升高,带隙基准的功耗也会增大。因此,带隙基准在电源电压为6V时的功耗最大。电源电压6 V时,不同工艺脚下带隙基准的静态电流随温度的变化曲线如图8所示。仿真结果表明,静态电流随温度的增大而增大,在ff工艺角125℃情况下静态电流最大,为9.337μA,因此,最大功耗为56.022μW。

图8 静态电流随温度变化曲线

5 结束语

本文提出了一种新型无运放、自偏置、输出可调的带隙基准电压源。该电路具有结构简单、工作电压范围大、功耗小、输出可调等特点,在2~6 V的工作电压范围内,最大功耗小于57μW;典型情况下,温度系数为5.8×10-6/℃,线性调整率为0.155%。