MOS栅控晶闸管在超高di/dt应用中的失效分析

刘亚伟,陈万军

(电子科技大学电子薄膜与集成器件国家重点实验室,成都 610054)

1 引言

脉冲功率技术已广泛应用于环境工程、生物医疗、节能减排、材料制备等诸多领域[1-3]。而在脉冲功率系统中,脉冲开关是至关重要的一部分,它需要具备承受高关态阻断电压、高开态电流密度、高di/dt的能力。火花隙、闸流管等传统脉冲功率开关曾被广泛应用于脉冲系统中,但该类器件同时具有开关速率低、使用寿命短、驱动电路复杂、体积庞大等缺点[4,5]。随着半导体技术的发展,固态脉冲开关器件的低成本、高效率、小体积等特性使其成为替代传统开关器件的绝佳选择。VDMOS、IGBT等固体开关器件因其较大的导通电阻阻碍了其在超高电流峰值、超高di/dt条件下的应用;SCR和GTO等器件由于受电流驱动控制开关开启,增加了驱动电路的复杂性,限制了其应用范围;而MOS栅控晶闸管(MCT)具有导通电阻低以及电压控制的特点,使其在脉冲功率领域得到广泛应用[6-8]。

但MCT器件在超高di/dt条件下放电时,器件栅氧化层极易损坏,本文针对MCT在超高di/dt条件下脉冲放电时器件的栅极失效问题进行研究,搭建测试平台,通过仿真和测试分析回路中器件阴极电感对栅极与阴极之间电势差的影响,建立栅极与阴极电势差变化模型,分析并验证模型中阴极电感和栅极串联电阻在脉冲放电过程中对器件可靠性的影响。

2 MCT器件的失效分析

2.1 MCT的工作原理及测试电路

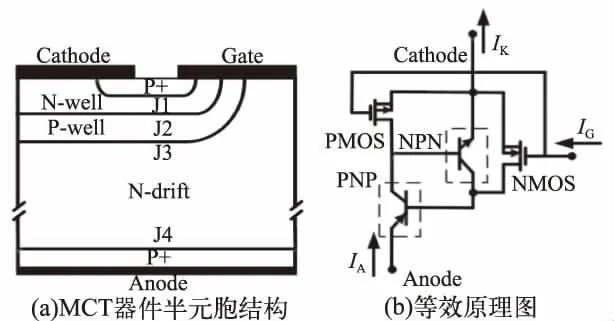

图1是MCT器件的半元胞结构示意图和等效电路图,当栅极与阴极施加合适的反向偏置电压时(VGK<VTH(PMOS)),等效原理图中PMOS开启,此时阳极施加正向电压,MCT结构中寄生PNP双极型晶体管中的J3处于反偏状态,较长的轻掺杂N型漂移区承受器件大部分的偏置电压,器件处于关断状态;当栅极与阴极施加一定的正向偏置电压时(VGK>VTH(NMOS)),等效电路中NMOS开启,PMOS关断;寄生PNP晶体管和NPN晶体管均处于放大状态,形成正反馈回路,MCT器件进入闩锁状态,导通压降减小,电流密度增加[9-11]。

图1 MCT器件半元胞结构示意图和等效电路图

图2为MCT器件脉冲放电测试原理图,关断状态时器件由信号发生器给栅极施加-5 V的反向电压,电压源(supply voltage)给电容C充电,实现电荷存储;当信号源输出+5 V电压时,器件开启,进行电导调制并迅速进入闩锁状态,电容存储的电荷通过由MCT组成的回路释放,完成一次脉冲放电过程。原理图中,电阻R用来控制电压源给电容的充电速度,罗姆线圈不接入放电回路,不影响回路的放电特性,用于捕捉脉冲放电时回路中的电流峰值的大小,同时可以测量脉冲周期,因该器件没有反向导通能力,脉冲放电过程中由电流过冲产生的反向电流通过续流二极管D1泄放,L1和L2分别是放电回路中阳极和阴极的寄生电感;脉冲放电测试波形如图3所示。

图2 MCT器件脉冲放电测试原理图

图3 脉冲放电测试波形图

2.2 MCT在脉冲放电过程中的失效分析

在800 V下单次或多次脉冲放电后,发现器件仍然具有一定耐压,但是已无法开启,将器件的阴极和栅极加扫描电压阳极浮空,测试结果如图4所示,栅极和阴极之间近似呈现短路状态,在去封装后的器件表面可以观察到明显的失效点。

图4 失效器件栅极和阴极I-V特性

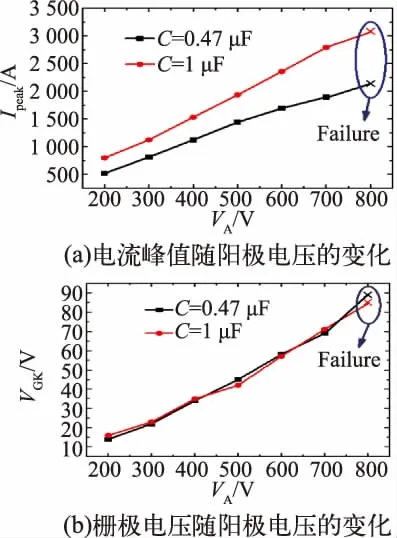

由图5(a)可以看出,电流峰值同为2300 A左右,采用1 μF电容进行连续脉冲测试的器件并未发生失效的现象,可见栅极和阴极之间的短路失效并非由放电回路电流峰值过大发生热烧毁引起的;在图5(b)中,800 V下脉冲放电,栅极的波动电压将近90 V,超过该器件栅氧化层80 V的临近击穿电压,故器件栅极的失效是由栅极与阴极电压过大造成的栅氧化层击穿引起的;又由器件脉冲放电波形中(见图3),栅极与阴极的电势波动与器件的脉冲电流变化呈现相关性,器件在放电时,脉冲电流具有极高的变化率di/dt,推测造成器件栅极失效的电压是由阴极寄生电感引起,阴极的感生电势为:

式中L为阴极寄生电感L2。

图5 不同电容下电流峰值和栅极电压随阳极电压的变化

为验证阴极电感的影响,采用二维器件模拟软件medici对器件的脉冲放电过程进行仿真,分别仿真L2为0 nH和15 nH时的脉冲放电特性,为保证脉冲放电回路中总电感不变,当L2为0 nH时,L1取40 nH,L2为15 nH时,L1取25 nH,放电电压设为1000 V。

图6 栅极和阴极电压随时间变化图

仿真结果如图6所示,当阴极电感为0 nH时,在器件脉冲放电过程中,栅极与阴极之间的电压几乎不发生变化,当L2为15 nH时,栅极电压最大可达75 V,阴极电压最大可达160 V,栅极和阴极两端电压差为85 V,大于该器件栅氧化层的击穿电压,所以阴极电感的存在引起了器件在高di/dt情况下放电时栅极与阴极之间的电势波动,进而造成了栅氧化层的击穿,在放电过程中,di/dt的值是随时间变化的,所以器件阴极的电压也随时间变化,检测的栅极与阴极的电压差也是随时间变化的。

2.3 栅极与阴极电势差变化模型

采用串联分压模型分析器件在放电过程中栅极与阴极的电势差,等效电路如图7所示,其中VIN为输入栅极的控制信号的电压,VG为器件栅极的电压,VK为器件阴极的感生电势,Rg为栅极串联电阻,Zc为栅电容的复阻抗,VK为器件阴极的感生电势,其具体值可由式(1)得出。

图7 器件脉冲放电时栅极和阴极串联分压模型

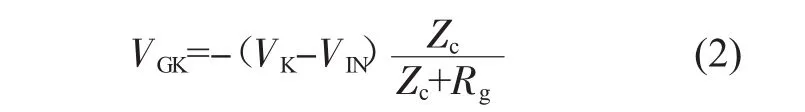

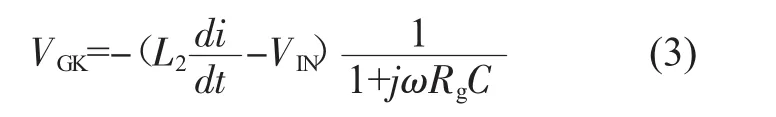

由图7可知,栅极与阴极之间电势差VGK为:

带入式(1)和Zc的值得出:

式中C是栅电容。

图8 栅极和阴极电势差与阴极电感的关系

在保持总回路电感为40 nH不变的情况下,进一步改变回路中的阴极电感L2,观察栅极电流和阴阳极电压差的变化,具体仿真结果如图8所示。由仿真结果可知,随着L2的增大,器件在阴极产生的感生电势也会变大,栅极和阴极之间的电压差也将变大,栅电容两端的电压变化也就越剧烈。

3 栅极驱动回路改进

3.1 减小阴极寄生电感

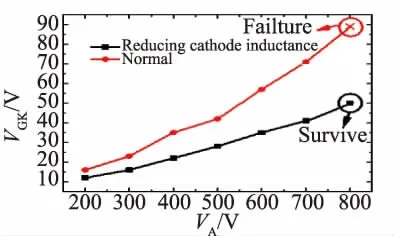

为了验证上述仿真结果并优化放电电路,保证放电回路中总导线长度不变以保证回路总电感不变,通过缩短回路中器件阴极导线的长度进而减小阴极电感,重新测试栅极与阴极之间的电压,结果如图9所示。器件在减小阴极电感的回路中,栅极和阴极的电压差有明显降低,器件在800 V下经过连续多次脉冲放电,仍能正常工作,测试结果与仿真结果一致,说明减小器件阴极回路电感可以有效降低栅极与阴极之间的电压差,避免由于阴极感生电势的影响造成器件失效。

图9 减小阴极电感前后器件栅极与阴极电压差随阳极电压的变化

3.2 增大栅极串联电阻

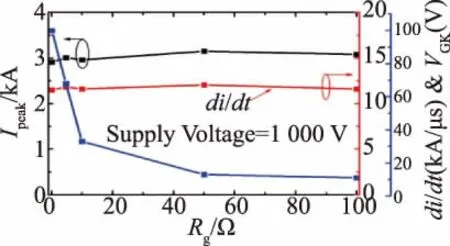

由式3可以得出,在脉冲放电电路设计时,为了降低栅极和阴极之间的电势差VGK,除了适当减小阴极回路中的寄生电感外,还可以通过增大栅极串联电阻的方式来降低阴极感生电势的影响。栅极串联电阻对脉冲放电性能的影响如图10所示。

图10 栅极串联电阻对器件脉冲放电性能的影响

由图10可知,栅极串联电阻可以有效降低器件在脉冲放电过程中栅极和阴极由于感生电势影响产生的电压波动,对放电回路的脉冲电流峰值和di/dt参数无明显影响,但是在实际的器件测试电路应用中,过大的栅极串联电阻会影响开启栅极电压对栅电容的充电速度,使器件的导通延迟增大,因此栅极和阴极之间的电势差与器件的导通延迟时间存在折衷关系,在满足系统对导通延迟时间要求的情况下应尽可能增大栅极串联电阻。

4 结论

本文通过实验和仿真分析了MOS栅控晶闸管在脉冲放电过程中栅极和阴极短路失效的现象,确定了在超高di/dt条件下,由于放电回路中阴极电感的存在产生感生电势,增大栅极和阴极之间的电势差是造成器件失效的主要原因,并建立栅极和阴极电势差变化模型,确定了栅极和阴极电势差与阴极寄生电感、栅电容、栅极串联电阻以及脉冲放电过程中脉冲电流变化率di/dt之间的关系。较小阴极电感和适当增大栅极串联电阻可有效提高MCT器件在脉冲放电时的可靠性。