基于双斜坡采样的像素级时间幅度变换器*

郑炯卫,唐 鹤,刘增鑫,陈科全,杨 磊,甄少伟,张 波

(电子科技大学,成都 610054)

1 引言

近年来,随着人工智能的演进,高级驾驶辅助系统(Advanced Driver Assistance Systems,ADAS)受到了越来越多的青睐。而激光雷达技术可得到外界环境的三维数据,为ADAS、机器视觉等应用提供了感知真实世界的可能。激光三维成像焦平面技术要求有更大的阵列规模、更快的速度、更高的精度以及更大的测量范围。TAC是三维成像焦平面技术的核心模块。而传统的像素级TAC通过采样单个斜坡电压产生,以采样电压代表时间间隔,受限于ADC的分辨率,基于单斜坡的TAC在动态范围和精度之间存在矛盾。斜率较高的斜坡可以实现较高的距离分辨率,但动态范围窄;斜率较低的斜坡距离分辨率较低,但动态范围宽。因此,如何实现高精度、宽动态范围的像素级TAC成为限制焦平面技术发展的难题[1]。

本文提出了一种双斜坡组合方案实现像素级TAC,像素内电路结构简单,只占用很小的芯片面积,便于在同一芯片上集成大量的TAC,这样焦平面技术也更容易做更大的阵列规模。TAC可以实现更高的精度,其最小分辨的时间精度可以达到500 ps,同时TAC又可以实现很宽的动态范围,时间间隔在0~8 μs的范围内均可精确测量,这样便实现了宽动态范围高精度的像素级TAC,在量化电压为11.7 mV时,整体电路实现了14位的有效精度,微分非线性DNL最大仅有0.9 LSB,积分非线性INL最大仅有1.3 LSB。

2 整体电路结构设计

传统TAC是采用单斜坡的方式,依据采样的单斜坡电压的大小量化时间间隔的长短,由于斜坡的摆幅受限于电源电压,TAC的动态范围和精度存在折中,若斜坡的积分时间很长,TAC的动态范围也就很宽,但TAC的精度不高;若斜坡的积分时间很短,TAC的精度会很高,但TAC的动态范围会很窄,本文正是针对传统TAC在精度和动态范围之间的矛盾,设计了一种双斜坡采样的TAC[2-4]。

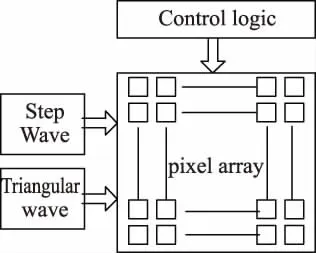

图1给出了该TAC的整体结构框图,包括阶梯信号产生模块(Step Wave)、三角波信号产生模块(Triangular Wave)、像素阵列和控制逻辑部分。

图1 整体电路结构框图

阶梯信号产生模块产生全局的阶梯波,用于判断时间间隔的高6位,三角波信号产生模块产生全局的三角波信号,用于判断时间的低8位,它们均为所有像素单元所共有,其性能直接影响所有像素的有效精度以及线性度,是整个电路最关键的部分。

像素阵列是重复性单元,每个像素阵列均由完全相同的模块组成,由于阵列的规模比较大,单个像素的面积和功耗显得特别重要,本文设计的像素单元中TAC部分仅由两个MOS开关和MOS电容组成,只占用很小的芯片面积,消耗极低的功耗,满足激光三维成像焦平面的需求。

3 关键电路模块设计

三角波信号产生模块和阶梯波信号产生模块分别产生全局的阶梯波信号和三角波信号。像素是重复性单元,由两个采样保持电路组成,两个采样保持电路分别采样STOP信号对应时刻的阶梯波和三角波的电压值,并以此量化每个像素内时间间隔的大小。

3.1 三角波信号产生模块

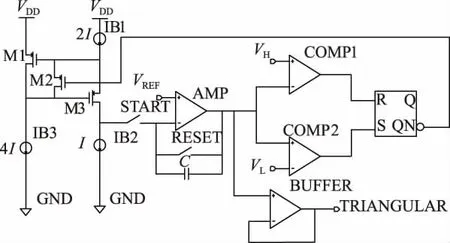

图2是三角波信号产生模块示意图,图3是相应的信号时序控制图,三角波信号的产生分为3个阶段,分别是电路复位阶段、产生三角波阶段和保持阶段。

图2 三角波产生模块

图3 三角波产生模块信号时序图

首先电路进入复位阶段,复位信号RESET为高电平,运算放大器AMP做单位增益缓冲器,其输出端电压被置位到基准电压VREF。

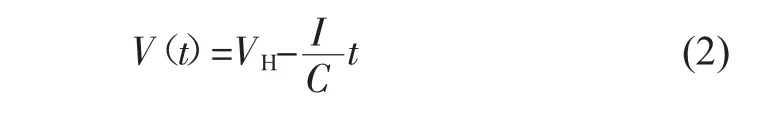

当复位阶段完成后,复位信号RESET和时间起始信号START同时翻转,电路进入产生三角波的阶段,此时运算放大器AMP与电容C构成一个积分器,复位后RS触发器的QN输出端为低电平,此时M3导通,电流源IB1的电流全部通过M2流到电流源IB3,只有电流源IB2的电流I会流过积分器,因电流I不断抽取积分器中电容C上存储的电荷,积分器输出端电压逐渐上升,那么则有:

积分器输出电压不断上升,比较器COMP1不断比较积分器输出电压和上限电压VH的大小,当积分器输出端电压高于上限电压VH时,比较器COMP1输出端电压会迅速翻转到0,即RS触发器的R输入端迅速翻转到0。由于积分器的输出电压一直高于下限电压VL,那么比较器COMP2的输出端电压维持高电平不变,RS触发器处于置位阶段,其QN输出端会迅速从低电位0翻转到高电位1,此时,M2截止,电流源IB1的电流2I开始流过积分器,但由于电流源IB2的电流只有电流源IB1电流的一半,因此流经积分器的等效总电流是大小为I的向下灌入电流,由于不断有电流灌入积分器中的电容C,此时积分器的输出电压产生向下的斜坡,那么则有:

此时,积分器产生向下的斜坡,比较器COMP1输出端又迅速从低电平翻转到高电平,那么RS触发器的R=1,S=1,RS触发器处于保持状态,RS触发器的QN输出端保持为高电平不变,由于比较器COMP1输出端保持低电平的时间很短,因此表现为一窄脉冲信号。

与上升阶段类似,积分器输出电压不断下降,比较器COMP2不断比较积分器输出电压和下限电压VL的大小,当积分器输出端电压高于下限电压VL时,比较器COMP2输出端电压会迅速翻转到0,即RS触发器的S输入端迅速翻转到0,由于积分器的输出电压一直低于上限电压VH,那么比较器COMP1的输出端电压维持高电平不变,RS触发器处于复位阶段,其QN输出端会迅速从高电位1翻转到低电位0,此时M2导通,电流源IB1中的电流通过M3流到电流源IB3,这时只有电流源IB2的电流I会流过积分器,电流I不断抽取积分器中电容C上存储的电荷,输出端电压逐渐上升,此时与刚开始产生斜坡信号的情况相同,实际上,应取VL=VREF,这样便可以产生理想的三角波,那么此时:

类似的,此时比较器COMP2输出端保持低电平的时间也很短,也表现为一窄脉冲信号。

在此过程中,若START信号一直为高电平,那么此过程将会不断地重复下去,积分器输出端电压便交替产生向上和向下的斜坡,因此便产生了三角波信号。

当产生三角波的阶段完成后,时间起始信号START由高电平翻转为低电平,此时便进入了保持阶段,由于时间起始信号START控制的开关关断,此时不再有电流抽取或者灌入积分器中电容C上存储的电荷,积分器输出端电压不再变化。

产生的三角波经过BUFFER后推送到每一个像素内,BUFFER的作用是匹配前后级的负载,隔离后级电路对前级电路的影响。

3.2 阶梯波信号产生模块

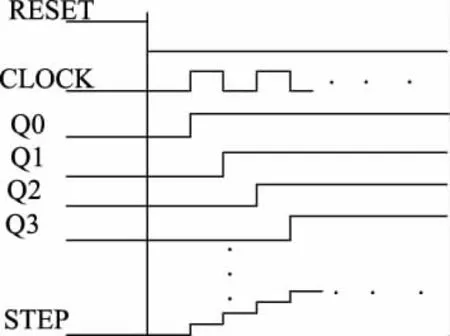

图4是阶梯波信号产生模块示意图,图5是相应的信号时序控制图。与三角波对应,阶梯波的产生也分为3个阶段,分别是复位阶段、产生阶梯方波阶段和保持阶段。在复位阶段,阶梯波和三角波共用同一复位信号;在产生阶梯波的阶段,三角波产生模块中的RS触发器输出端QN为其提供时钟信号CLOCK,不需要片外单独提供时钟,这样既可以减少外部时钟的数量,又可以很好地匹配三角波产生模块和阶梯波产生模块的逻辑电路,降低时钟抖动的影响。

图4 阶梯波产生模块

图5 阶梯波产生模块信号时序图

由于阶梯波产生模块和三角波产生模块共用同一个复位信号,因此在三角波产生模块进入复位阶段的同时,阶梯波产生模块也进入复位阶段,此时所有D触发器的输出电压均复位到低电平,开关S0、S1、S2、S3等均截止,而运算放大器AMP连接成单位增益负反馈的形式,因此其输出端电压复位为VREF。

当复位信号RESERT由高电平翻转为低电平时,此时阶梯波产生模块进入产生阶梯波的阶段,不过此时由于三角波产生模块也是刚进入产生三角波的阶段,其RS触发器的输出端QN还将维持不变,也即时钟信号CLOCK维持低电平不变,那么此时并没有电流流过电阻R,因此运放输出端电压保持为VREF不变。

当三角波产生模块的RS触发器输出端QN由低电平翻转为高电平时,也即时钟信号CLOCK第一个上升沿来临时,此时Q0由低电平翻转为高电平,而Q1、Q2等保持为低电平不变,开关S0导通,这时将有电流I流过电阻R,电阻R上会有压降IR,因此运放AMP输出端电压由VREF翻转为VREF+IR。

当三角波产生模块的RS触发器输出端QN由高电平翻转为低电平时,也即时钟信号CLOCK第一个下降沿来临时,此时Q1由低电平翻转到高电平,而Q0、Q2、Q3保持不变,开关S1导通,因此将有电流2I流过电阻R,电阻R上会有压降2IR,因此运放AMP输出端电压由VREF+IR翻转为VREF+2IR。

随着三角波产生模块的RS触发器输出端QN交替不断地向上向下翻转,也即时钟信号CLOCK交替不断地向上向下翻转,那么上述过程将会不断重复下去,因此运算放大器AMP输出端便产生阶梯波。

当RS触发器输出端QN不再翻转时,时钟信号CLOCK也跟着不再翻转,流过电阻R的电流不再增加,电路进入保持阶段,运放AMP输出端电压也将维持最终电压,不再变化。

产生的阶梯波同样需要BUFFER推送到像素内,BUFFER的作用也是匹配前后级的负载,隔离后级电路对前级电路的影响。

该阶梯波信号产生模块采用温度计编码方式的DAC,相对于二进制编码方式的DAC,这样可以避免短时脉冲波形干扰,输出的阶梯波可以实现很好的单调性、由电流源失配引起的DNL小等优点[5]。

3.3 像素阵列模块

像素阵列模块是重复性单元,每个像素内部的电路完全相同,由于阵列的规模比较大,每个像素单元即使增加很小的面积,对于整个阵列而言芯片增加的面积也是巨大的,因此设计像素时应尽可能选取简单的电路结构。

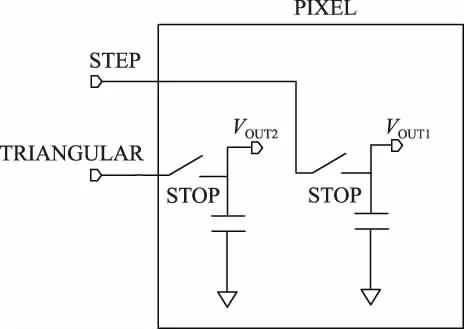

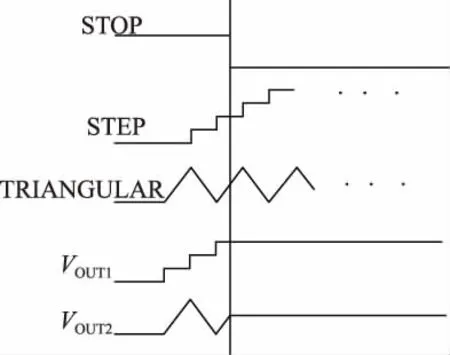

本文选取的像素结构如图6所示,其时序控制图如图7所示。像素由两个简单的采样保持电路组成,每个采样保持电路只有一个开关和电容,其中开关是由CMOS传输门组成,其中NMOS管的尺寸是440 nm/600 nm,PMOS 管的尺寸是 1 μm/600 nm,而NMOS管和PMOS管的最小尺寸均为220nm/600nm,为了消除开关切换时时钟馈通和电荷注入的影响,CMOS传输门两边均加Dummy管,Dummy管的尺寸为CMOS传输门的一半。电容由工作在饱和区的NMOS管组成,考虑到开关切换时KT/C噪声的影响,采样阶梯波电压的电容取40 fF,采样三角波电压的电容取100 fF[5-6]。可见,每个像素内的电路具有结构简单、面积小、静态功耗低的优点,这样像素阵列的规模便可以做到很大。

图6 像素单元结构示意图

图7 像素单元时序控制图

如图7所示,当像素内的时间终止信号STOP为高电平时,开关导通,两个采样保持电路分别随阶梯波和三角波电压的变化而变化,当时间终止信号STOP由高电平翻转到低电平的瞬间,开关截止,两个采样保持电路分别采样了该时刻阶梯波信号和三角波信号对应的电压,然后用采样的阶梯波的电压粗量化时间,用于判断时间所在的区间,用采样的三角波电压细量化时间,以便更精确地判断时间的长短,这样便实现了高精度宽动态范围的像素级TAC。

4 仿真结果

该电路采用了0.18 μm标准CMOS进行设计。三角波信号产生模块中复位的电压VREF和比较器的下限电压均是1 V,比较器的上限电压是4 V,因此三角波每次均是从1 V上升到4 V再下降到1 V,其周期是256 ns,由于三角波要实现细量化时间,量化的精度是8位,因此,时间分辨率应为500 ps,三角波的精度应不低于11.7 mV。

阶梯波信号产生模块中复位的电压VREF也是1 V,每次阶跃的时间间隔是三角波的半个周期,也即128ns,由于阶梯波要实现时间的粗量化,量化的精度是6位,因此阶梯波要实现64次阶跃,考虑到电源电压的限制,64次阶跃后阶梯波上升到4 V,因此每次阶跃的电压高度是46.8 mV。

图8是一个像素的瞬态仿真结果图,START信号和STOP信号的时间间隔是290 ns,根据采样结果来看,采样阶梯波电压值是1.094 V,可以判断出时间处在第二个阶梯上,以此推算出时间的高位是256 ns,采样的三角波电压值是1.797 V,可以判断时间的低位是34 ns,以此便可得出STOP信号是290 ns,即可验证电路设计的正确性。

图8 瞬态仿真结果

积分非线性(INL)是实际有限精度特性曲线与理想有限精度特性曲线在垂直方向上的差值,微分非线性(DNL)是在每个垂直台阶上测量的相邻编码之间的距离。

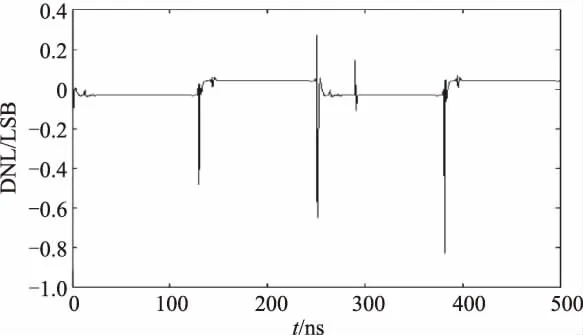

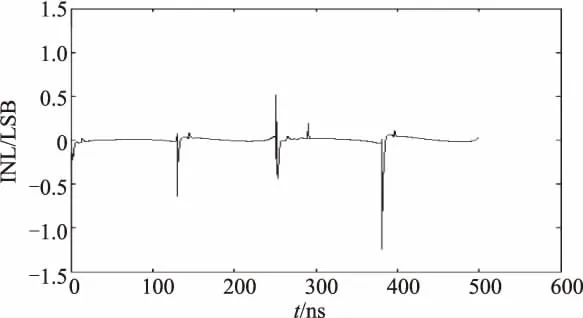

由于三角波具有周期性,其DNL和INL关系曲线也是不断重复的,因此分析其INL和DNL时不需要在整个时间段内进行分析,本文接下来分析其在0~500 ns内的DNL和INL,也就是其前两个周期内的结果。对于固定的时间间隔,也即START信号与STOP信号之间的时间间隔固定时,该TAC会得到一个采样结果,以此采样结果可还原出时间间隔,通过不断改变时间间隔的长短,会得到一系列的采样结果,并以此还原出一系列的时间间隔,把还原出的时间间隔与设定的时间间隔进行分析,便可得到该TAC的INL和DNL关系曲线,图9是该TAC的DNL关系曲线,图10是该TAC的INL关系曲线,其中LSB是11.7 mV。

图9 TAC的DNL

图10 TAC的INL

当时间间隔很短时或者时间间隔处于阶梯波的阶跃点和三角波的拐角点,此时DNL和INL稍差,这是因为系统由一个状态切换到另一个状态需要时间响应,等系统状态稳定以后,其DNL和INL会很小。根据仿真结果可以得到,DNL最大有0.9 LSB,INL最大有1.3 LSB,这已经是非常好的结果,满足绝大部分场合下的应用了。

以上仿真和分析是基于单个像素而言的,整体上TAC实现了14位的分辨率,其中阶梯波实现了高6位的精度,三角波实现了低8位的精度,TAC时间分辨率的精度达到了 500 ps,动态范围也有 0~8 μs,DNL是0.9 LSB,INL是1.3 LSB。

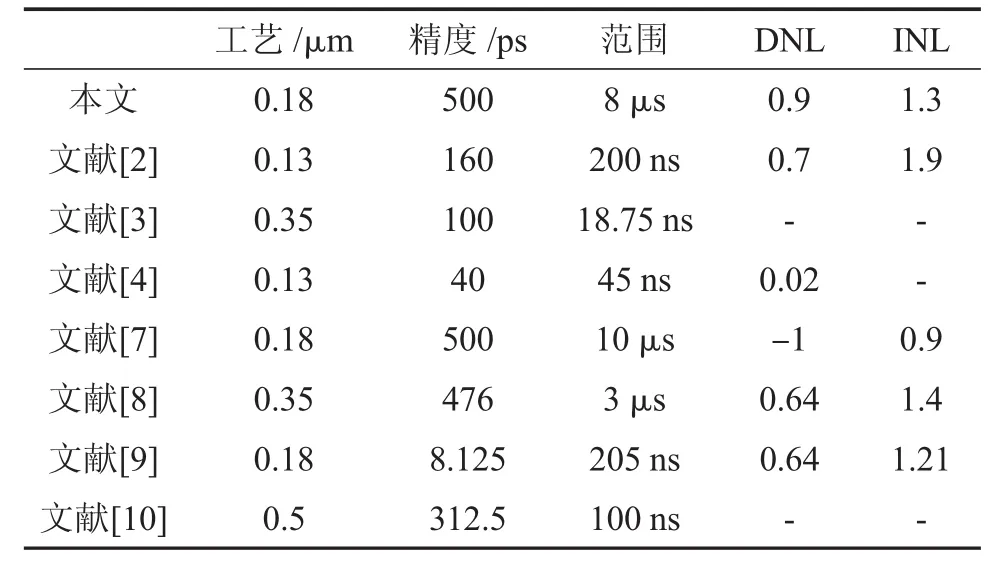

表1是本设计与先前的文献对比的结果,文献[2]~[4]是通过传统的单斜坡的方式实现的TAC,虽然能实现很高的精度,但其动态范围很有限,文献[2]的动态范围最大,也不过200 ns,远不能满足焦平面读出电路的需求;本文和文献[7]均是采用三角波进行时间的细量化,指标接近,但文献[7]是通过数字的方式进行时间的粗量化,需要6 bit的计数器,这对焦平面读出电路而言,像素面积是无法接受的,文献[8]~[10]虽然也能做到很高的精度,但是其动态范围也很窄,亦不能满足焦平面读出电路的需求。本文中的TAC动态范围可达8 μs,精度也可以达到500 ps,解决了激光三维成像焦平面读出电路的需求。

表1 该电路与先前电路的对比

5 结论

文中介绍了一款高精度宽动态范围的像素级TAC,其原理是用双斜坡组合的方案量化时间,采样阶梯波粗量化时间,采样三角波电压细量化时间,整体上TAC实现了14位的精度,最小分辨精度500 ps,动态范围是8 μs,DNL最大是0.9 LSB,INL是1.3 LSB,实现了高精度宽动态范围的像素级TAC。电路整体功能正常,满足激光焦平面成像电路的应用要求。