基于ATE的FPGA测试技术研究和应用

王 华

(上海华岭集成电路技术股份有限公司,上海 201203)

1 引言

FPGA的可编程性给FPGA本身完整和全面的测试带来诸多挑战,FPGA测试必须考虑各种故障模型以充分检测这些器件以及器件缺陷的容错能力,逻辑资源必须在不同的运作模式下进行测试,而这又导致需要对FPGA中被测逻辑资源进行多重重新配置。

自动测试设备(ATE)具有高集成度、高效率等优点,被广泛用于集成电路测试验证分析和大规模产业化测试,在对FPGA器件的测试技术开发中,由于自动测试系统本身向量存储深度的限制,FPGA对不同资源和故障覆盖的检测需要重复配置,相应的配置位流长,配置文件多,自动测试系统很难一次将所有配置文件加载进测试系统内存中,从而不得不多次加载,导致测试时间成倍增加。芯片的测试成本是由整个芯片的测试时间决定的,因此如何一次性尽可能多地加载配置向量,更快完成测试过程中对FPGA的配置成了FPGA测试中必须解决的问题。

2 FPGA测试流程

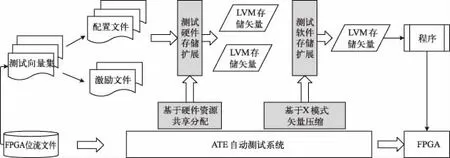

通常情况下,FPGA测试过程中除少数直流参数(如上电电流、电源静态电流)不需配置FPGA外,其余依照功能/参数测试项的要求,通过下载位流将被测FPGA配置为对应的状态,然后再进行测试。功能测试时需要对被测FPGA施加激励并检查其输出是否符合预期。部分参数测试需要在施加激励且输出符合预期的情形下进行参数的测试。对于上述两类情况,都要开发对应的功能测试向量集,可以分类为配置向量和激励向量。

图1 FPGA基于ATE测试开发方案

FPGA测试位流开发流程是通过EDA软件使用硬件编程语言对设计进行编程,通过转换工具生成测试用bit位流文件。进入测试阶段将设计生成的位流文件转换为自动测试系统的矢量文件,自动测试系统将矢量文件加载进测试系统大容量矢量存储(LVM)中,在测试过程中将矢量文件下载到FPGA中,实现相应的电路功能,从而完成测试验证,测试流程如图1所示。这其中占用测试系统80%以上的LVM存储资源是对FPGA进行配置的矢量部分。

现有技术中,实现FPGA的配置方法有很多,根据器件的类型和应用场景,各FPGA厂家均提供了多种配置方法来实现对FPGA的配置,以XILINX公司Virtex-4系列为例,主要有以下几种:JTAG方式、主串方式、从串方式、并行方式。JTAG、主串、从串这3种配置方法都是采用串行的数据传输方式将配置数据加载到FPGA芯片中,由于数据位宽限制,配置时间较长,并行方式可选择8位或32位的数据位宽,配置速度较快。由于配置数据宽度的不同,所生成的位流大小也不一样。以Slave Select MAP32进行配置,一次通过32个信号作为配置数据位流的输入,每个信号的长度最大到709 464位,位流的长度反映到ATE测试系统上就是矢量深度,每个信号以周期形式进行划分,存储到LVM内存中。

经过周期化处理后的文件为测试系统可以识别和存储的格式,目前自动测试系统存储测试矢量的方式是为每个信号分配独立的存储空间,一个周期存储1 bit数据,1024 bits为1 k存储深度,即1024个周期的测试矢量。

图2 XILINXV4系列配置数据大小

自动测试系统用于存储测试矢量的大小通常受到限制,为了解决FPGA向量存储深度的问题,一方面自动测试系统供应商增加测试系统的存储深度,提高存储深度相应增加设备的成本,另一方面从测试方法上寻求解决的办法。目前针对FPGA测试配置矢量下载的一种方式是在测试DUT板上扩展外部适配器,该方法是将FPGA测试所需要的配置文件储存在一个存储器阵列,测试系统在测试时通过选择配置文件对待测FPGA芯片进行测试前的配置,该方法解决了FPGA配置向量大、测试系统无法一次加载的问题,但由于要在测试过程中实时测试系统与配置模块交互,降低了测试效率;另一种方法需要在测试前期就考虑开发专门的硬件,增加了开发的周期和额外的开销。

3 基于ATE的测试矢量扩展解决方案

为克服由于测试系统LVM存储深度限制导致FPGA测试过程中重复加载测试矢量的情况,本文研究了FPGA测试矢量存储扩展方案,对FPGA这类配置向量深度有特殊要求的器件通过硬件设计和软件方法扩展FPGA配置管脚占用的矢量存储深度,在不增加外部硬件的基础上,减少测试过程中重复加载测试向量的次数,将占用测试向量深度较小的资源分享给配置管脚使用,提高资源的利用率从而提高测试效率。

3.1 基于测试系统硬件资源扩展方案

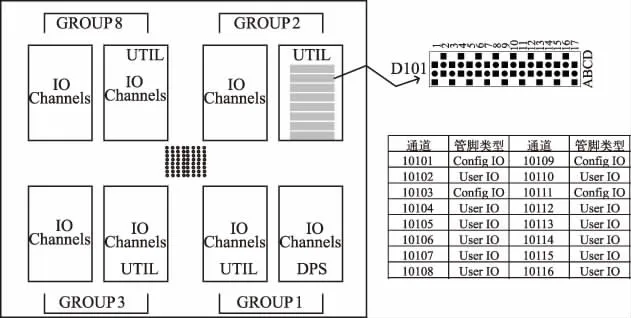

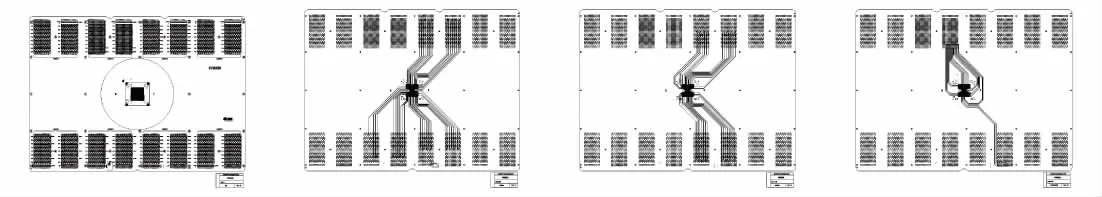

基于测试系统硬件资源共享分配方案是在爱德万V93000测试系统本身硬件支持的基础上,通过硬件上每8个通道为1组可以相互间共享测试向量深度,其分享原理是将非配置管脚空余的存储资源分享给配置管脚使用。为了充分最大化利用存储资源共享功能,基于芯片测试要求和测试系统的硬件设计规则,由于FPGA器件涉及到差分测试的需求,而测试系统差分硬件设计上要求差分对必须在同一组信号中,故为每2个配置管脚分配到一组共享单元中,如图4所示为硬件资源分配方案,图5为本文研究的XC4VSX55_FF1148千万门级FPGA器件基于该方案的部分Layout图纸。

图3 测试矢量存储扩展方案

图4 测试硬件资源分配方案

在测试过程中,配置信号和非配置信号在软件方面涉及到多个方面的特殊设置,在测试程序Pin定义文件中将配置管脚和非配置管脚以port的方式独立出来;其次,开发专门的脚步软件对测试矢量按照独立的port从原始向量里提取出来,通过这种方法可以在软件上实现独立对单个port的向量进行运行,而不受到不相关信号的影响。通过存储资源分享的方式,可以实现为每一个配置管脚使用到4个测试系统通道的存储资源。

图5 XC4VSX55测试板Layout部分图纸

3.2 基于测试软件的矢量压缩方法

基于测试软件的矢量压缩方法是通过X模式的矢量压缩,将多个器件周期适配到单个测试系统周期。“X”表示乘法,“X4模式”表示每个测试系统周期有4个器件周期,X模式的目的是更快地运行测试并更高效地使用内存。如果测试系统周期以8 ns的间隔发生,则器件周期将在X4模式下以2 ns的间隔发生,在X8模式下以1 ns的间隔发生。一个器件周期即表示1 bit的位流数据,测试系统矢量存储器的使用类似地被压缩,在X8模式中测试系统的112 MV存储器适合于896 MV的测试器件存储深度测试需求。

这种乘法效应是通过使用多个驱动/接收边缘来实现的。例如,如果使用X8模式是使用了8个驱动边沿,包含一个脉冲的器件周期可以在测试系统周期内出现4次。“X”值越大,每个测试系统周期所需的边越多,图6显示了X1、X2、X4和X8模式。

图6 测试系统X模式示例

X模式通过增加驱动和接收触发事件沿来增加测试系统单个周期内的器件周期数,这种应用会带来更复杂的矢量数据组合和测试时序关系。首先,对于自动测试系统而言,0/1作为输入驱动信号,L/H/X作为输出判断信号,FPGA器件配置矢量使用到的管脚除了CFG_DONE、INIT_FLAG等几个信号作为配置状态判断的信号是输出信号,其他都是作为输入信号,没有双向的输入输出管脚,这样在定义波形组合的时候只需要考虑0/1的组合,而不需要将0/1和L/H/X进行组合,大大减少了组合器件周期的数量,满足测试系统Waveform的限制要求。

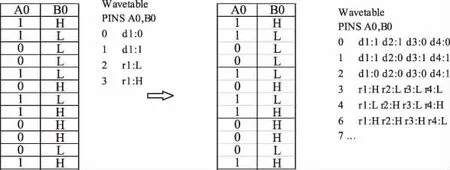

图7 X1模式向X4模式转换方式

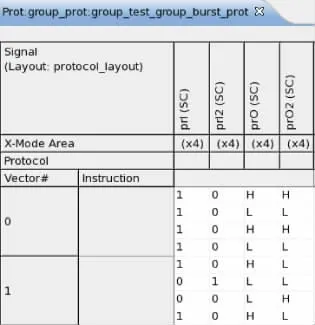

在测试时序方面,原本单一周期只有一个数据,相应的为这一个数据定义一个d1事件时间,现在X4模式下包括4个数据,这需要4个事件时间(d1、d2、d3、d4 或者 r1、r2、r3、r4) 来定义整个周期的时序。FPGA器件在从并配置模式下,器件时钟由外部测试系统提供,由于时钟是脉冲信号,每个脉冲时钟需要2个时间驱动来完成,相应的在X4模式下时钟需要8个驱动时间,为了保证测试稳定性,数据输入建立时间和保持时间时序相对于时钟信号余量应尽量充足,经过X4模式转换生成的测试向量在测试系统中显示如图8所示。

图8 X4模式下矢量存储方式

4 应用实例分析

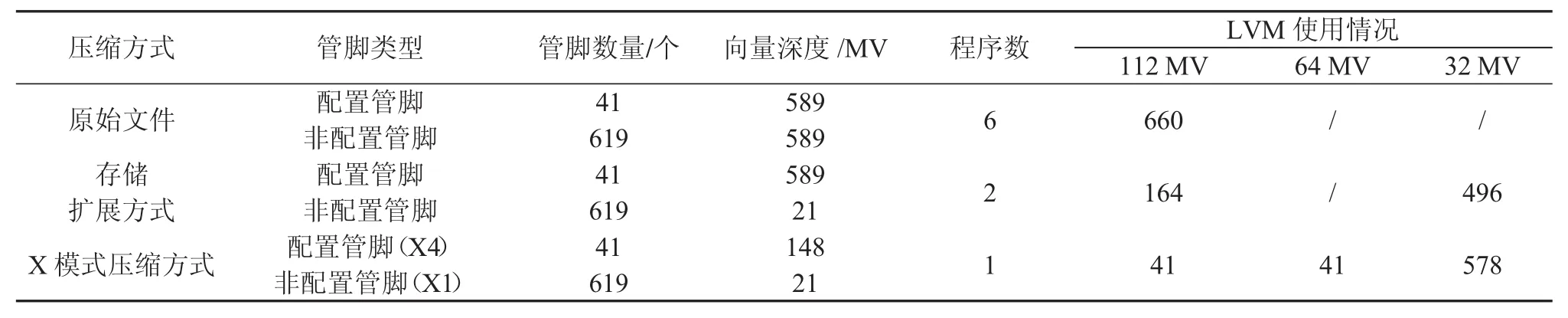

本文研究的XC4VSX55_FF1148千万门级FPGA器件采用BGA1148封装,除去电源和地管脚,其IO管脚共计660个,用于配置的管脚主要包括M0/M1/M2、CFG_DONE、GCLK、INIT_FLAG等信号作为配置控制或者状态观察,选用Slave Select MAP32配置模式,还包括32个管脚作为配置数据输入,总计41个管脚作为配置使用,测试配置位流文件通过这41个配置管脚下载到FPGA内部,其他信号在配置期间处于浮空状态,开发平台采用爱德万公司V93000自动化测试系统。

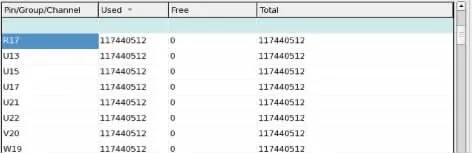

如图9所示为配置管脚存储空间使用情况,R17、U13、U15等本身存储空间为117440512/(1024×1024)=112 MV,在load完测试pattern后,存储空间已被全部使用。图10为非配置管脚的存储空间使用情况,可以看出,因为用于分享给配置管脚的存储空间不一样,所以使用到的存储空间也不相同。

图9 配置管脚存储空间使用情况

图10 非配置管脚存储空间使用情况

图11 存储空间具体分配情况示例

图11列出了其中一组信号内(8个相邻通道10301~10308)的资源分配情况,R17配置管脚本身需求存储空间大约320 MV左右,在使用完本身存储空间以后,实际占用了其他7个信号总共210 MV左右的存储空间。

在存储扩展的基础上,再采用X模式的方式针对配置管脚向量进行X4模式的转换,则可以将向量存储深度需求进一步压缩,测试系统存储深度License需求也进一步减少,一个程序就可以将所有配置向量加载完成。

表1 FPGA不同方式下存储资源使用情况

5 总结

本文旨在针对大规模现场可编程FPGA器件在自动测试系统测试验证分析过程中,对ATE存储向量深度的特殊需求,在没有特定工具和下载方式的情况下使用测试系统本身的扩展模式和功能,通过硬件设计和软件编程的方法在自动测试系统中对FPGA测试提供重复配置测试解决方案。整个测试过程可以通过单个ATE上载所有测试用例矢量一次完成,而不会中断每次功能测试之间的测试过程,并且在测试资源使用上达到成本和效率的最优化,该方案在自动测试中提供了巨大的优势。