基于SOC的通用处理模块设计

崔准

(中国电子科技集团公司第二十研究所,西安 710068)

0 引言

面对日益增长的电子产品小型化和通用化要求,根据通信系统中通用的实际需求,基于高速芯片的应用水平,对通用处理模块要求硬件越简单越好,因此采用高性能的单片 SOC设计通用模块成为了通信系统的必然趋势[1]。

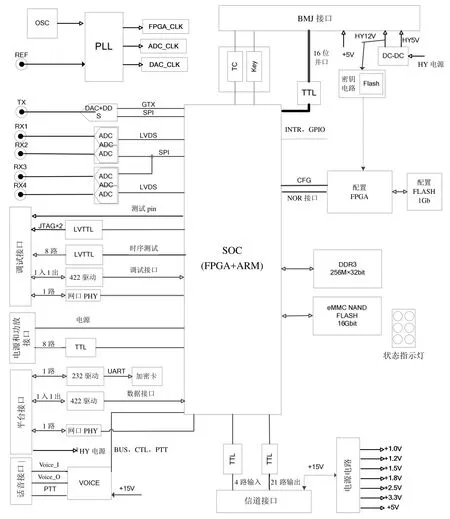

1 整体设计

以高性能SOC(嵌入式双核ARM)、CPLD、DSP、ADC、数字直发 DAC(含 DDS,为接收机提供频综)、RS232 接口、RS422 接口、以太网接口、语音芯片、音频 ADC/DAC、DC/DC 电源、SDRAM、FLSAH 存储器、时钟源、时钟综合器等器件以及外围电路构建射频信号数字直发和接收信号数字处理硬件平台,支持实现数字直发、高速数字采样、数字信号处理、数据处理、接口处理、等功能。

2 主要电路设计

2.1 ADC电路

(1)ADC主要指标

位数:14位;最高采样率:250MHz;模拟输入带宽:1000MHz;

最大输入功率:+10dBm;SNR:不小于60dB;ENOB:9.5位;通道隔离度:不小于95dB。

图1 通用处理模块的组成框图

(2)多片同步

用同一组时钟给2片ADC提供时钟,时钟之间保持严格同相,由SOC为2片ADC提供一个同步输入信号,把 ADC内的时钟分频器复位到初始状态,通过这两种方式保证多片ADC之间的同步。通过精心的PCB布线,保证4路输入中频信号之间的路径延时尽量一致。

采用上述同步和布线措施后,可确保4通道间时序不一致性小于800ps。

(3)中频输入电路

ADC中频输入电路,由于中频信号位于第二奈奎斯特区以上,频率较高,为了获得较高的性能指标,需要用2个巴伦补偿差分信号的幅相不一致[2]。

2.2 DAC电路设计

射频发射信号的产生由 ADI公司的器件AD9164[3]直接产生载波调制信号,由设计框图可以看出,其输出后,经单刀双掷开关、单刀单掷开关、带通滤波后输出。带通滤波器主要为改善发射输出时载波调制信号带外杂波抑制≥-70dBc指标。

在 FPGA内部输出的 I、Q信号数据率为40MSPs,先做 6倍插值,升采样到 240MSPs,送入DAC。将240MSPs的I、Q信号在DAC 内部做24倍插值,输出采样率5760MSPs,设置NCO的输出频率,实现数字正交上变频将信号调制到发射频点。

2.3 SOC

2.3.1SOC构成

SOC选用 Xilinx公司 ZYNQ 7系列的XC7Z100-2FFG900I,片内集成2个Cortex A9 ARM内核的处理器资源PS(Processing System)和FPGA可编程逻辑PL(Programmable Logic)。芯片采用高性能低功耗的28nm工艺制程[4]。PS和PL在不同的电源域上,有需要时,用户可以单独给PL部分断电,以节约功耗。

PS主要由以下4部分构成:

(1)应用处理器单元(APU);

(2)存储器接口;

(3)I/O外设;

(4)互联部分。

2.3.2片内资源

SOC片内资源见表1。

表1 SOC性能、功能汇总表

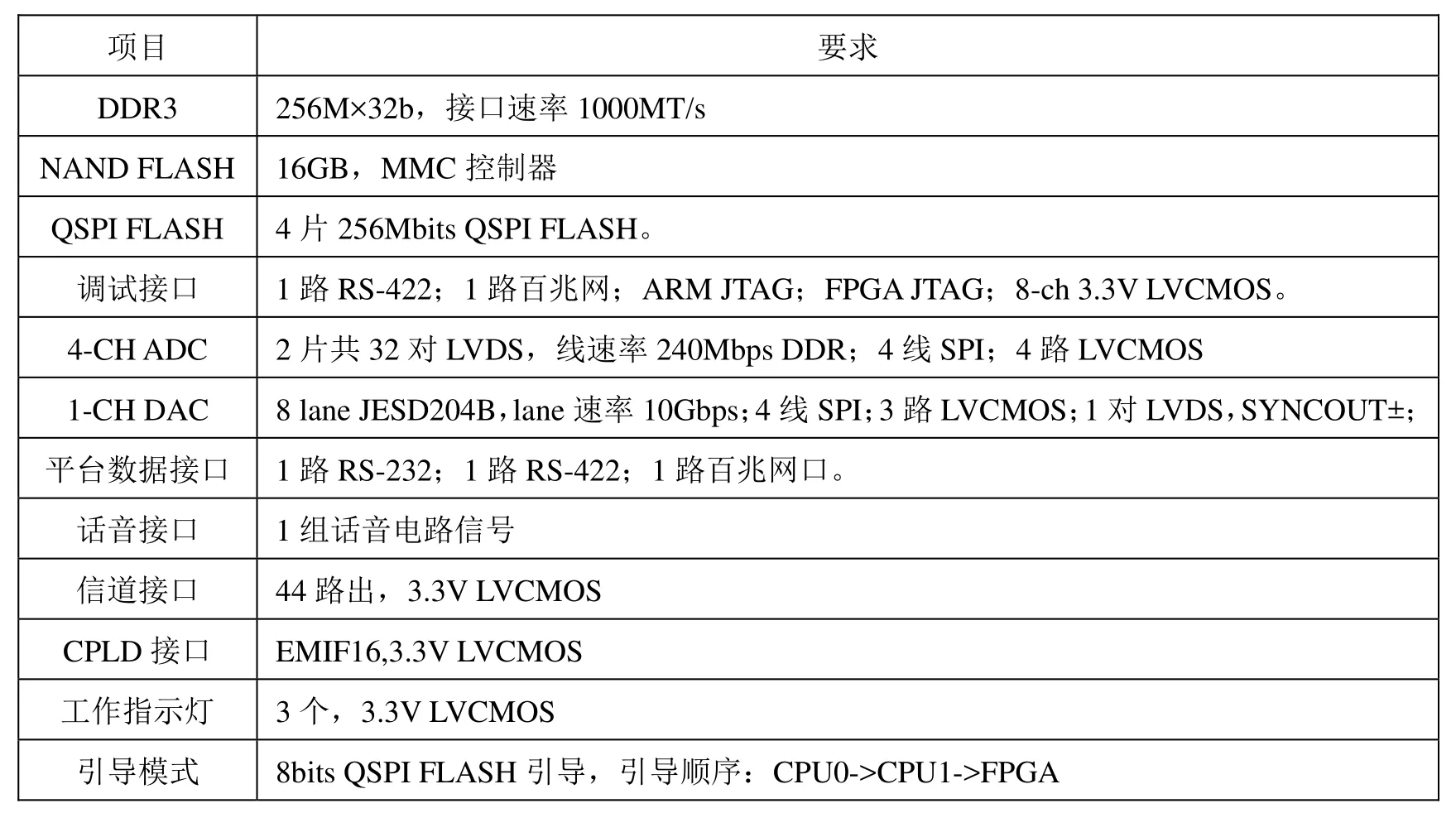

2.3.3外围接口

SOC外围接口汇总表见表2。

表2 SOC外围接口汇总表

2.4 时钟综合器

板外提供10MHz参考时钟,板载1片ADF4355时钟综合器,产生DAC和SOC PL JESD204B所需的6GHz时钟CLK和同步SYSREF信号。板载1片AD9522-1时钟综合器,产生ADC、SOC PL和百兆网Phy芯片所需的各种时钟信号。

2.5 板级管理

采用一片CPLD进行板级管理,监测电源状态,DAC、SOC和电源芯片等功耗较大器件的工作结温,和电源电压、电流。

当发生过温、过压、过流等情况时,板级管理电路将板载全部电路置于复位状态,点亮相应的告警指示灯,发出相应的告警信号。

3 主要软件设计

主要软件包含三部分软件:SOC PS ARM0软件,SOC PS ARM1软件,SOC PL软件。

3.1 SOC PS ARM0 BSP软件功能

SOC PS ARM0用作信息处理器,工作频率800MHz,运行VxWorks操作系统,操作系统版本待定。

为了支持办卡用户的二次开发,在BSP软件层,需要实现如下功能:

(1)支持VxWorks操作系统;

(2)CPU配置、启动;

(3)内存分配;

(4)以太网驱动;

(5)RS-232、RS-422串口驱动;

(6)DDR3 SDRAM驱动;

(7)QSPI FLASH驱动;

(8)eMMC NAND FLASH驱动;

(9)话音驱动;

(10)SOC PL驱动;

(11)引导SOC PS ARM1代码;

(12)配置SOC PL代码。

3.2 SOC PS ARM1软件功能

SOC PS ARM1用作信号处理器,工作频率800MHz,无操作系统,运行裸机程序。通过512kB L2 Cache同信息处理器进行数据交换。信号处理器通过存储器接口和可编程逻辑到存储器的接口对SOC PL内建存储器进行访问,访问速率为32bits@100MHz。由于是裸机运行,没有操作系统管理开销,可以保证最大的实时响应能力,经评估,处理器对外部中断的响应时间小于1μs。

实现以下功能

(1)上电初始化;

(2)与信息处理器交换数据的驱动;

(3)SOC PL内建存储器接口驱动;

(4)中断响应驱动;

3.3 SOC PL功能

SOC PL即 SOC可编程逻辑,即 SOC中的FPGA部分。用于实现数字下变频、数字相关、MSK调制解调、成形滤波等功能。

在驱动代码层,需要实现如下功能:

(1)以太网驱动;

(2)RS-232、RS-422串口驱动;

(3)eMMC NAND FLASH驱动;

(4)话音电路底层接口;

(5)SOC PS驱动。

4 模块测试方案

4.1 单元测试环境设计

通用处理模块单元测试环境见图 2。用信号源作为ADC的输入信号源,用频谱仪测量DAC输出频谱指标,用示波器监视 DAC输出时域波形和输出给信道的控制信号。用直流稳压电源提供15V直流电。用专用的模拟BMJ板测试BMJ接口。使用2台计算机,其中一台接数据接口的RS-232和百兆以太网口;另一台计算机接调试接口的百兆以太网口、FPGA JTAG接口和ARM JTAG接口。

数据接口的RS-422和调试接口的RS-422进行自环测试。调试接口的8路TTL信号和功放接口的4入、4出TTL信号对接测试。功放接口的1路TTL输出信号用于模拟产生DKey信号,测试DKey功能。话音电路接耳机和麦克进行功能测试。

单元测试项目包括:

(1)外部数据接口(百兆以太网)测试;

(2)RS-422接口测试;

(3)调试、测试接口(RS-422、百兆网口、ARM JTAG、FPGA JTAG、FPGA时序测试信号)测试;

(4)话音接口测试;

(5)射频接口测试;

(6)ADC指标测试;

(7)DAC指标测试;

(8)信息处理器功能、性能测试;

(9)信号处理器功能、性能测试;

(10)功耗测试。

图2 通用处理模块单元测试环境

4.2 综合测试软件

软件模块包括:

(1)与显控计算机通信模块(在DP内实现);

(2)与FPGA接口模块(DP和FPGA均有相关模块);

(3)MSK扩频调制模块(在FPGA内实现);

(4)MSK解扩解调模块在FPGA内实现);

(5)信道控制模块(在DP和FPGA内均有相关模块);

(6)显控计算机显控软件;

(7)显控计算机通信软件;

(8)显控计算机误码率、漏组率统计软件。

4.3 测试工作流程

综合测试软件工作流程见图3。

图3 软件工作流程

4.4 测试结论

通过对通用处理模块的功能性能测试设计,完成了模块的外部数据接口(百兆以太网)测试;RS-422接口测试,调试、测试接口(RS-422、百兆网口、ARM JTAG、FPGA JTAG、FPGA时序测试信号)测试,话音接口测试,射频接口测试,ADC指标测试,DAC指标测试,信息处理器功能、性能测试,信号处理器功能、性能测试,功耗测试以硬件稳定性的测试。通过对硬件和软件的充分测试,该模块的硬件和软件能够满足通用处理模块的使用要求。

5 结论

经过对基于 SOC芯片的功能电路设计和相应的软件设计,实现了在一片芯片上的信号处理。信息处理和链路处理,使原来需要3块CPU协同处理完成的工作得以在1块芯片上实现,降低了模块的功耗、减小了模块的体积、提升了整模块的可靠。基于 SOC芯片的通用模块设计实现了数模转换功能、模数转换功能、信号处理功能、信息处理功能、链路处理功能、话音的收发功能。通过环境测试和综合测试验证了模块的通用性、实用性以及可延展性满足使用要求。为后续的设备小型化通用化研制提供了良好的硬件和软件支撑。