FPGA中关于复位的设计和研究

陈云 陈恩耀 刘国斌 左丽丽 刘伟

(上海航天电子技术研究所,上海 201109)

1 引言

复位是FPGA设计中一个基本而又重要的环节。复位的目的是在系统启动或内部模块功能发生错误时将设计强制定位在一个初始可知状态, 合理选择复位方式是电路设计的关键。现在常用的复位方式有三种:同步复位、异步复位和异步复位和同步释放。本文从多角度对三种复位方式的优劣进行了总结, 针对复位设计中存在的问题进行分析并给出了相应的解决方案。

2 三种复位方式的讨论

2.1 同步复位

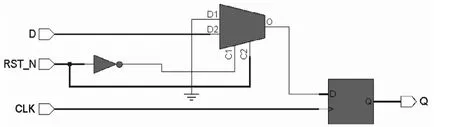

同步复位是指复位信号仅在时钟信号的有效沿对触发器进行复位,此时复位信号可以看作触发器输入端信号的一部分。同步复位综合后RTL图如图1所示。

同步复位的优点:综合出较小的触发器,能够保证整个电路设计的同步性,确保复位仅在时钟信号有效沿发生,有利于滤除高频信号的干扰,有利于进行时序分析及系统的总体同步化,易于进行基于周期的仿真。同步复位的缺点:复位信号的有效时间必须大于时钟周期,否则无法被识别并进行复位操作,需要一个脉冲延展器来保证复位信号具有一定的脉冲宽度, 以确保能够在时钟的有效沿被采样到,综合时占用更多的逻辑资源。

2.2 异步复位

异步复位是指无论时钟沿是否到来,只要复位信号有效沿到来就对系统进行复位,复位信号和时钟相互独立。异步复位综合后RTL图如图2所示。

异步复位的优点:有效利用了寄存器CLR端口,节省了系统资源;复位信号的有效时间可以不受时钟周期的限制,确保其可控性,由于受数据通路时序的要求, 不可能通过在数据通路上添加逻辑门或增加连线延迟来处理同步复位,使用异步复位就可以保证不将复位信号加载到数据通路上,且电路可以不依赖于时钟进行复位。异步复位的缺点:复位信号如果发生在靠近时钟沿很近的时间点,那么触发器就可能没有足够的时间维持输入端信号的值,容易造成亚稳态,从而影响设计的可靠性;复位信号容易受到毛刺的影响,会导致触发器的误操作,进而影响设计的稳定性;此外异步复位的可测性和STA的复杂性要高于同步复位。

图1 同步复位电路图

图2 异步复位电路图

2.3 异步复位同步释放

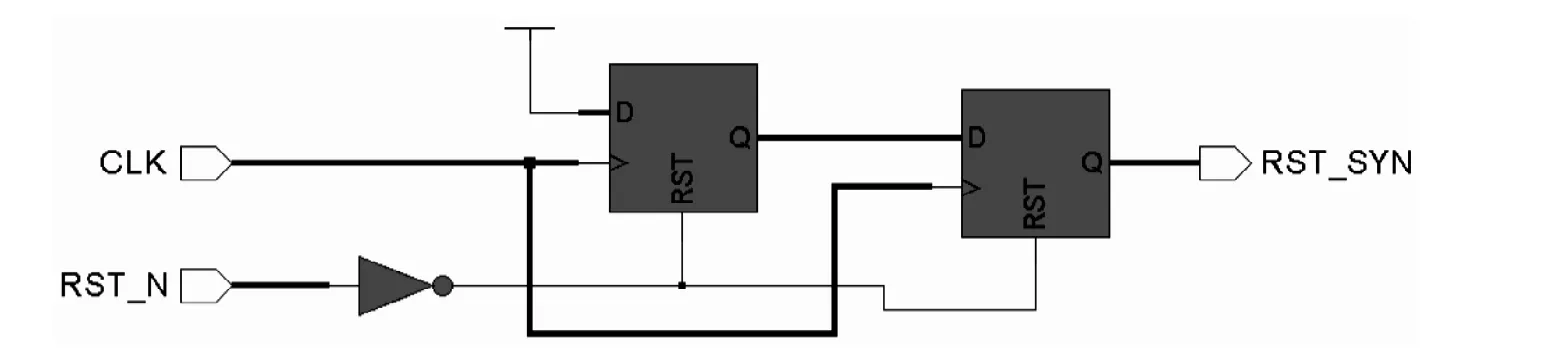

异步复位同步释放是指在异步复位信号到来的时候不受时钟信号的同步,而是在复位信号释放的时候受到时钟信号的同步。其综合后RTL图如图3所示。

其中异步复位信号使用FPGA寄存器的全局异步复位端口能够使复位信号有效时刻到达所有寄存器的时钟偏移最小,既能够节约资源又能简化设计。由于异步复位信号释放时可能导致亚稳态的发生,为了解决这一问题可以采用同步释放,即先将异步复位信号用电平同步器同步后分配给其他功能模块,使得这些功能模块内寄存器在复位释放时总是满足复位恢复时间的约束,从而抑制了亚稳态的发生。异步复位同步释放的双缓冲电路的复位方式同时弥补了同步复位和异步复位的缺陷,并很好地发挥了他们的优势之处。异步复位同步释放的双缓冲复位方式采用两级触发电路,第二级触发器将第一级触发信号利用时钟打一拍,异步信号同步化,有效的降低亚稳态发生概率,同时节约了系统资源,在FPGA逻辑设计中可以很好的提高复位的可靠性。

图3 异步复位同步释放电路图

图4 恢复时间和释放时间图

图5 例1综合后RTL图

3 复位设计中存在的问题

3.1 亚稳态问题

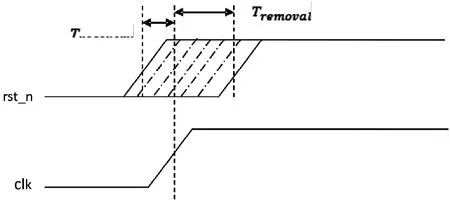

复位设计中复位信号必须保持一定的脉冲宽度以确保时钟的有效沿采样区落在此有效脉冲宽度内,如果时钟采样时刻是复位信号的跳变沿即不稳定态X态,那么复位信号将被X态掩盖。要详细说明亚稳态的产生机制,此处涉及两个概念:恢复时间Tremoval和释放时间Tremoval,恢复时间是指复位信号释放时刻与随之而来最近的时钟有效沿之间的最小时间,而释放时间是指时钟有效沿与复位信号无效时刻之间的最小时间,如图4所示。

如果低有效复位信号的上升沿落在这两个时间窗口内,则触发器的输出端的值将为不定态,既可能处于低电平也可能处于高电平,甚至处于震荡态并在不确定时刻才稳定为高电平或低电平状态。在亚稳态时如果输出值在下一个寄存器捕获之前已经稳定到有效状态,那么这个有效状态也可能发生逻辑误判,如果此逻辑错误发生在决定器件某个功能的关键性寄存器上,将导致此芯片的相关功能也出错,此外如果亚稳态信号被捕获时为震荡态并传递到不同的寄存器,那么这些本该得到相同正确逻辑值的寄存器会得到不同的值,这些不同寄存器有的获得正确值而另一些则获得错误值,将导致逻辑混乱进而使整个功能发生错误。

虽然了解了亚稳态发生的机制,但亚稳态发生是时间问题,往往是不可避免的,目前没有一种方式可以从根本上消灭异步电路中亚稳态的发生,只能通过优化设计使得评估出现亚稳态的平均无故障时间MTBF(Mean Time Between Failures)变大以抑制亚稳态发生,在现行FPGA设计中往往通过将异步复位信号进行两级同步后再使用,可以显著抑制亚稳态的发生,提升系统的可靠性。

3.2 局部复位的设计

FPGA设计中尽量使用专用全局复位或置位资源,其主要作用是对系统中存在的所有触发器、锁存器、查找表单元的输出寄存器进行复位,不会占有额外的布线资源。使用GSR资源,异步复位到达所有寄存器的偏斜最小。

如果设计需求里必须采用某个使能信号进行局部复位,尽量不使用组合逻辑后的信号进行局部复位,组合逻辑出去的电平信号经常伴随着毛刺,将此信号直接用作复位将导致触发器的误判操作,如果非要使用,先此使能信号在需要进行复位的时钟域内进行多级滤波滤除毛刺后使用,这样能大大提升设计的稳定性和可靠性。

图6 例2综合后RTL图

3.3 同一复位路径上复位的设计

在设计时如果对复位问题不够重视,经常会出现在某些功能模块使用同步复位后又在其他模块内使用异步复位的情况,使得同一复位路径上如果既使用同步复位又使用异步复位,首先会导致复位时这条路径上相关寄存器的值跳变的时间不一致,如果这些寄存器输出后续需要做组合逻辑则易产生毛刺进而影响功能的实现,其次这种设计还有可能导致在逻辑综合和布局布线时发生问题,所以尽量避免此种情况的发生。下面为两个常见的错误设计,其设计代码和综合后RTL图如图5、图6。

例1:always@(posedge CLK)begin

if(!RST_N)

Q1 <= 1'b0;

else

Q1 <= DATA;

end

always@(posedge CLK or negedge RST_N)begin

if(!RST_N)

Q2 <= 1'b0;

else

Q2 <= DATA;

end

例2: assign TMP = RST_N_1^RST_N_2;

always@(posedge CLK)begin

if(!TMP)

Q1 <= 1'b0;

else

Q1 <= DATA;

end

always@(posedge CLK or negedge TMP)begin

if(!TMP)

Q2 <= 1'b0;

else

Q2 <= DATA;

end

在复位设计中需要养成一个良好的习惯,最好单独写一个模块作为复位产生模块, 针对输入的异步复位信号,在此模块内通过异步复位同步释放的方式产生复位,然后将此复位信号作为系统复位接到接到所有其他需要复位的功能模块中,这样就会避免发生上述问题。

4 结语

在FPGA设计中不论是采用同步复位还是异步复位, 复位信号必须尽量与时钟信号同步, 否则设计可能被复位到一个无效状态。本文对FPGA 设计中常用的复位设计方法进行了分类、分析和比较,并针对实际复位设计中可能存在的问题,提出了如何提高复位可靠性的方法。随着FPGA设计规模越来越大、功能越来越多,其复杂程度也不断提高,对复位设计可靠性的依赖也越来越紧密,一个好的复位设计方案可以有效减少或消除由复位不当所带来的系统可靠性的问题。

[1]田志明,杨军,罗岚.异步复位设计中亚稳态问题及其解决方案[J].电子器件,2002,25(4):435-439.

[2]夏宇闻.Verilog数字系统设计教程(第2版)[M].北京航空航天大学出版社,2008,6.

[3]李忠琪,胡剑浩,王剑.FPGA中复位电路的设计研究[C].中国通信集成电路技术与应用讨论会论文集,2008.