基于MOS电流模逻辑的4/5双模前置分频器设计

朱艳霞,梁 蓓,杨发顺

(1.贵州大学 大数据与信息工程学院,贵州 贵阳 550025;2.贵州大学 科技学院,贵州 贵阳 550025)

近年来,随着全球无线通信技术的发展,无线通信频段达到了几GHz[1]。体积小、功耗低、性能优已成为航空电子通信设备的发展方向和要求[2]。在锁相环频率综合器中,分频器位于反馈回路上,其工作速度决定了锁相环输出时钟信号的最高频率[3],其功耗是整个锁相环功耗的来源之一。为了满足高频通信的要求,提高双模前置分频器的速度以及降低功耗成为首要问题。因此,研究和设计一个高速、低功耗、低相位噪声的双模前置分频器,对锁相环频率综合器及其功能的实现有着重要的意义和价值[4-5]。

双模前置分频器以D触发器为基本单元。近年来,为了D触发器的性能,出现过许多不同类型结构的D触发器,每种结构都有各自的优缺点。本文采用MOS电流模逻辑(MOS Current Mode Logic,MCML)电路,MCML电路是以独特的差分输入,差分输出,以及采用恒流源偏置的方式。相对CMOS电路来说,该电路更加适合在低电源电压下工作,能输出较小的电压摆幅,也就减小了相邻电路之间的干扰和电路的动态功耗。减小电源电压,MCML电路的延时却不增加;增加工作频率,功耗保持不变;另外,MCML电路的差分对称结构也使它对环境噪声(串扰噪声、电源/接地噪声)具有极强的抗干扰性[6-7];而MCML电路采用恒流源的偏置方式,它始终消耗着静态功耗[8],因此,MCML电路更加适合工作的高频状态。用MCML电路的这一特点设计4/5双置前模分频器,使频率综合器的高速、低功耗性能得到提高。

1 MCML基本工作原理

MCML基本结构如图1所示,其逻辑电路结构主要由3部分组成:下拉网络开关、上拉电阻、恒流源。下拉网络相当于开关的作用,又可以称为逻辑运算模块,当有信号输入时,差分结构的两条支路处于打开或关断状态,决定着下拉网络开关电流Iss的走向,从而使恒流源电流Iss只流向其中一条支路,进而实现电路的逻辑功能。然后经过上拉电阻,实现电平的输出,输出摆幅为ΔV。电路的功耗与电压摆幅与尾电流Iss有关,因此减小电压摆幅与尾电流是减小功耗的基本途径。

P耗=Iss×ΔV

(1)

其中,P耗为电路的输出功耗,Iss为尾电流源,ΔV为电压输出摆幅。

当NMOS管工作在饱和区时,它能输出较高的阻抗,因此采用工作在饱和区的NMOS管来代替恒流源,输出恒定电流Iss。在高频段时,能提高电路的逻辑运算精度。而在实际应用中,考虑到使用电阻会消耗大的面积,N阱电阻与扩散电阻对衬底的PN结寄生电容较大,多晶硅电阻因工艺偏差而精度不够[9],因此使用工作在线性区的PMOS管代替上拉电阻RD。此外,为了设计方便,常将PMOS管的栅极直接接地。

对于MCML结构的电路,其工作速度受电压摆幅、负载电阻、尾电流Iss、电容CL(含负载电容和寄生电容)的影响[9],其延迟表达式为

(2)

图1 MCML逻辑电路

由于上述参数之间相互影响、相互作用,为提高工作速度和电压摆幅,需要增大尾电流,但同时也增加了功耗和面积;减小负载电阻可以减小充放电时间常数,但同时减小了电压摆幅。因此在设计电路时需要折中考虑这些参数,使MCML结构的电路性能达到最佳[10]。

2 电路设计

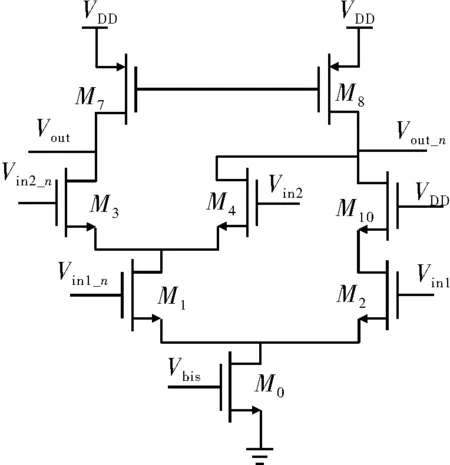

2.1 或门设计

图2为MCML结构的逻辑或门电路[11],其中NMOS管M1、M2、M3、M4、M10构成下拉网络开关,M0作为恒定电流源,负载电阻由PMOS管M7、M8代替。通过对逻辑或门电路参数的优化设计,采用SMIC 0.11 μm CMOS工艺,Cadence仿真软件,得到所设计的MCML逻辑或门的输出波形,如图3。在电源电压为1.2 V,尾电流源Iss为20 μA,输入信号为1 GHz的条件下,其电压摆幅为0.5 V,功耗为24 μW,其上升延时为21.2 ps,下降延时为33.8 ps。

图2 MCML逻辑或、或非门

图3 MCML逻辑或、或非门波形图

由图3可知,电路的同相端Vout实现了或的功能、反向端Vout_n实现了或非功能。将电路中的输入信号Vin1和Vin2与其反相信号Vin1_n和Vin2_n进行调换,可实现与、与非功能。

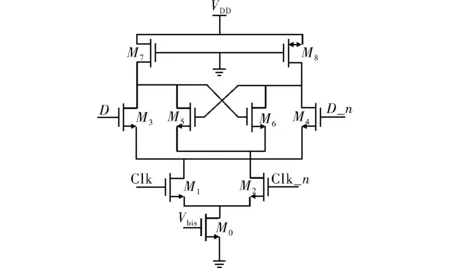

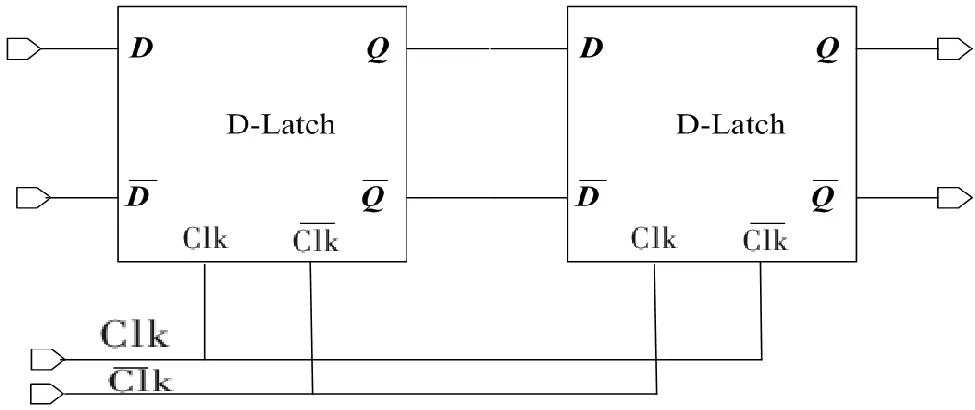

2.2 主从D触发器的设计

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,在特定输入脉冲电平作用下改变输出状态[9]。图4为MCML结构的D-Latch电路原理图。与逻辑或门结构相似,其中,PMOS管M7、M8代替电阻,NMOS管M0充当恒定电流源,M1、M2作为时钟输入级,M3、M4、M5、M6共同组成数据输入与寄存级。两个MCML结构的D-Latch串联,时钟输入相反,构成一个主从式D触发器,电路框图如图5。当CLK输入为高电平时,主锁存器实现跟踪功能,从锁存器实现锁定功能;输入信号Vin跳过主锁存器直接输送到从锁存器,但从锁存器的输出仍然保持上一次的信号。当CLK输入为低电平时,主锁存器的功能转为锁定功能,从锁存器转为跟踪功能,主锁存器锁定上一次的信号,并将这一信号输送给从锁存器,因此从锁存器的输出仍然为上一次的信号。即CLK输入转为低电平时,主从D触发器的输出并不随CLK的输入变化[12]。

图4 MCML结构D-Latch电路原理图

相对于D-Latch来说,主从式结构的D触发器的功耗更低,但延时又相对增加。若D-Latch的延时为τ,则主从式D触发器的延时为2τ。当电源电压为1.2 V,尾电流Iss为20 μA ,输入信号为500 MHz,时钟信号为1 GHz时;图4所设计D-Latch的传播延时τ为69.6 ps,图5所设计的主从式D触发器传播延时为133.7 ps,功耗为61.47 μW。与计算值2τ=139.2 ps相比较,其误差约为4%,与传统的CMOS电路相比,其功耗和延迟都比较小。

图5 MCML主从D触发器结构框图

图6 主从D触发器的波形图

2.3 MCML 4/5双模前置分频器

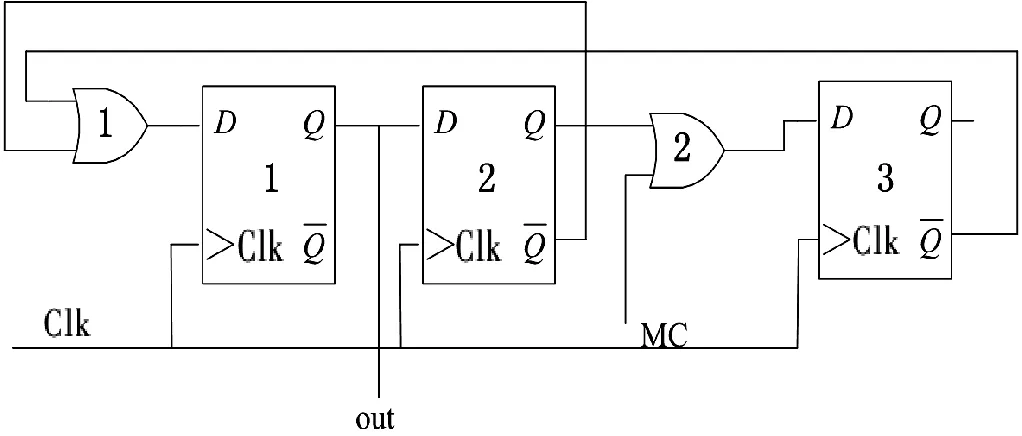

3个MCML结构的主从式D触发器和2个MCML结构的或门,构成4/5双模前置分频器电路[1],如图7。当MC的输入信号为高电平时,触发器2的输出结果对或门2的作用可忽略,或门2的输出结果都为高电平。触发器1和3的串联输出实现4分频;当MC为低电平时,实现5分频。在频率综合器中,可根据MC输入信号的高低电平状态选择想要的分频比。

图7 4/5双模前置分频器

图8 4/5双模前置分频器瞬态响应

或门和主从式D触发器分别采用图2和图5结构的电路。尾电流Iss为50 μA,频率在1~5 GHz的范围内,对图7所设计的4/5双模前置分频器进行瞬态仿真,仿真波形如图8所示。结果表明,电路功能正确,电路的功耗分别为0.543 mW、0.552 mW、0.547 mW;电路的功耗几乎不随频率的变化而变化,且相对于其他电路功耗较小。

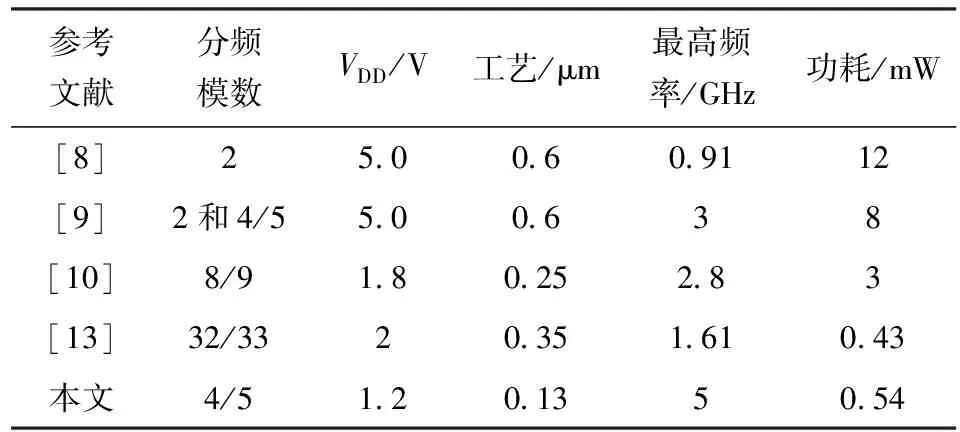

表1为本文所设计的分频器和窦建华[13]、韩波[14]、Pellerano[15]、J. Navarro[16]等人所设计的分频器结果对比。窦建华在电源电压为5 V,采用0.6 μm的工艺,使用源级耦合逻辑(SCL)电路实现了2分频;该分频器的最高工作频率为0.91 GHz,功耗为12 mW。韩波在电源电压为5 V,采用0.6 μm的工艺,使用TSPC(True Single Phase Clock)和E-TSPC(Extended TSPC)技术设计了2分频和4/5的双模前置分频器;该分频器的最高工作频率为3 GHz,功耗为8 mW。Pellerano和J. Navarro用TSPC技术分别实现了8/9和32/33的双模前置分频器;其中8/9双模前置分频器的最高工作频率为2.8 GHz,功耗为3 mW;32/33双模前置分频器的最高工作频率为1.61 GHz,功耗为0.43 mW。因此,采用MCML电路设计4/5的双模前置分频器的最高频率比TSPC和SCL结构电路的自高频率较高,其功耗较低。

表1 分频器的参数对比

4 结束语

提出了基于MCML结构的4/5双模前置分频器的设计方案。由于采用MCML电路的4/5双模前置分频器的功耗与工作频率无关,仅取决于基本模块的功耗。因此,优化单元模块的参数是提高双模前置分频器性能的一个重要途径。改设计用已优化参数的MCML电路设计了主从式D触发器和或门,并对其性能进行了分析讨论。采用MCML结构的主从式D触发器和或门构成一个4/5双模前置分频器,仿真结果表明,MCML结构电路的功耗和速度均优于传统的CMOS电路。

参考文献

[1] 曾健平,谢海情,晏敏,等.新型双模前置32/33分频器设计[J].微电子学与计算机,2007(1):150-152.

[2] 周炳利,许波强,王从道.一种高速跳频频率合成器的实现[J].电子科技,2013,26(8):88-89.

[3] 庞遵林,郭锐.一种用于高速锁相环的整数分频器设计[J].电子科技,2015,28(6):104-107.

[4] 陈作添,吴烜,唐守龙,等.宽带低相位噪声锁相环型频率合成器的CMOS实现[J].半导体学报,2006,8(10):67-69.

[5] 王永禄,杨毓军,周述涛.一种超低功耗5 GHz双模预置分频器[J].微电子学,2006,6(5):38-40.

[6] Hassan H,Anis M,Elmasry M,MOS current mode logic: desugn, optimization, and variability[C].Paru: Proceedings of IEEE International SOC Conference. 2004.

[7] 桑红石,方海涛,余萌,等.环形振荡器对称负载特性分析[J].微电子学与计算机,2011,28(5):197-200.

[8] 蒋征科.低功耗MCML电路和电流型CMOS电路设计研究[D].杭州:浙江大学,2003.

[9] 梁蓓,马奎,傅兴华.MOS电流模逻辑分频器设计[J]. 微电子学与计算机,2012,29(10):157-160.

[10] Hassan H,Anis M, Elmasry M.MOS current modelogic:design, optimization,and variability[C].CA,USA:IEEE International SOC Conference,2004.

[11] 刘树凯.高速CMOS MCML单元设计及温度计译码电路实现[D].西安:西安电子科技大学,2012.

[12] 盛旺.高性能32/33分频双模前置分频器设计[D].长沙:湖南大学,2008.

[13] 窦建华.0.6 μm CMOS 静态分频器电路设计[J].电气电子教学学报,2004,26(1):35- 37.

[14] 韩波,唐广.2.4 GHz动态CMOS分频器的设计[J]. 国外电子元器件,2006(1):15-17.

[15] Pellerano S.A 13.5 mW 5 GHz frequency synthesizer with dynamic-logic frequency divider[J].IEEE Journal of Solid-State Circuits,2004,39(2):378-383.

[16] Navarro J,Martins G C.Design of high speed digital circuits with E-TSPC cell library[C].Brazil:In Proceedings of the 24thSymposium on Integrated Circuits and Systems Design,2011.