高性能多标准可配置Viterbi译码器设计与验证

戴澜 马东俊

摘 要: 为了使Viterbi译码器广泛地应用于更多标准中,结合前向回溯译码和滑窗流水技术,同时ACS(Add?Compare?Select)部件通过减规约的操作减少异或延迟,提出一种高性能可配置Viterbi译码器。该译码器支持[12,13,14]码率,约束长度在5~9之间,生成多项式任意配置等参数,同时支持GPRS,WiMAX,IS?95 CDMA,LTE,CDMA 2000等多标准。在对译码器进行设计的基础上,基于UVM 验证方法学搭建一种模块级验证平台,完成Viterbi译码器模块级的功能验证,覆盖率达到99.4%。利用Synopsys Design Compiler工具进行综合,面积为0.2 mm2;在28 nm工艺,500 MHz主频下,功耗为38.3 mW,吞吐率为1.06 Gbit/s。结果表明,此译码器具有很好的灵活可配性,在移动终端有很好的应用前景。

关键词: Viterbi译码器; 滑窗流水技术; 多项式任意配置; UVM 验证方法学 ; 异或延迟; 移动终端

中图分类号: TN919.3?34 文献标识码: A 文章编号: 1004?373X(2018)10?0010?05

Abstract: To make the Viterbi decoder widely applied in more standards, a high?performance configurable Viterbi decoder is proposed by combining with pre?traceback (PTB) decoding and sliding?window pipeline technology, and reducing the XOR delay by means of the specification subtraction operation in Add?Compare?Select (ACS) components. The decoder can support the code rates of 1/2, 1/3 and 1/4, constraint length of 5 to 9, polynomial generation arbitrary configuration and other parameters, and meanwhile can support multiple standards such as GPRS, WiMAX, IS?95 CDMA, LTE, and CDMA2000. On the basis of the decoder design, a module?level verification platform is established based on the UVM verification methodology to accomplish module?level functional verification for the Viterbi decoder with the code coverage rate as high as 99.4%. The Synopsys Design Compiler tool is used to perform integration, and the area is 0.2 mm2. In the 28 nm process with the main frequency of 500 MHz, the power consumption is 38.3 mW and the throughput rate is 1.06 Gbit/s. The results show that the decoder has good flexibility and compatibility, and has a good prospect in mobile terminal application.

Keywords: Viterbi decoder; sliding?window pipeline technology; polynomial arbitrary configuration; UVM verification methodology; XOR delay; mobile terminal

维特比译码器在现代通信、信息储存中都有广泛的应用。为了配合多样化的通信标准,设计一个能够适应多种标准的、高性能的维特比译码器,具有十分重要的意义。

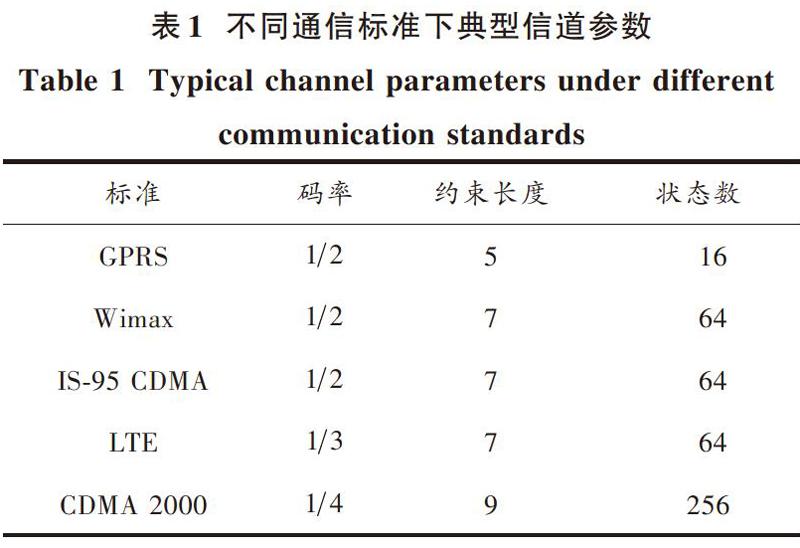

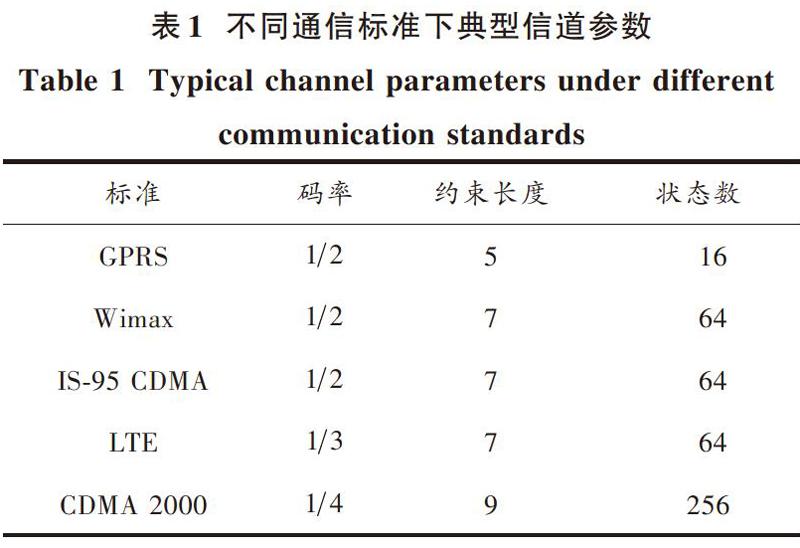

一般Viterbi译码器大多是支持单一标准的[1?3],本文中基于前向回溯和流水技术[4?5],采用基四算法,提出一种支持多标准、可配置的译码器。表1列出了不同通信标准下,多标准Viterbi译码器需要支持的码率、约束长度、状态数参数。从表中可以看到大部分通信标准的码率都在[12,13,14]间变化,约束长度在5~9间变化。

如何高效地验证Viterbi译码器是目前亟待解决的问题。文献[6]采用VMM(Verification Methodology Manual)验证方法学搭建MAC(Media Access Control)模块的验证平台,缺点是VMM最初不开源,使用不方便;文献[7]采用OVM(Open Verification Methodology)验证方法学设计了一个关于SoC(System on Chip)系统的验证平台。OVM虽然是开源的,但是没有引进寄存器解决方案,这是很大一个短板。而UVM(Universal Verification Methodology)验证方法学继承了OVM和VMM的优点,同时又结合System Verilog(SV)验证语言的随机约束特性,针对可配置译码器可以产生大量随机激励,所以本文中采用UVM验证方法学,结合SV验证语言,搭建层次化验证平台,解决了手动遍历所有配置信息的问题,实现了验证的高效性。

1 Viterbi译码器优化算法

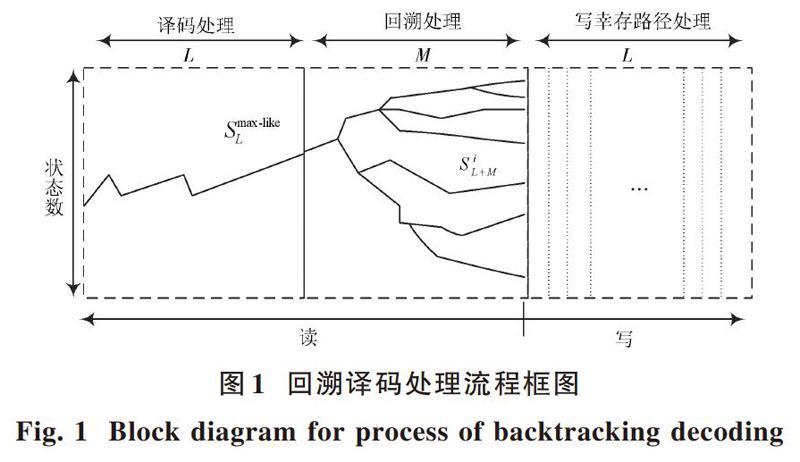

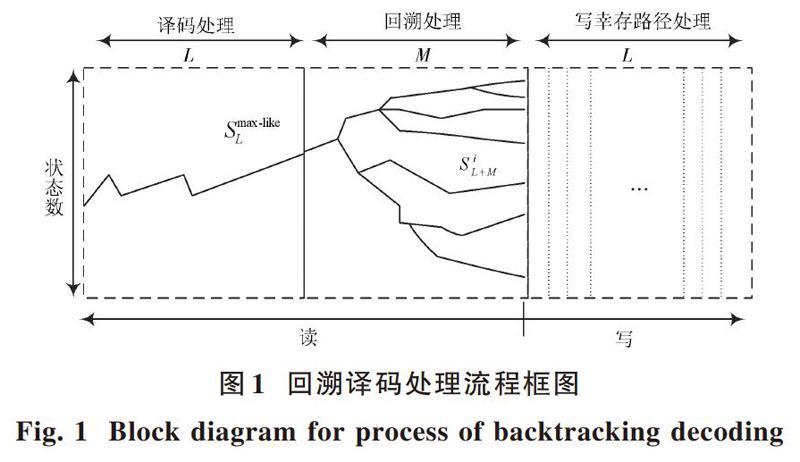

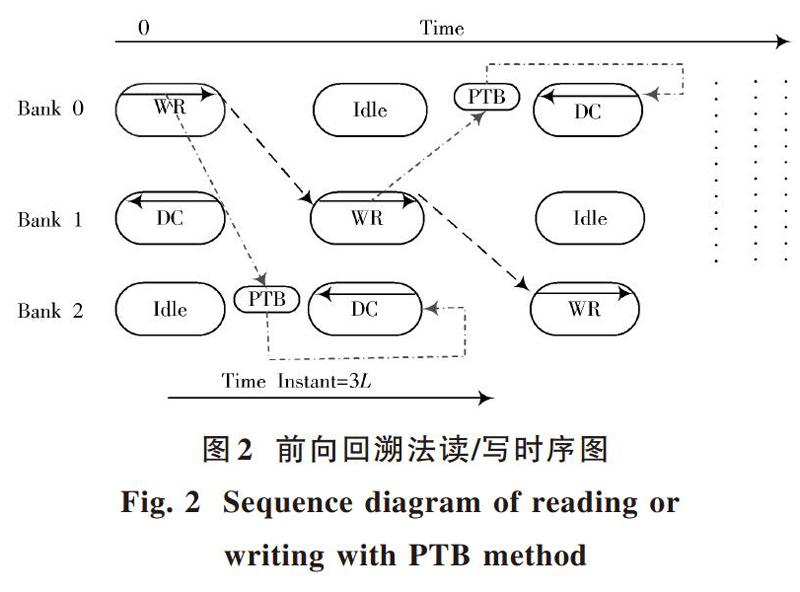

传统的回溯方法在文献[4?5]中进行了详细的介绍。为了减小传统回溯方法中的译码延迟,本方案中采用基于数据一致性原则的前向回溯译码方法(Pre?traceback,PTB),同时引入指针寄存器,在基四结构下,通过64状态交换单元组成的交换网络来得到DC(Decoding,DC)操作的起始状态。如图1所示,所有状态经过M步回溯处理以后,将汇聚到同一个状态。在起始回溯时,选择任意起始状态,通过一定级数回溯后,路径会收敛于最大似然状态。

采用 PTB 处理后从幸存路径写入到译码比特出来延时大小为 3L,减小了后向回溯处理中存储器读/写次数。Idle表示空闲状态,不做任何操作。 前向回溯法读/写次数时序图如图2所示。

2 Viterbi译码器实现方案

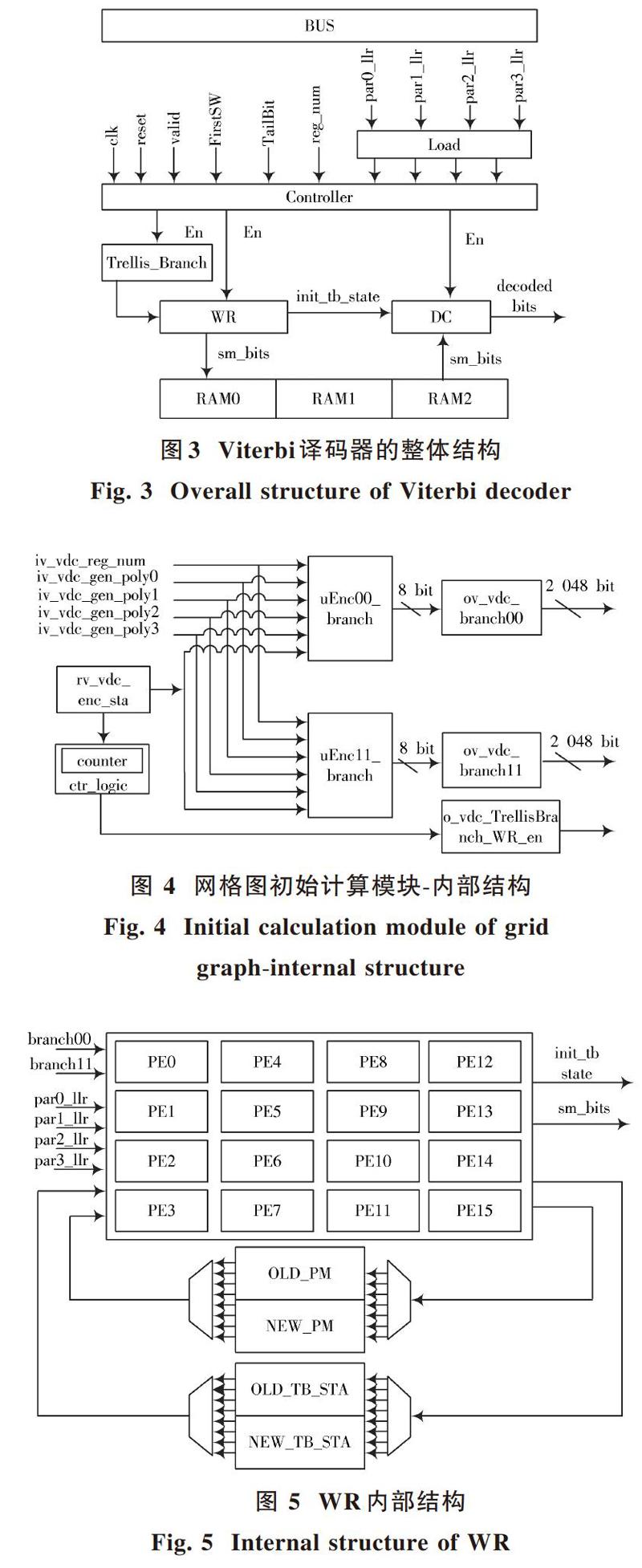

文中Viterbi译码器主要根据LTE卷积编码(3,1,7)设计的,其是一个支持多标准、高性能、可配置的Viterbi译码器。Viterbi译码器的整体结构图如图3所示。

Trellis_initial是网格初始化单元,根据码率、生成多项式、约束长度初始化trellis图的分支路径,对于基四算法来说,需要生成4路输出,分别是“00”,“01”,“10”,“11”分支产生的校验比特。这4条分支产生的校验比特用于分支度量的计算。经过简化,本方案中只需要产生2路分支,即“00”分支和“11”分支,得到的发送序列用于计算分支度量,从而完成译码器的可配置。网格图内部计算结构如图4所示。

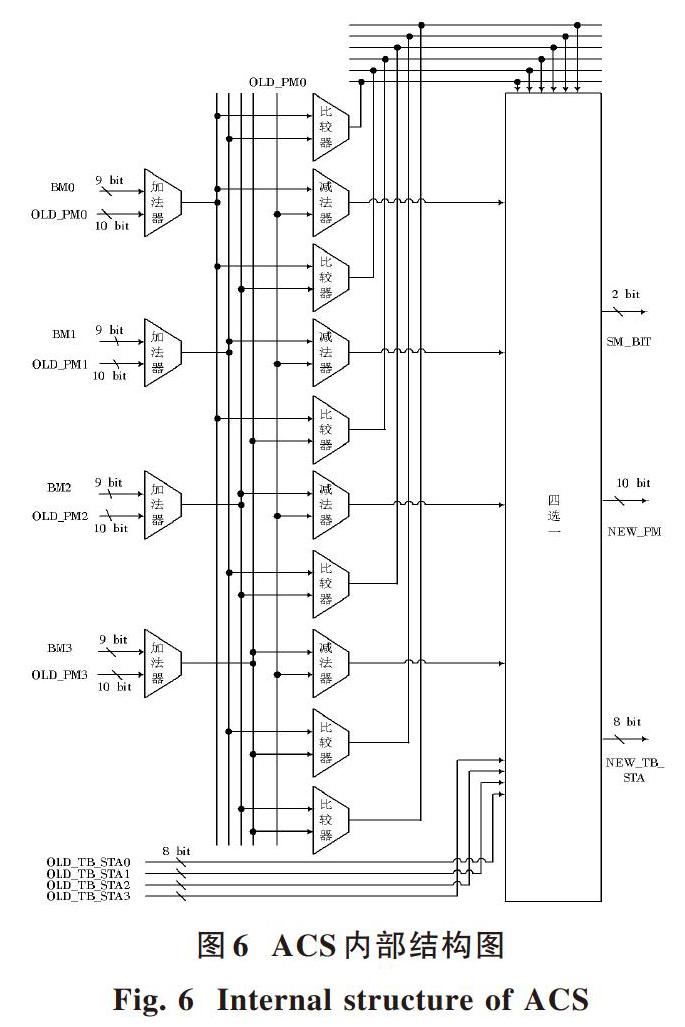

WR(Write)是前向狀态递归计算单元,本设计中一共有64个ACS单元,每4个组成一个蝶形处理单元,共有16个蝶形处理PE(Processing Element)单元。WR内部计算结构如图5所示。

ACS单元内部结构图如图6所示,单元内部增加少量减法器来减小译码延迟,同时采用减规约操作,每次减去前一时刻的某一个状态度量值,比模规约算法少了两级异或延迟。

DC是译码单元,回溯译码单元从RAM中读取的数据是128位宽,译码时首先要从128 bit中选出对应回溯状态的2个幸存比特,然后利用幸存比特更新回溯状态,同时取回溯状态的高两位作为译码输出。

综上所述,本文中通过对配置参数的灵活性支持,采用前向回溯译码和流水操作,得到了可配置的Viterbi译码器。

3 Viterbi译码器验证

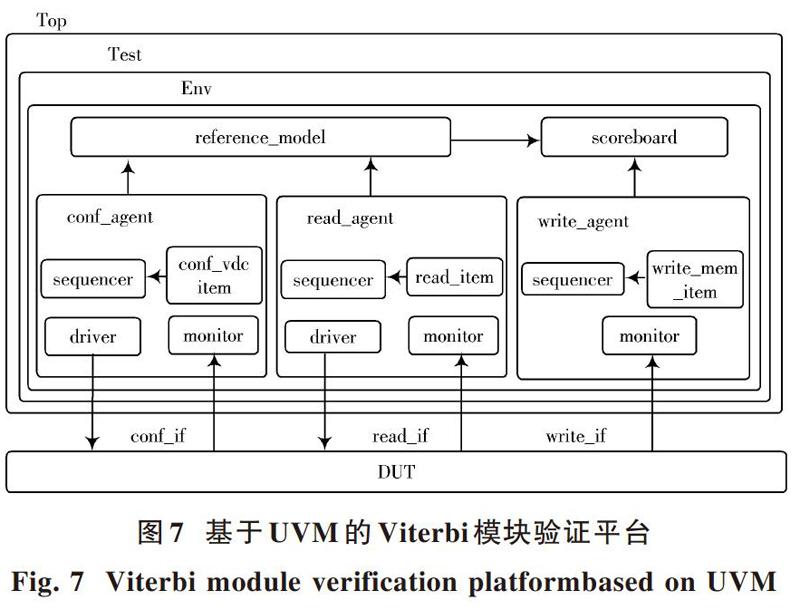

本文基于UVM验证方法学结合SV语言,设计了Viterbi译码器验证平台,如图7所示。

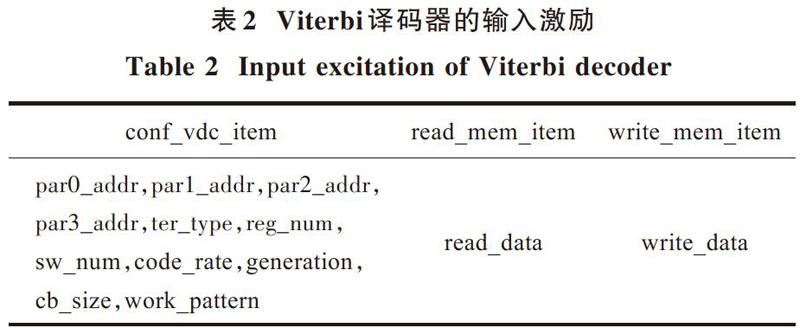

在该平台中例化了三个agent,分别是conf_agent,read_agent和write_agent,定义了三个interface,分别是conf_if(配置接口)、read_if(读数据接口)、write_if(写数据接口),来实现信息配置,数据读取和写入。本文中采用的reference model是基于C语言编写的参考模型,通过DPI(Direct Programming Interface)[9]接口将其接入到验证平台中,最终在scoreboard中实现和DUT(Design Under Test)的结果比对。通过比对,判断DUT的功能是否正确。下面对所设计的验证组件进行了简单的讨论。data_item产生DUT的输入激励,这些输入激励可以是输入数据,也可以是一些配置信息,如表2所示,为本方案中所需要的配置和数据激励。

conf_vdc_item生成Viterbi译码需要的配置信息,包括4路检验信息的地址、结尾方式、寄存器个数、滑窗个数、码率、生成多项式的配置、工作模式、码块大小;read_mem_item产生输入激励信息;write_mem_item存储Viterbi译码结果,用于和reference model的译码结果比较。

sequencer负责发送sequence_item(conf_vdc_item,read_mem_item,write_mem_item)到 driver,并接收driver发回来的一个响应。driver是一个主动的主体,负责将 read_mem_item,write_mem_item 里的信息驱动到 DUT 的端口上,monitor是一个被动的主体,负责监测输入激励和译码结果,在write_agent里只例化了monitor。

4 结果与分析

4.1 基四算法下的性能仿真结果

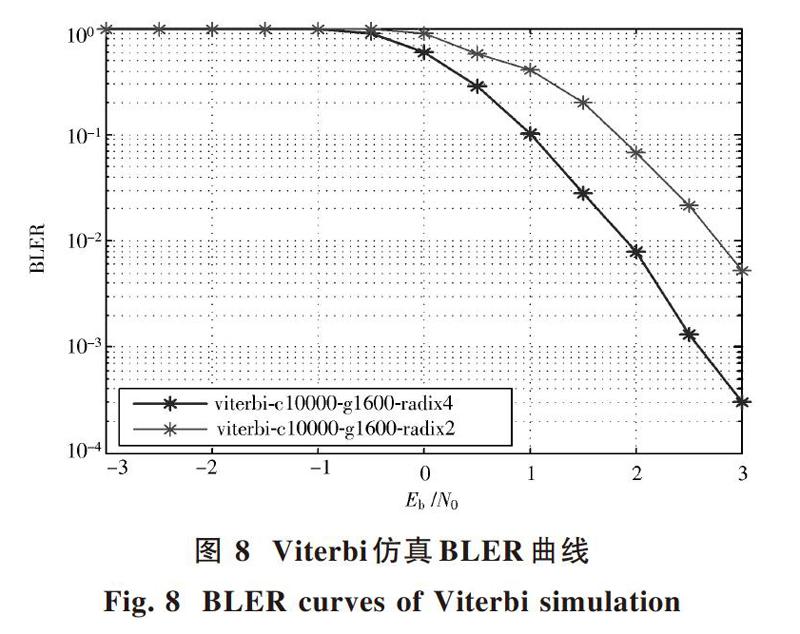

基四算法下的性能仿真结果如图8所示。该仿真中码块长度1 600,码块个数10 000,AWGN信道,采用QPSK调制。从图8中可以看出,基四算法下的前向回溯译码性能优于基二算法,性能提升约1 dB。

4.2 性能对比

表3列出了本设计中基二、基四算法下Viterbi译码器典型参数和性能,以及其他相关工作中的性能对比,主要包括基数、约束长度、码率、频率和吞吐率。由表3可知,本文实现的Viterbi译码器不但性能更高,而且灵活性更强,可以支持约束长度在5~9,码率在[12,13,14]间变化,并支持GPRS,WiMAX,IS?95 CDMA,LTE,CDMA 2000等多种通信标准。

4.3 DC综合结果

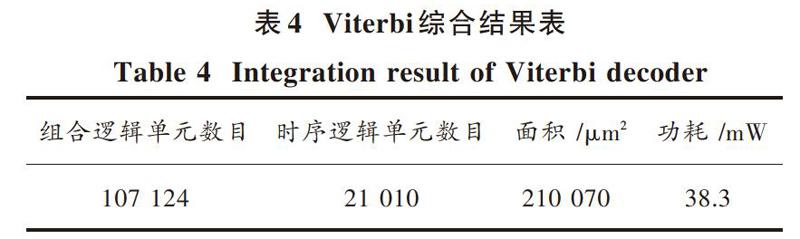

本文设计采用TSMC 28 nm标准单元库,利用Synopsys Design Compiler进行综合,主频设为500 MHz,综合结果如表4所示。

4.4 验证结果

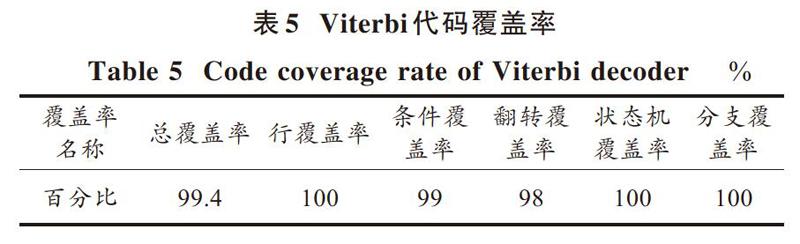

软件仿真是在Linux环境下,利用VCS编译UVM库进行的,设置的码块个数为300个。通过在scoreboard里判断DUT和rererence model的结果,若译码结果一致,打印“compare success!”字样,否则打印“compare failed!”。本文中最终打印结果全部打印的“compare success!”,说明维特比译码器译码正确。表5列出了最终代码覆盖率。

以上结果说明本文中设计的验证平台达到了预期要求,实现了对Viterbi译码器的功能验证。

5 结 语

本文通过配置Viterbi译码器的动态参数实现了支持不同标准的译码器,并通过仿真验证。在500 MHz主频下,峰值吞吐可以达到1.06 Gbit/s。对于支持多标准的译码器来说,明显优于其他设计。利用Synopsys Design Compiler工具进行综合,500 MHz主频下,功耗为38.3 mW,且仿真结果表明,该译码器具有较好的译码性能,值得应用推广。同时在验证领域中,本文采用UVM验证方法学搭建的验证平台成功复用到CRC(Cyclic Redundancy Check)检验的模块中,极大地提高了验证的效率和平台的复用性。

参考文献

[1] BATCHA M F N, SHA′AMERI A Z S. Configurable adaptive Viterbi decoder for GPRS, EDGE and Wimax [C]// Proceedings of IEEE International Conference on Telecommunications and Malaysia International Conference on Communications. Penang: IEEE, 2007: 237?241.

[2] YUAN H H, HSU C Y, KUO T S. Low complexity Radix?4 butterfly design for the Viterbi decoder [C]// Proceedings of IEEE Vehicular Technology Conference. Montreal: IEEE, 2006: 1?5.

[3] ABDALLAH R A, LEEY S J, GOEL M, et al. Low?power pre?decoding based viterbi decoder for tail?biting convolutional codes [C]// Proceedings of IEEE Workshop on Signal Processing Systems. Tampere: IEEE, 2009: 185?190.

[4] MANZOOR R, RAFIQUE A, BAJWA K B. VLSI implementation of an efficient pre?trace back approach for Viterbi algorithm [C]// Proceedings of International Bhurban Conference on Applied Sciences and Technology. Islamabad: IEEE, 2007: 27?30.

[5] 薛莲.MIMO?OFDM系统二相ACS前向回溯基四Viterbi译码器设计与实现[J].科技通报,2013,29(9):176?180.

XUE Lian. Design and implementation of two?phase ACS and pre?traceback Radix?4 Viterbi decoder for MIMO?OFDM system [J]. Bulletin of science and technology, 2013, 29(9): 176?180.

[6] 李炎琨.基于VMM验证方法的研究[D].西安:西安电子科技大学,2010.

LI Yankun. The research of VMM?based verification method [D]. Xian: Xidian University, 2010.

[7] 柏才明.基于OVM的SoC功能验证系统的设计与实现[D].武汉:华中科技大学,2011.

BAI Caiming. Design and implementation of OVM?based SoC function verification system [D]. Wuhan: Huazhong University of Science and Technology, 2011.

[8] 张弓.可配置的Viterbi译码器的FPGA实现[D].西安:西安电子科技大学,2009.

ZHANG Gong. Implementation of a configurable Viterbi decoder with FPGA [D]. Xian: Xidian University, 2009.

[9] Accellera. Universal verification methodology (UVM) 1.2 user′s guide [EB/OL]. [2015?11?06]. https://wenku.baidu.com/view/19eced832f60ddccdb38a05b.html.

[10] 3GPP. TS 36.212?2009 multiplexing and channel coding (V8.7.0) [S]. [2009?06?01]. http://www.zbgb.org/147/StandardDetail

2505982.htm.

[11] Accellera. Universal verification methodology(UVM)1.2 class reference [EB/OL]. [2013?12?16]. http://ishare.iask.sina.com.cn/f/65070280.html.