4K高集成度小间距LED显示屏控制器的设计与实现

祁亚军,王剑锋

(佛山市青松科技股份有限公司,广东 佛山 528200)

随着技术的发展,LED显示屏可以实现的点间距越来越小,目前点间距0.9 mm的LED显示屏已经达到量产的阶段。较小的点间距消除了近距离观看时的颗粒感。这就为LED显示屏进入军队公安指挥中心,能源行业集控中心,广电行业演播中心等需要大屏幕显示设备的场合提供了契机。传统大屏幕设备一般由数字光处理技术(Digital Light Procession,DLP)背投和液晶显示器(Liquid Crystal Display ,LCD)液晶拼接而成。这些传统设备因为物理原因,都无法克服边框拼接间隙问题。一个完整的画面被边框分割,严重影响观看者的视觉感受,分散观看者的注意力。LED显示屏由无边框的模块组成,整个大屏幕浑然一体,保证了画面的完整性。除了无拼接缝,LED显示屏在亮度、对比度、色彩还原、系统功耗、维护成本等方面都优于DLP背投和LCD液晶拼接。因此,目前小间距LED显示屏已成为室内大屏幕设备的首选[1]。

在小间距LED显示屏的大量工程实践中,我们发现原先通用的LED显示屏控制器已不再适用。首先,随着点间距的缩小,相同显示面积下,像素数大幅增加。原先的控制器显示带宽已严重不足,需要多台控制器并联才能完成整个屏幕的控制。这就增加了系统的复杂度,需要解决多台控制器的同步问题,降低了系统可靠性。其次,小间距LED显示屏的应用场合决定了它需要支持多格式的信号源,比如最常见的HDMI,DVI,SDI,VGA等,但是原先的控制器只支持DVI,对于其他格式的信号,需要通过其他设备进行转换。最后,原先的控制器没有友善的人机接口,所有操作需要通过电脑进行,操作复杂[2]。

针对小间距LED显示屏的产品特性及应用特点,有必要开发一款高集成度,多功能,高带载,易使用的控制器。

1 控制器功能需求分析

根据以往项目实施经验及未来技术发展趋势,我们确定新的控制器应具备以下功能。(1)支持逐渐成为主流的4K@30 Hz的信号输入。满足超高清画面显示的要求。(2)支持HDMI,DVI,SDI,VGA,DP等各种常用信号接口。减少对外部转换器的需求。(3)具备视频缩放,隔行转换,画质增强,画中画等视频处理功能。保证显示质量。(4)具备Genlock同步功能。用于保证显示画面的完全同步。(5)具备多媒体文件存储与解码能力。摆脱对电脑等播放设备的依赖,使显示屏可独立运行。(6)带有LCD,按键等人机交互设备。便于方便快捷的操作系统。(7)支持以太网通信。配合软件实现对控制器的远程、集中管理。(8)LED控制输出端口总带宽不低于6 GB,以满足4K的带载需求。

2 控制器总体设计

基于上述需求分析,我们规划控制器由CPU+FPGA+视频处理SOC三大核心部分构成。充分发挥各种处理芯片自身的特长,优势互补,协同工作,共同构成一个强大的小间距LED显示屏控制系统。CPU运行标准Linux操作系统,用来实现多媒体文件解码,人机交互,系统配置与管理等。FPGA具有强大的可编程能力,优异的并行处理架构,通过自主开发固件,用来实现多路输入信号的切换、拼接,画面处理、存储与转发以及LED显示屏的直接控制。视频处理SOC是视频处理ASIC芯片,广泛应用于高端电视,高端显示器,用来实现视频缩放,隔行转换,画质增强,画中画等视频处理功能。

3 控制器关键功能模块的实现

如前所述,控制器共分三大功能模块。其具体实现为以下方面。

(1)视频处理SOC选用ST意法半导体公司的高端显示器芯片STDP9320,该芯片支持4K分辨率的输入输出。支持各种常见视频信号的输入。拥有先进的MADi及DCDi视频缩放,隔行转换,画质增强,画中画等视频处理技术。强大的6基色颜色管理。由于带宽原因,STDP9320需要使用两组LVDS信号才能输出4K分辨率的画面。而FPGA无法直接接收LVDS信号,因此在视频处理SOC和FPGA间增加了两路LVDS转TTL的转换电路。

(2)CPU芯片选用飞思卡尔公司的i.MX6 Quad应用处理器。该CPU拥有4个ARM Cortex-A9处理核心,最高运行速度1 GHz。因此具备强劲的计算能力。芯片内部集成了硬件视频加速器,具有1080P全高清视频解码能力。芯片自身带有丰富的外设资源,支持各种常见外围接口。芯片有TTL LCD显示接口及HDMI显示输出接口。我们利用LCD显示接口把CPU解码出来的画面送给FPGA。利用HDMI接口输出系统操作界面。这样在播放画面的同时可以进行系统操作,保持了两者的独立性。CPU的软件系统基于标准Linux开发,使得整个系统具有开放性,易扩展性。

(3)FPGA是整个系统的核心。视频处理SOC和CPU出来的数据都要经过FPGA处理后,才能在LED显示屏上显示出来。根据对引脚数量及内部逻辑资源的需求分析,我们选择了Intel公司的Cyclone IV EP4CE40F29 FPGA芯片。该芯片共有780个引脚,40K的LEs逻辑资源。完成全部开发后,共使用了92%的引脚和81%的逻辑资源。

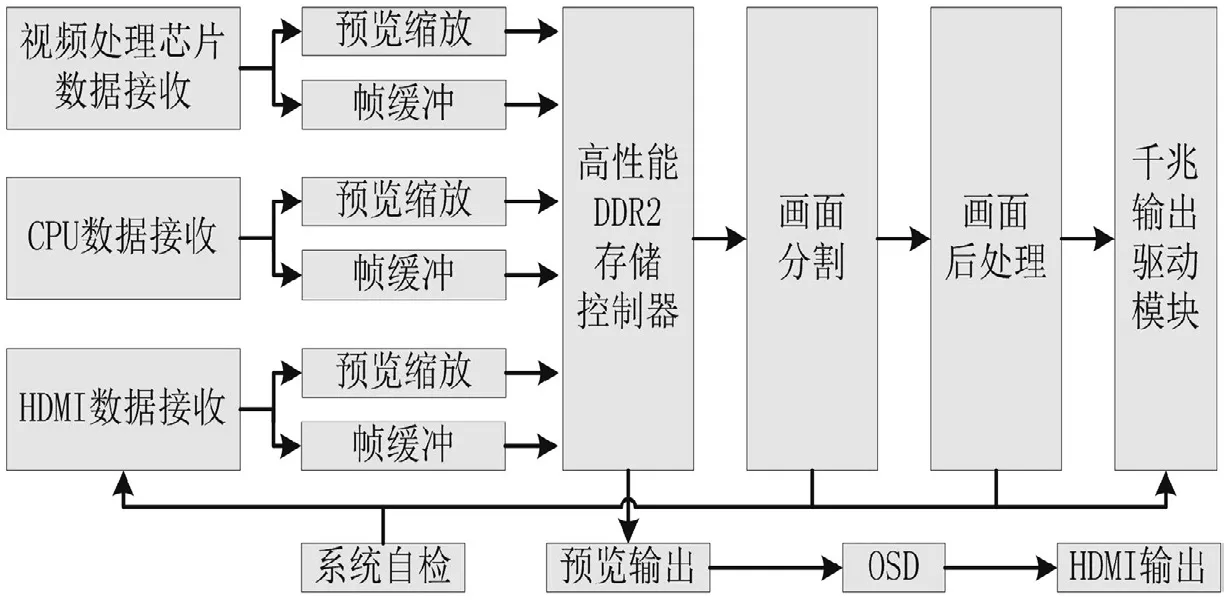

FPGA内部系统框如图1所示。

图1 FPGA内部系统框

FPGA需要同时接收来自视频处理芯片,CPU,HDMI接收芯片的数据,处理后,还要通过6路千兆网输出到LED显示屏。因此,FPGA芯片需要很高的数据吞吐率。我们设计了144 bits位宽的DDR2存储器接口及高性能存储控制器,满足了整个系统的带宽需求。

为了便于用户实时监视信号源的状态,我们为控制器设计了预览功能。用户可以通过操作面板上的按键一键调出3路信号源的实时画面。同时,通过OSD技术,我们将关键系统信息叠加到预览监视画面,让客户实时感知系统状态,第一时间发现异常。

整个系统具有高度的灵活性,每个功能模块的参数可通过CPU数据交互接口实时动态配置,并即刻生效。满足了实际应用中多样化的需求。

系统内建自检功能。可以自行完成板载硬件的测试工作并输出测试报告。为运维人员的故障排除提供可靠依据。

LED显示屏输出接口选用业界通用的千兆以太网物理层(Physical Layer,PHY)。利用这种成熟通用器件提高数据传输系统的性价比。因为每路千兆以太网只有1 GB的带宽,要实现6 GB的总线带宽,需要6路千兆网芯片并行输出。因

此,系统需要画面分割功能。将一个完整的画面按照LED显示屏实际布线进行分割后,输出给千兆网驱动模块,最终完成显示数据到显示屏的传输。

4 结语

本文根据小间距LED显示屏的应用特点,设计并实现了一款集高带宽LED控制器、视频处理器、信源切换器、画面拼接器和监视器等功能与一体的控制器。通过提高系统的集成度,简化了整个系统的复杂度,降低了系统成本,提高了系统可靠性和易用性。目前该控制器已产品化并大量应用于实际的小间距LED显示屏工程项目中,取得了较好的经济效益和不错的用户口碑。

[参考文献]

[1]魏洵佳.带有视频图像处理功能的一体化LED显示屏控制器[J].中国集成电路,2012(8):71-76.

[2]ST半导体公司.STDP9320 data brief.pdf[EB/OL].(2012-12-12)[2018-04-04].http://www.st.com/resource/en/data_brief/stdp9320.pdf.