声纳数据分布式冗余传输系统设计

王冬冬,晏慧强,吕国飞

(上海船舶电子设备研究所上海201108)

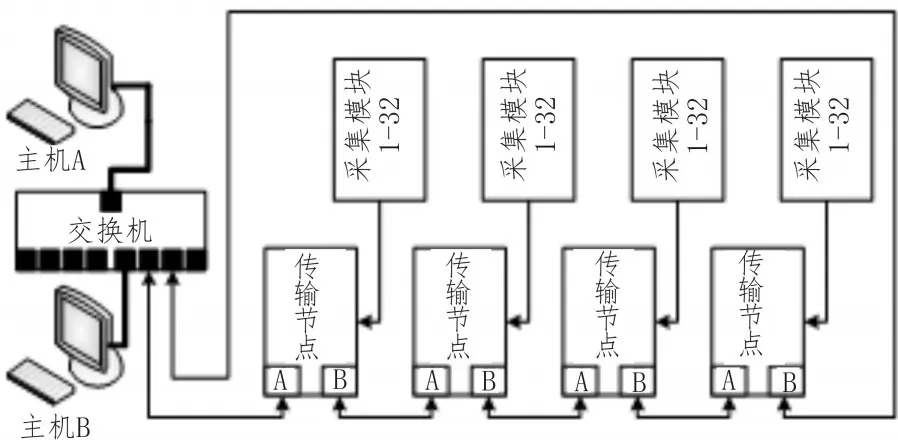

近年来,声纳系统的探测性能不断提升,主要表现在探测距离的不断增加以及方位分辨能力的不断提高。增加阵元规模可以获得较高的阵处理增益和方位分辨力,但同时也造成数据量的大幅增长。拖线阵声纳大规模发展背景下,高速数据流的实时可靠传输意义尤为重大。千兆以太网具有通信速率高、传输距离远、工作可靠性高等优点,将千兆以太网技术应用到拖线阵声纳设计中,可以满足目标数据的实时采集传输及处理要求。

拖线阵声纳特殊的工作环境,决定了其传输系统必须具有较高的工作可靠性,为此,必须在千兆以太网数据传输的基础上增加冗余机制。常见的冗余传输方案适用性较差,难以用于拖线阵传输链路设计,文中提出了一种兼顾布线复杂度、传输距离以及链路利用率的双向环路冗余传输方案。

1 千兆以太网数据传输功能实现

传输节点设计基于物理层和MAC层,不涉及高层协议,去除了上层协议中有关流量控制和差错检测等操作。由于没有上层协议为程序提供统一的服务接口,基于底层的开发较为复杂。开发过程中通过调用Xilinx公司提供的Embedded Tri-Mode Ethernet MAC Wrapper IP核,简化了开发过程,缩短了开发周期,提高了系统工作稳定性。

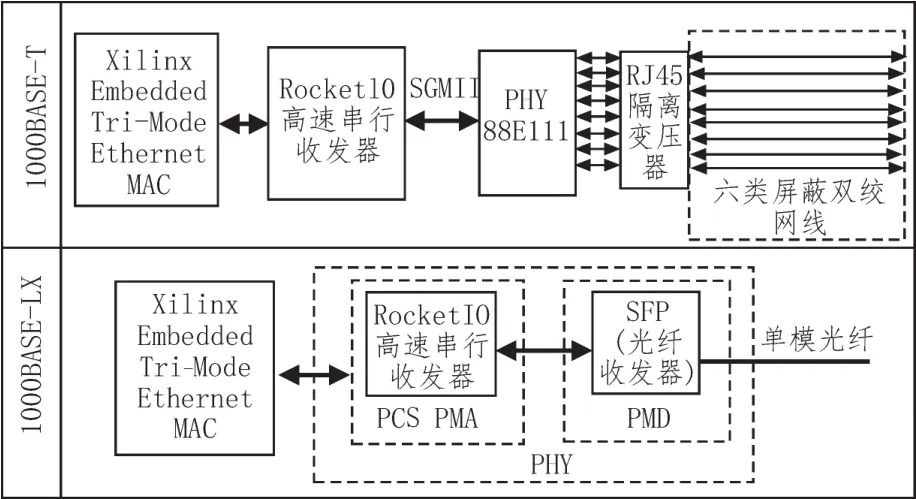

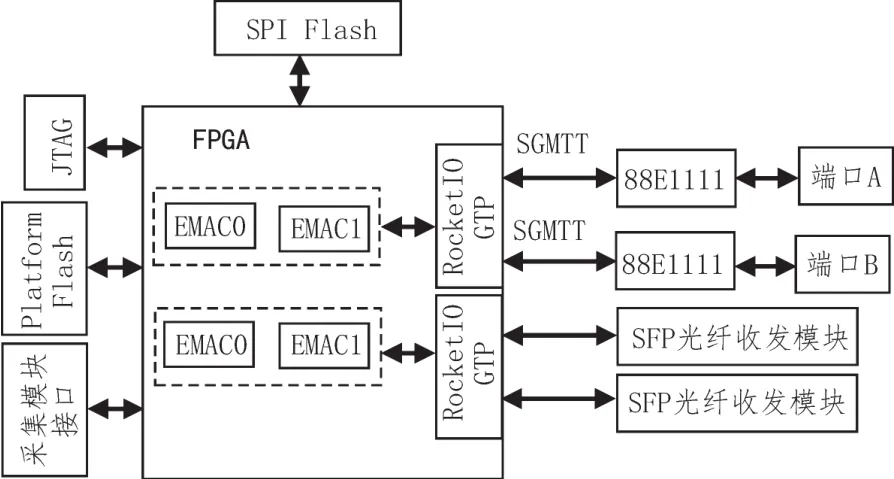

1.1 物理层实现

物理层的设计需要实现PCS(物理编码)子层、PMA(物理介质附属)子层以及PMD(物理介质相关)子层的功能。如图1所示,以双绞线为传输介质的1000BASE-T标准不支持MAC与双绞线的直接互连,设计选用MARVELL公司的88E1111芯片来实现物理层的PCS、PMA以及PMD子层。该芯片支持1000BASE-T千兆以太网标准,能够实现吉比特数据速率下的均衡、回波和串扰消除、数据恢复以及差错检测等功能,具有低功耗特性,在复杂噪声环境中能提供稳健的性能表现。

图1 1000BASE-T及1000BASE-LX物理层的实现

以单模光纤为传输介质的1000BASE-LX标准中,PCS子层和PMA子层通过FPGA芯片内的RocketIO GTP高速串行收发器实现,将GTP与光纤收发模块相连便可实现PMD子层的功能。GTP中PMA子层主要完成8 bit位宽MAC帧数据与RocketIO串行数据间的转换,并从接收数据流中恢复出时钟。PCS子层负责8b/10b编解码及CRC校验。

1.2 MAC层实现

MAC层主要完成数据帧的封装和解封,以及地址匹配等操作。设计中选用Xilinx Virtex5 LX110T FPGA芯片,该芯片内部集成了嵌入式三态以太网MAC控制器硬核,通过对其进行例化来实现以太网MAC控制器功能。MAC控制器支持MII、GMII、RGMII以及SGMII等多种接口模式,用于与PHY芯片对接,并提供MDIO/MDC接口来对PHY芯片的配置寄存器进行读写,以完成工作方式配置或工作状态读取。设计中为了方便PCB板布线,将MAC控制器和PHY芯片都配置为SGMII接口模式。SGMII模式仅使用两对差分线进行数据收发,MAC控制器需要先通过RocketIO GTP实现串/并转换。考虑到GTP收发器中PCS子层的8b/10b编码,同样提供1 000 Mbps的通信带宽,GTP工作时钟频率将高达625 MHz。工作频率越高,GTP对时钟抖动越敏感,因此每对收发器均需使用独立的高精度有源差分晶振。

1.3 MAC控制器配置

MAC控制器支持多种工作模式,全双工半双工、百兆千兆速率、MIIGMIIRGMIISGMII接口、1000BASE_T1000BASE_X PCS/PMA等。MAC控制器硬核中包含两个MAC控制器MAC0和MAC1,两者共享HOST配置寄存器访问总线,通过HOST总线可以对相关寄存器进行配置,结合HOSTEMAC1SEL选通信号,完成对MAC0及MAC1的配置。程序采用有限状态机结构,在125M时钟的驱动下依次进行状态跳转,首先将HOSTEMAC1SEL置为0,向12个配置寄存器中写入相应值,对MAC0进行配置,然后将HOSTEMAC1SEL取反,再次向12个配置寄存器中写入相应值,对MAC1进行配置。

2 双向环路冗余传输设计

现有的拖线阵传输系统大致可分为三类:基于单向级联结构的开路传输、基于星型网络拓扑结构的冗余传输以及基于总线型网络拓扑结构的冗余传输。由于可靠性、传输距离以及布线的复杂度等因素的制约,以上3种组网方案均不能很好地适应拖线阵大规模发展的需要,为此,论文提出了具有高度适用性的双向环路冗余传输方案。

2.1 几种常见的传输节点组网方案

2.1.1 单向级联开路传输

单向级联开路传输节点组网方式如图2所示,应用此方案的传输系统,任意一传输节点的断路或故障,都会使该节点位置以后的级联模块无法正常工作,这种连接方式虽然结构简单,但可靠性较差,会增加整个传输链路故障的概率。

图2 单向级联开路传输组网示意图

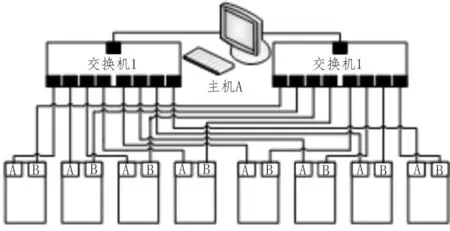

2.1.2 基于星型网络拓扑结构的冗余传输

不少传输系统采用基于点对点的星型拓扑结构,如图3所示,这种组网结构最大的特点是可靠性高,任一传输节点的故障或开路都不会影响网络中其他节点与主机的通信。但这种冗余传输方案不适用于大规模拖线阵声纳的数据传输。一方面,随着传输节点的增加,线束数量剧增,而拖线阵内空间狭小,布线将会变得非常困难。另一方面,数据采集模块主要位于主动接收段和被动接收段,采集数据最远需传输近200米才能到达阵首,而以双绞线为传输介质的1000BASE_T标准支持的最远传输距离仅为100米,因此系统必须采用多级转发机制才能实现双绞线链路上的数据传输。

图3 基于星型结构的冗余传输组网示意图

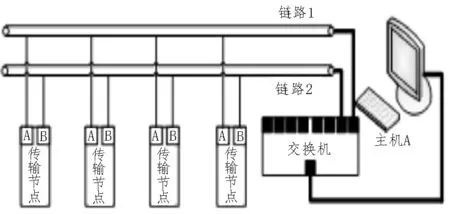

2.1.3 基于总线型网络拓扑结构的冗余传输

如图4所示,一些数据传输系统采用基于总线的结构,将多个传输节点挂接在总线上,这些传输节点对总线的访问具有独占性,会造成总线资源的浪费,进而导致数据传输效率低下。对于大规模拖线阵,总线上挂接的节点数量庞大,还需考虑总线的驱动能力,电流、电压驱动能力往往限制数据的传输距离,同时严格的阻抗匹配实现起来也比较困难。

2.1.4 双向环路冗余传输

如图5所示,双向环路冗余传输链路中任意两节点间数据传输都是基于点对点的通信,无需考虑多个节点对链路的竞争,同时多节点转发机制也可以保证相邻两节点间的距离不超过60米,此外,由于采用非并行组网,布线也较为简单,因此双向环路冗余传输方案能够较好地适应大规模拖线阵声纳数据传输的需要。

图4 基于总线结构的冗余传输组网示意图

图5 双向环路冗余传输组网示意图

2.2 双向环路冗余传输工作机制

设计中两个方向的链路均可独立进行数据收发操作,工作时同一原始报文会被标上相同的时间戳,然后沿两个方向分别发送出去,各传输节点对添加时间戳后的报文进行转发。当传输链路中某一节点因故障无法正常工作时,环形链路被分割为两条独立的数据传输链路,主机可分别沿故障节点的上游链路和下游链路(即反向链路与正向链路)、从不同的两个方向接收数据,这种冗余发送机制使得传输链路具有一定的容错工作性能,提高了链路的工作可靠性。

另一方面,当传输节点某一方向接收出现误码时,可利用另一方向的接收数据对错误进行纠正。接收数据时节点根据时间戳判断两个方向上到来的报文是否为相同报文,两个方向上报文的到达时间存在差别,设计中通过时间优先序列的方法处理冗余报文的接收。若先到达的报文通过校验,则节点从先到达的报文中接收数据,并在接收列表中的相应位置写入时间标戳。当另一方向上相同时间戳的报文滞后到达时,节点检测到接收列表对应位置已写入值,则将滞后到达的报文丢弃。若先到达的报文未能通过校验,接收列表中的相应位置为空,则滞后到达的报文有机会对先前的误码传输进行纠正。一包数据接收完成,系统对接收列表进行清空,保证前一包数据的接收列表不会影响下一包数据的接收。采用这种机制提高了报文接收的可靠性,进一步增强了传输链路的稳健性。

2.3 双向环路冗余传输实现方法

2.3.1 独立收发端口设计

Xilinx XC5VLX110T FPGA片内资源丰富,集成了2个三态以太网MAC控制器硬核。每个MAC控制器硬核包含两个MAC控制器,共享Host Bus配置寄存器访问总线。传输节点设计时同时对FPGA芯片内的2个三态以太网MAC控制器硬核进行例化,将其中的一个通过RocketIO GTP收发器分别与两片千兆以太网PHY芯片相连,再连接到两个RJ45,形成两个独立的数据收发网口,另一个MAC控制器硬核通过RocketIO GTP收发器分别与两个光纤收发模块相连,构成两个独立的数据收发光口,传输节点结构如图6所示。

采用这种设计,一方面便于环形组网,以实现双向环路冗余传输。整个传输网络的组建基于环形拓扑结构,这样当一个传输方向上出现节点故障时,主机可以从另一方向发送或接收数据帧,保证整个传输链路具有一定的容错性能。另一方面也可以实现类似流水级的操作,能够有效降低链路中多个节点间的传输延迟。

图6 单个传输节点结构框图

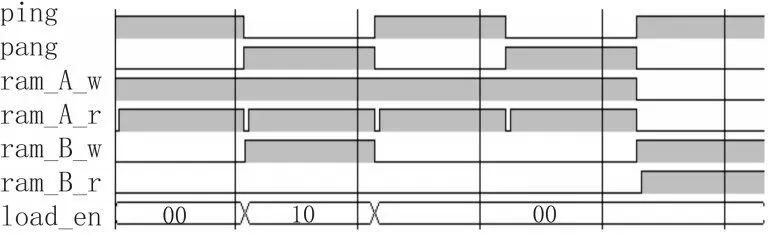

2.3.2 双重乒乓切换机制

参数下发过程中,传输控制板仅仅需要对来自上一传输节点的数据进行转发,不涉及本地数据处理。考虑到传输控制板上不同端口的数据收发时钟不一致,可能出现接收数据未稳定就将其发送出去的情况,为了避免收发操作冲突,需要对接收到的数据进行缓冲处理。设计中利用Xilinx Block Memory Generator IP核实现异步双端口RAM,将双端口RAM划分为高位地址段和低位地址段。

数据转发开始,系统从RAM高位地址段读取数据,同时将来自上一传输节点的数据写入RAM低位地址段缓存,待接收一帧数据和发送一帧数据均完成,RAM高位地址段与低位地址段进行乒乓切换。依次循环,RAM高、低位地址段相互配合,节拍性地进行乒乓切换,完成对数据的无缝缓冲与发送,便于多个传输节点间实现流水级转发,能够有效降低传输延迟。

与参数下发不同,数据上传过程中,传输控制板不仅需要对来自上一传输节点的数据进行处理,同时还需要处理来自本地采集模块的数据。考虑到来自上一节点的数据对应的采集时间稍早于本地采集数据,因此前一节点数据处理的优先级必须高于本地采集数据处理,设计中采用双端口RAM先对来自本地采集模块的数据进行缓存,在下一传输周期的起始段对缓存数据进行读取并将其发送出去。

为了避免本地采集数据缓存与前一节点数据转发之间相互影响,可以将本地采集数据与来自前一传输节点的数据分开缓存,即在原先RAM内部高低位地址段乒乓操作的基础上增加双RAM间的乒乓切换,若传输节点总数为N,则每完成一帧数据的发送或接收,进行一次高低位地址段乒乓切换,每完成N次高低位地址段乒乓切换,一个完整转发周期内的全部采集数据可以经链路上传至接收主机,进行一次双RAM间的乒乓切换。

采用双重乒乓切换机制实现多个传输节点间的流水级转发,保证了高速采集数据流数据能够连续不断地传送到干端进行处理,且采集数据能够按时间先后以及节点号顺序依次排列,接收端无需对收到的报文进行重新排序,效率较高。

3 同步采集控制设计

工作时水听器数据采集模块通过SPI串行总线与传输控制板对接,数据接收前主机会下发同步接收命令,传输控制板正确接收到命令帧后利用PLL对参考时钟(64 MHz)输入进行分频处理(计算见公式(1)),产生相应的同步脉冲(24.576 MHz)。在同步脉冲的驱动下,采集模块进行AD转换,同时传输节点对采集数据进行读取。方案中没有直接选用24.576 MHz的有源晶振,而是利用FPGA内的PLL对输入时钟进行分频,采用这种方案的优势在于:对于非常见规格的采样时钟频率值,设计能够实现软件可重配置,使得数据采集模块的适用范围更广。

(反馈系数M=48,预分频系数D=5,后分频系数P=25)

FPGA中每个PLL单元最多仅支持5路分频时钟输出,而每个传输控制单元需产生32路同步时钟信号,以驱动数据采集模块工作,因此设计中选用时钟分配芯片对输入时钟进行多路复制输出。

考虑到32路同步采集电路中一部分与传输控制模块相距较远,为了增加同步时钟信号的传输距离,设计中先通过差分驱动器将TTL电平转换成LVDS差分信号进行传输,在接收端再使用差分接收器恢复出TTL电平。

4 光纤链路备份设计

光纤质地脆,机械强度差,易折易碎,在耐腐蚀性、反复插拔操作、抗外力拉伸和抗弯折等方面的工程可靠性相对比较脆弱,因此光纤链路工作状态易出现异常。为了避免因干湿端间的光纤链路异常[17-18]而导致整个传输系统的崩溃,设计中预留了备用光纤收发链路,用于进一步提高传输系统的工作可靠性。

SFP光纤收发模块的LOS引脚输出电平可标示接收光功率正常与否,当链路发生异常,接收光功率低于正常范围,LOS引脚被拉高,输出为高电平。链路正常时接收光功率处于正常范围,LOS引脚输出为低电平。利用FPGA对两个独立SFP模块的LOS引脚输出电平进行检测,当LOS引脚输出为低电平,表明链路处于正常工作状态,使用主链路进行数据收发。当LOS引脚输出为高电平,表明接收到的光功率低于敏感门限,链路发生异常,启用备用链路进行数据收发,具体来说即在FPGA程序中根据SFP_DETCT信号电平的高低来选择使能MAC1、GTP_DUAL的 transceiver1还是 MAC0、GTP_DUAL的transceiver0。

5 仿真及测试

传输控制模块实物图如图7所示。

图7 传输控制模块实物图片

5.1 功能仿真

FPGA功能模块编写完成后需要对其进行功能仿真以验证逻辑设计是否正确,功能仿真也称前仿真,可利用Isim软件完成。由图8中的仿真结果可以看出,每完成一帧数据的发送或接收,程序进行一次高低位地址段乒乓切换,每完成N次高低位地址段乒乓切换,程序进行一次双RAM间的乒乓切换,与预期设计结果相符合。

图8 功能仿真波形

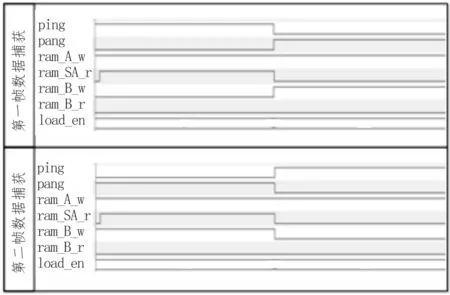

5.2 时序仿真

前仿真不涉及具体的硬件电路时序,还需利用Chipscope在线逻辑分析仪对FPGA内部信号进行在线检测以验证模块是需设计的准确性。图9在线仿真结果表明,RAM高低位地址段能够根据发送及接收计数值自动完成乒乓切换,与功能仿真结果相一致。需要说明的是,设计中一帧数据发送或接收完毕,会留有1 μs的间隙,因此仿真波形中会有帧间隙的存在。

图9 时序仿真波形

5.3 传输节点组网测试

测试链路中首尾两个传输控制模块通过光纤与交换机连接,中间模块使用六类屏蔽网线实现互连,网线长度为58 m。各传输控制模块在同步时钟信号的控制下对采集数据进行读取和转发。与交换机连接的主机成功接收都来自首尾两节点的报文,断开传输链路中任意两传输控制模块间的连接,主机端仍可接收到完整的数据报文,表明双向环路冗余传输机制工作正常。

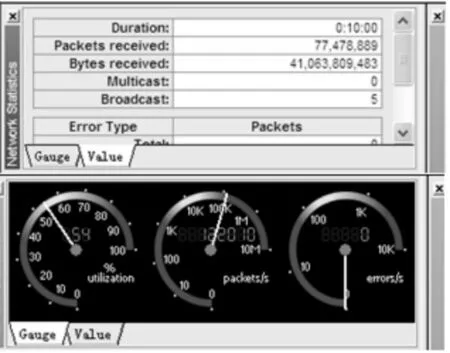

在主机端利用WildPackets Ethernet NX以太网测试软件持续10分钟对链路状况进行监测,测试结果如图10所示。主机B平均每秒接收到约120 000帧数据,帧长为固定值530字节,平均数据传输速率约为500 Mbps(设计中每一帧数据接收或发送完成后留有一定的间隙,减小帧间隙时间值可在一定程度上提高传输速率)。

图10 主机端传输速率及误码率测试结果

6 结论

本文针对拖线阵声纳大规模发展的需求,基于千兆以太网物理层及MAC层自定义协议开发了传输控制单元,实现了高速采集数据流的实时传输。同时,基于冗余传输思想,对多个传输控制单元进行了环路拓扑结构组网,赋予系统一定的容错工作性能,增强了拖线阵声纳系统的工作可靠性。测试结果表明,多节点传输链路的平均数据传输速率高于500 Mbps,并且容错机制能够高效、稳定地发挥作用。方案设计合理、工程可实现性强,对高速数据采集传输系统的设计具有重要的参考意义。

参考文献:

[1]瞿鑫,吴云峰,李华栋,等.基于FPGA的千兆以太网数据传输的设计与实现[J].电子器件,2014,37(4):68-71.

[2]张金凤,李耀南.基于千兆以太网的高速数据传输系统设计[J].火控雷达技术,2014,43(2):19-22.

[3]刘鑫,孙大军,田原,等.一种高速声纳实时处理系统的设计与实现[J].嵌入式技术,2013,39(4):12-15.

[4]伍新维,付仲满,章建雄.千兆冗余以太网链路状态检测技术[J].计算机工程,2013,39(12):75-78.

[5]王一茗,张可,陈龙.一种高可靠可控双冗余以太网的设计与实现[J].计算机科学,2014,41(5):97-101.

[6]马文超,张涛.一种基于FPGA的千兆以太网高速传输平台[J].计算机工程,2012,38(1):242-244.

[7]朱佳齐,白广治,许晏,等.基于FPGA的嵌入式串行以太网设计设计[J].仪表技术与传感器,2012,12(11):5-7.

[8]王宇聪,韩启祥,蔡惠智,等.声呐信号处理中UDP协议数据传输研究与设计[J].现代电子技术,2012,35(1):78-79,84.

[9]候以合,张冬冬,丁雷.基于FPGA+MAC+PHY的千兆以太网数据传输系统设计[J].科学技术与工程,2014,14(19):662-664.

[10]韦宏,付友涛,孔凡鹏,等.基于FPGA的千兆以太网设计[J].现代电子技术,2012,35(18):56-59.

[11]史鹏腾.基于千兆以太网的FPGA多通道数据采集系统设计[J].电子技术,2015,28(2):123-126.

[12]何琼,陈铁,陈鑫.基于以太网硬协议栈的数据采集节点[J].仪表技术与传输器,2013(2):21-23.

[13]袁阳,孟李林.基于FPGA的千兆以太网数据传输设计[J].电子科技,2016(2):156-158,162.

[14]张志伟,靳鸿,穆蔚然,等.基于千兆以太网的机载雷达数据采集系统设计[J].现代雷达,2016(9):57-60,66.

[15]张克功,李和平,高鑫.基于千兆以太网的雷达数据可靠传输系统设计[J].自动化与仪表,2012(6):26-31.

[16]石金成,张小辉,黄玉刚,等.基于FPGA的两路千兆以太网光纤传输系统[J].光通信技术,2013(7):11-13.

[17]阎家光.光纤传感器在煤矿井筒监测系统中的应用[J].自动化与仪器仪表,2016(12):63-64.

[18]房鸿,付宗,吴旭.双程前向结构掺铒光纤光源的稳定性研究[J].西安工业大学学报,2015(10):784-787.