基于RS 485总线的ADS1258数据采集网络系统设计与实现

高金转 严帅 张会新

摘 要: 针对在航天测试领域中对多个地点处多路模拟信号进行精确采集的需求,设计了相距1 m的6个传感器节点,每个节点10路模拟信号的采集系统。该系统以Spartan?6 FPGA为核心芯片,控制24位精度的模数转换模块、40 Mb/s传输速率的RS 485总线传输模块和USB接口模块的工作,大大简化了以前的测试系统,并提高了采集数据的可靠性和系统工作的稳定性,可广泛应用于对精度要求较高的航天测试系统。

关键词: 数据采集网络; RS 485; ADS1258; USB接口; 系统设计; 传输速率

中图分类号: TN710?34; TP335 文献标识码: A 文章编号: 1004?373X(2018)07?0174?04

Design and implementation of ADS1258 data acquisition

network system based on RS 485 bus

GAO Jinzhuan1, 2, YAN Shuai3, ZHANG Huixin1, 2

(1. National Key Laboratory for Electronic Measurement Technology, North University of China, Taiyuan 030051, China;

2. Key Laboratory of Instrumentation Science & Dynamic Measurement of Ministry of Education, Taiyuan 030051, China;

3. Beijing Institute of Astronautics System Engineering, Beijing 100076, China)

Abstract: In order to accurately acquire the multi?channel analog signals at different sites in the spaceflight measurement field, a acquisition system was designed and implemented, which has 6 sensor nodes for 1 meter, and each node has 10?channel analog signal. The Spartan?6 FPGA is taken as the core chip of the system to control the analog?to?digital conversion module with 24?bit, RS 485 bus transmission module with 40 Mb/s, and USB interface module. The system can simplify the previous test system greatly, improve the reliability of data acquisition and stability of system working, and is widely used in the spaceflight test system with high precision requirement.

Keywords: data acquisition network; RS 485; ADS1258; USB interface; system design; transmission speed

0 引 言

在测试测量系统中,经常需要对多个地点的多个模拟量信号进行精确采集,其测试方法较为繁琐,测试数据精度略低。为简化测试系统并提高采集数据的精度,设计一个网络化的高精度采集系统显得尤为重要。其中,影响整个测试系统综合指标的关键因素之一是A/D转换器的性能参数,故选用具有16路24位高精度的模数转换器ADS1258[1],可获得高保真度、高信噪比、高分辨率的数字信号[2]。网络化则可改善测试方式,使得测试方便易操作,选用TI公司的RS 485接口芯片ISO1176T,具有生命周期更长、可靠性更高、更高速度和更多节点等特性和优势,可满足设计要求[3]。

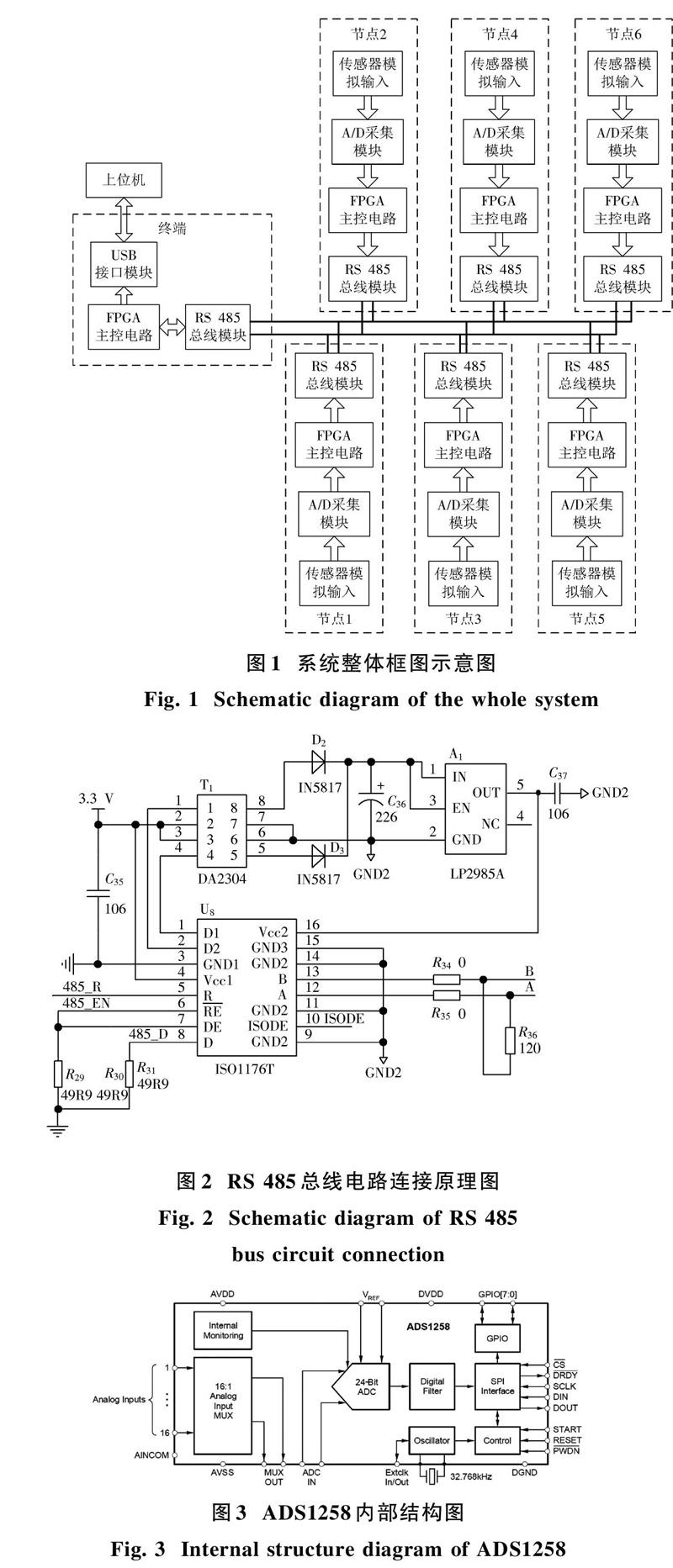

1 系统总体设计

本系统是基于RS 485总线的传感器网络节点的设计,主要实现了对相距1 m的6个传感器节点处共60路模拟信号进行精确采集,并传输至上位机显示,其中传感器节点的设计由A/D采集模块、FPGA控制电路和RS 485总线模块组成,终端的设计由FPGA控制电路、RS 485总线模块和USB接口组成。整体原理框图如图1所示。

系统的总体工作流程为:

1) 上位机发送命令给终端节点,终端解析并重组命令,将其发送至RS 485总线上;

2) 传感器节点均接收RS 485总线上的命令并解析;

3) 命令匹配的传感器节点启动工作进行数据转换,并将转换结果组成数据包发送至RS 485总线上;

4) 终端接收数据重组并通过USB接口上传至上位机。该系统正常工作对总线的要求极高,半双工差分线路收发器ISO1176T芯片作为RS 485总线,可灵活地控制接收和发送,使得系统设计简单且易实现。

2 主要硬件电路设计

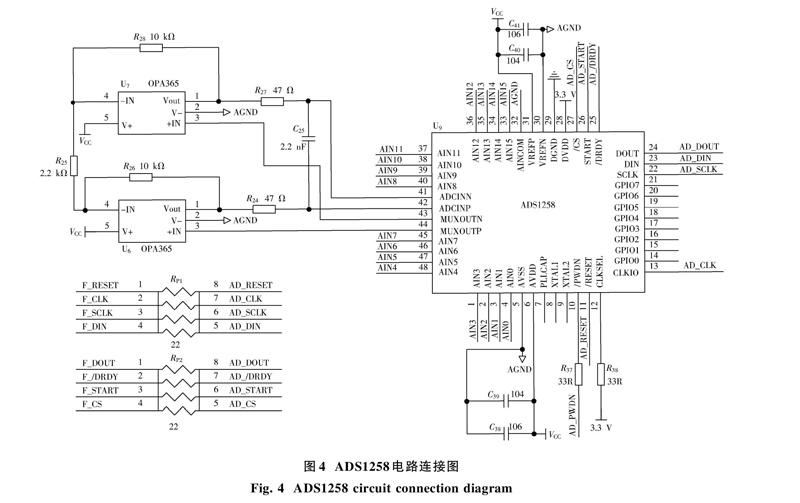

2.1 RS 485总线模块设计

系统设计中,RS 485总线使用的ISO1176T芯片是带集成变压器驱动器的隔离式半双工差分线路的收发器,可支持多达160个节点的连接,工作速率高达40 Mb/s,可以满足该系统设计要求的25 Mb/s的传输速率,与变压器DA2304和稳压器LP2985A配合使用,使得RS 485差分线传输具有高效率及低电磁干扰,能够延长总线的传输距离,进而扩大系统的测试范围,具体的电路连接如图2所示。

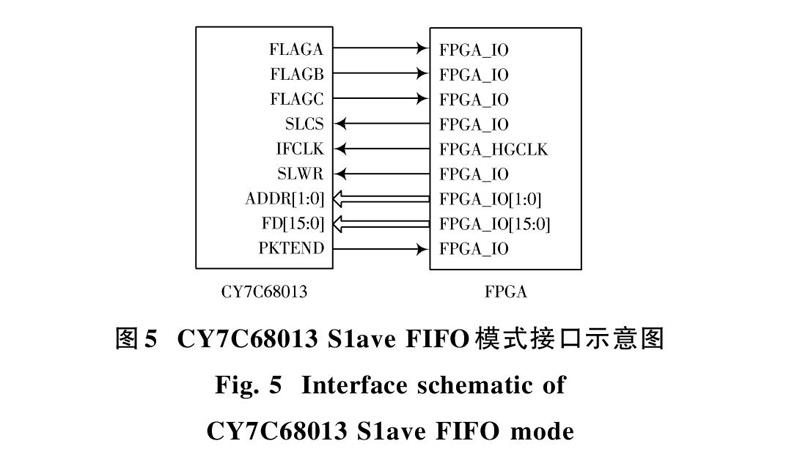

2.2 A/D采集模块设计

数据采集部分的关键在于A/D转换芯片的精度,本系统选取ADS1258转换芯片,其转换精度使得本系统的采集精度更高,并选用其内部滤波器对信号进行滤波,从而简化电路。该芯片的主要特点是固定通道采样速率最高为125 kS/s(可编程),自动检测通道采样速率最高为23.7 kS/s(可编程);模拟输入多路复用器可配置成8路差分输入或16路单极输入[4]。其内部主要由16路复用器、可编程数字滤波器、ADC及基准部分电路、通用输入输出端口和SPI串行接口等组成,如图3所示。

電路设计时,将ADS1258时钟选择管脚CLKSEL拉高,即不使用外部晶振,由FPGA提供时钟,从管脚CLKIO接入,采用5 V单端供电。相比固定通道模式,自动浏览通道模式对控制多路数据通道的工作更灵活,即可控制其转换16通道中任何通道的模拟数据,因此选用该模式工作。具体的电路连接如图4所示。

ADSl258采用4线制(时钟信号SCLK、数据输入DIN、数据输出DOUT和片选/CS)SPI通信方式[5],由FPGA主芯片通过引脚DIN将相关数据输入ADC,对其内部寄存器进行读写控制及工作模式的配置,通过引脚DOUT读取转换数据和寄存器数据。其中,CONFIG0,CONFIGl是结构寄存器[6],可设置芯片的工作模式、采样延长时间、采样频率等;MUXSCH寄存器用于在固定通道采样的工作模式下ADC模块正负端口输入通道的选择设置;MUXDIF寄存器、MUXSGO寄存器和MUXSGl寄存器用于在自动扫描采样的工作模式下差分输入通道与单端输入通道的选择设置。

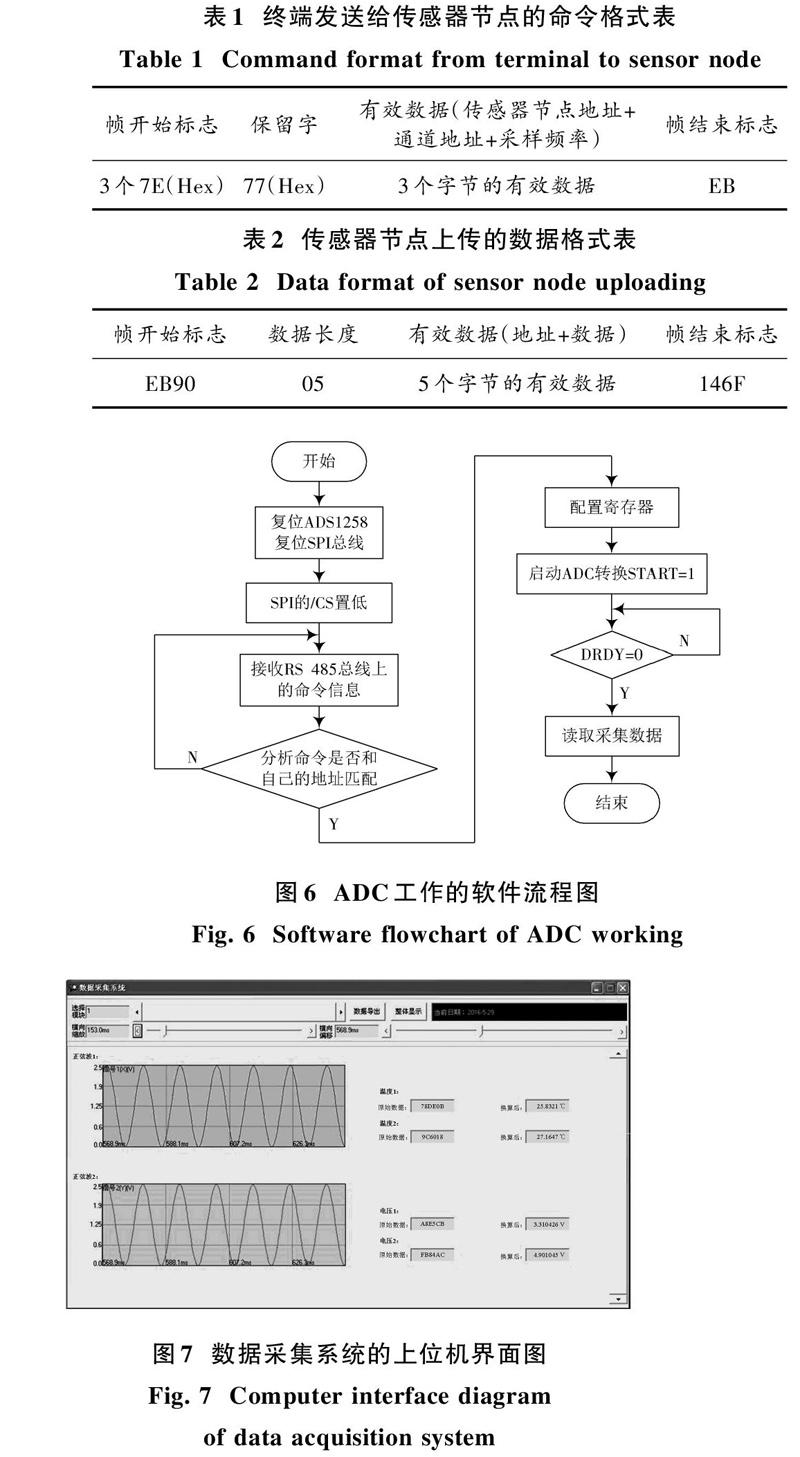

2.3 USB接口电路设计

为满足系统设计中数据的传输速度需求,采用USB 2.0与上位机进行数据和命令的互传。USB接口选用微控芯片,即EZ?USB FX2系列的CY7C68013?56芯片。该芯片具有12 Mb/s的全速传输和480 Mb/s的高速传输功能,可以在3种模式下工作,即GPIF模式、Ports模式和Slave FIFO模式[7]。其中,比较高速的一种模式是Slave FIFO模式,在此模式下,CY7C68013对于FPGA主控芯片而言,相当于从FIFO、主控芯片在工作时钟的上升沿将数据传给芯片的数据总线,芯片接收到数据之后使用智能串行引擎将其打包发送。由此可见,FPGA只需控制好FIFO的相应接口即可实现,如图5所示。

在Slave FIFO模式下,CY7C68013的管脚FIFOADR[1:0]是地址线,控制选择FIFO的某个端点,SLCS管脚是FIFO的片选信号,SLWR管脚控制Slave FIFO的读写操作,FPGA芯片通过对三个标志引脚FLAGA,FLAGB,FLAG的监控来获知当前USB总线通信的状态。

3 系统软件关键技术设计

3.1 RS 485总线通信协议设计

为了使终端能很好地控制各个传感器节点工作和接收相应传感器节点传回来的数据,严谨的总线通信协议是很关键的技术之一[8]。为避免总线上传输的数据受到环境中各种因素的干扰和数据中毛刺的影响,以导致数据传输有误,所以数据包应加上帧头和帧尾。

1) 命令信息

由终端发给各个传感器节点的具体命令格式如表1所示,在HDLC传输协议的基础上,将其中的有效数据改为传感器节点的地址,本系统中设定传感器节点地址依次[9]为01~06。传感器节点识别帧头后开始接收8个字节的命令,对命令解析之后,根据有效数据,相应的传感器节点将相应地址通道转换的数据上传至总线上。

2) 数据信息

由传感器节点上传的长度为10个字节的数据包的具体格式如表2所示。数据包括帧头、帧尾和有效数据,其中有效数据包含地址(传感器节点的地址和通道地址)和模数转换之后的数据(4个字节)。

3.2 A/D采集软件设计

ADS1258芯片中ADC转换程序的软件流程图如图6所示。模数转换芯片开始工作时,给芯片提供16 MHz的工作时钟,复位管脚/RESET置低100 μs,对芯片复位,然后将CS置低4 096个时钟,对SPI总线复位,然后配置A/D芯片的相关寄存器。主要是对三个寄存器的配置,即配置CONFIGl寄存器,其中的DRATE位可设置采样频率;再配置寄存器MUXSG0和寄存器MUXSG1完成对所需通道的采集设置。由于该转换器CONFIG0寄存器中的MUCMOD位的默认值为0,即工作在自动浏览模式下,所以不需要对其进行配置。配置完寄存器之后,启动转换命令START=1,再判断DRDY信号是否置低,置低说明数据准备好,然后通过数据线DOUT输出数据,转换后的有效数据为32位数据,其中高8位为状态字,后24位为ADC转换的有效数据。

4 测试结果

对该数据采集系统进行全面测试。图7是各节点中第一通道采集的数据,并上传至上位机显示。传感器节点1和传感器节点2分别对峰峰值为2.5 V的正弦波进行采集,从上位机图像上看,波形稳定无毛刺,且显示数据基本正确;传感器节点3和传感器节点4分别用温度传感器采集26.32 ℃和27.64 ℃的温水,上位机显示的数据也很接近原始数据;另外2个传感器节点分别采集的是幅值为3.3 V和5 V的直流电压,采集之后换算的数据几乎接近。由此可见该A/D采集的精度较高。

5 结 语

本文设计了一种基于RS 485总线而建立的数据采集网络系统,选用FPGA为主控芯片,控制RS 485总线芯片ISO1176T的收发和模数转换芯片ADS1258的多路采集,实现多个传感器节点的多通道数据采集,并详细说明了主要硬件电路设计和系统软件设计的关键技术。测试结果显示,该数据采集网络工作稳定,并实现了各传感器节点的数据采集,且采集的数据稳定,采集精度满足指标要求。

参考文献

[1] 高俊杰,谢宏,杨文璐,等.基于WiFi的医学信号采集系统研究[J].单片机与嵌入式系统应用,2012,12(8):38?41.

GAO Junjie, XIE Hong, YANG Wenlu, et al. Research on medical signal acquisition system based on WiFi [J]. Microcontrollers & embedded systems, 2012, 12(8): 38?41.

[2] 宋楠,陈箫,李锦明,等.基于ADS1258的高精度信号采集电路设计[J].电源技术,2011,35(12):1566?1567.

SONG Nan, CHEN Xiao, LI Jinming, et al. Design of high precision signal acquisition system based on ADS1258 [J]. Chinese journal of power sources, 2011, 35(12): 1566?1567.

[3] 佚名.德州仪器推出具有集成驱动器的Profibus RS 485收发器[J].电子与电脑,2011(3):80.

Anon. Texas instrument launches Profibus RS 485 transceiver with integrated drive [J]. Compotech China, 2011(3): 80.

[4] 吴平,骆朝亮.基于USB的ADS1258传感器信号采集系统[J].软件导刊,2010(6):65?67.

WU Ping, LUO Chaoliang. ADS1258 sensor signal acquisition system based on USB [J]. Software guide, 2010(6): 65?67.

[5] 刘源,柯玉涛,周宇辰.基于ADS1258的多路信号采集系统的设计[J].信息系统工程,2014(3):143?144.

LIU Yuan, KE Yutao, ZHOU Yuchen. Design of multi?channel signal acquisition system based on ADS1258 [J]. China CIO News, 2014(3): 143?144.

[6] 郑润娜,张晓春.RS 485总线的理论与可靠性分析[J].科技信息,2011(32):125.

ZHENG Runna, ZHANG Xiaochun. The theory and reliability analysis of RS 485 bus [J]. Science & technology information, 2011(32): 125.

[7] 吴磊,郭超平,申世涛.基于CY7C68013与FPGA的便携式数据采集系统[J].计算机应用,2012,32(z1):164?166.

WU Lei, GUO Chaoping, SHEN Shitao. Portable data acquisition system based on CY7C68013 and FPGA [J]. Journal of computer applications, 2012, 32(S1): 164?166.

[8] 周倩.基于FPGA的高速数据釆集系统控制模块设计[J].电子科技,2012,25(5):14?16.

ZHOU Qian. Design of high?speed data acquisition control mo?dule based on FPGA [J]. Electronic science and technology, 2012, 25(5): 14?16.

[9] 王剑.基于FPGA的高速多路同步数据采集系统[J].科技视界,2013(27):42?43.

WANG Jian. High?speed multi?channel synchronous data acquisition system based on FPGA [J]. Science & technology vision, 2013(27): 42?43.