基于ZYNQ平台的一体化控制组合

湖北三江航天红峰控制有限公司 吴旭亮 岳惠峰 周粉利 雷战克 荣洪刚

1.引言

随着技术的发展,特别是控制系统中,FPGA+ARM 构建的处理系统的应用越来越广泛,相对其他处理系统更加轻便灵活。Xilinx 公司推出的 Zynq-7000 系列全可编程片上系统(以下简称Zynq)就采用了 FPGA+ARM 结构,其集成 ARM Cortex A9 双核(ProcessingSystem,PS)以及最多可达相当于 500 多万个逻辑门可编程逻辑(Programmable Logic,PL)单元。这种硬件架构改变了传统的 FPGA+ARM/DSP 核架构,提供了单 CPU、多处理核、FPGA 和 ARM 内部高速互联的新型解决方案,使用单片 FPGA 能很好地完成工作,能够灵活地用于各种领域。

在对传统弹/箭上电气系统共性电路资源、专用电路资源进行分析、研究的基础上,制导控制组件将通常控制计算机、时序控制器、舵机控制、电源配电器进行功能上的一体化集成和电路设计上的深度融合,结合一体化处理软件,由一台制导控制组件实现原来多种设备的功能。

本文利用ZYNQ的性能,解决了高速与微型的矛盾,成功研制出了集高速度、高精度、小型化、集成式于一体的基于ZYNQ平台的一体化控制组合,并通过了地面的性能测试。

2.一体化控制组合总体设计

以低成本、通用化、集成式、模块化制导控制组合设计和研制为需求,开展基于ZYNQ平台的一体化控制组合技术研究,构建一体化制导控制组合统型技术指标体系,突破传统的总体方案与架构设计思想,打破传统的以功能划分的各子系统为基础进行单独设计的思路,采取硬件资源统筹规划,以功能模块化、通用化、组合化为设计理念,建立电气、通信、机械接口、软件架构等设计与应用规范体系,将各子系统中的电子设备接口软硬件进行集成设计,减少系统内冗余器件,减小主控组件体积、降低设计成本,提高系统的基本可靠性和环境适应性。

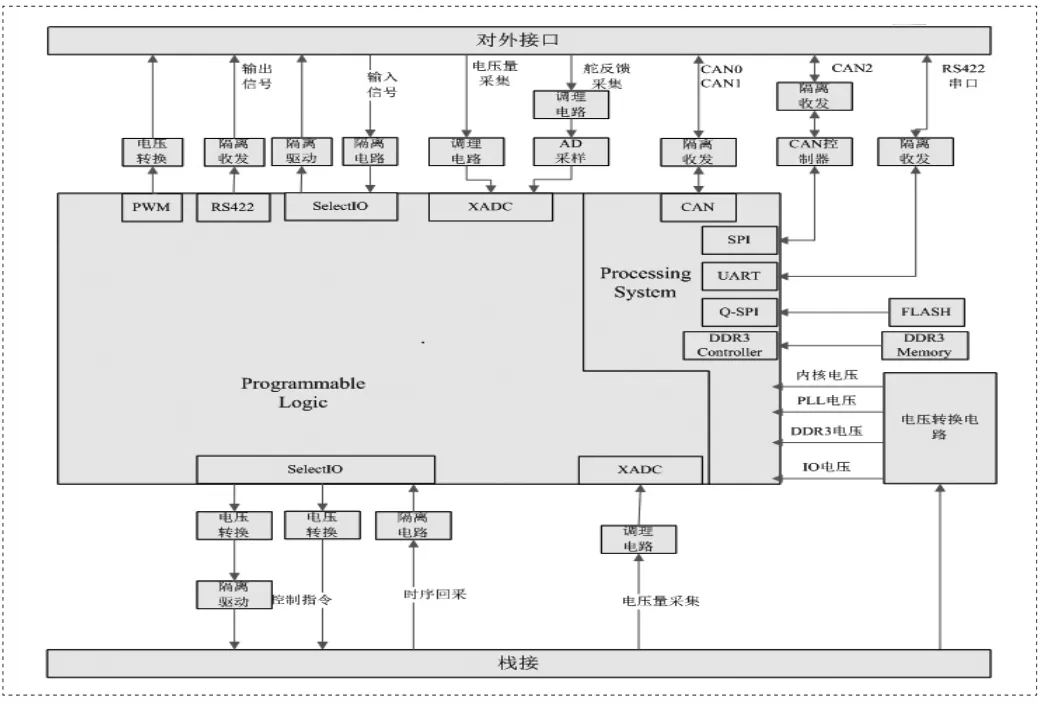

一体化控制组合设备内部划分为SoC控制模块、配电时序模块、舵机功放模块。各模块功能独立、通用,接口统一、标准。适应系统CAN总线架构,设备对外接口主要为配电电源、通信接口、PWM舵机接口、时序接口、模拟采集接口等。

图1 一体化控制组合原理框图

3.方案设计

在一体化控制组合方案设计之前,要对控制组合的任务和实现的目标作需求分析。根据总体的要求、控制对象的复杂程度以及控制规律的运算数据量大小,选择控制周期;按照控制周期内控制计算量来确定弹上计算的类型和运算速度,并结合外部单元确定开关量接口方案、通讯接口方案、计算机组成架构以及对抗干扰因素的考虑,可确定整体的通讯协议、接口形式以及结构形式。

3.1 SoC控制模块设计

SoC控制模块的设计通常采用自上而下的方法。按照总体需求定义顶层的接口和参数,再确定底层的子系统或功能。采用Zynq平台的一个特别的优势就是处理器和可编程逻辑之间的强耦合,即两者部署于同一芯片上。在PS和PL之间以低延时,高性能的AXI连接,这允许性能不同的两种资源可以在系统被分割为软件和硬件两部分时同时发挥其最高性能。这是由于与两者分离设计的系统相比,这种模式在通信开销上有大量减少,同时大幅降低了系统硬件复杂程度,提高了系统工作可靠性。

SoC控制模块主要组成包括:SoC处理器电路和通信接口电路、A/D调理电路、PWM接口电路、I/O接口电路、备用接口电路等外围接口电路,模块原理框图如图2所示。

图2 SoC控制模块原理框图

3.2 配电时序模块设计

配电时序模块主要由DC/DC转换电路、转电、断电控制电路、开关量驱动电路、状态采集电路组成。主要包含以下功能:a)DC/DC转换电路:将28V电源转换为±15V和+5V输出至SoC控制模块;b)转电断电电路:接收转电、断电指令,完成转电断电的配电功能;c)时序输出电路:采用固体继电器对母线电源的正负分别进行管制,采用磁保持继电器对关键信号短路、断路保护,同时实现状态自动采集判断,实现安全管制功能,增加系统安全性;d)状态采集电路:完成时序状态采集监测到SoC控制模块。

3.3 舵机功放模块设计

舵机功放板主要由H桥功率放大电路、二次电源电路及光耦隔离电路等部分组成。主要包含以下功能:a)H桥功率放大电路:接收舵机控制PWM波信号,实现电机功率驱动;b)二次电源电路:将28V电源转换为15V提供给驱动电路;c)光耦隔离电路:将控制器发送的PWM控制信号隔离后发送给驱动电路。

3.4 结构设计

基于ZYNQ平台的一体化控制组合由时序电源模块、SOC控制模块、舵机功放模块组成,三部分结构设计为层叠堆栈形式,结构紧凑,可扩展性强,方便后续产品升级。为满足恶劣环境工作可靠性,对安装壳体进行局部加强,改善印制板的振动环境。为了合理控制系统热性能、ZYNQ芯片部分增加导热垫,将发热量大的器件直接与上盖板直接接触,通过壳体进行散热。

4.软件框架和应用功能实现

一体化控制组合软件主要有以下几部分:ZYNQ-7000芯片配置、内部AD、片外AD、时钟分频、时序输入接口、时序输出接口、PWM控制等。一体化控制组合软件开发环境为Vivado2015.4及SDK,IP核使用Verilog硬件描述语言,FPGA软件采用Block实现方式。

4.1 基于AXI总线外围接口IP核设计

在SOC系统设计中,高级微控制器总线结构(Advanced Microcontroller Bus Architecture,AMBA)被广泛采用,已经迅速成为SOC结构和IP 核开发的标准。AXI4、AXI4-Lite、AXI4-Stream这三种总线标准是AMBA4.0的重要组成部分。AXI4总线有助于最大化性能和能效;AXI4-Lite总线和AXI4-Stream总线亦可以在特定应用中简化数据传输通道设计[1]。

为简化ZYNQ处理器对外围慢速接口处理,一体化控制组合SoC控制模块通过ZYNQ处理器的PL端口FPGA资源扩展外围接口,如模拟量采集芯片AD7656读写控制、开关量接口扩展及防抖处理、PWM信号输出等均通过基于AXI4-Lite总线的外围接口IP核实现。ZYNQ处理器ARM端直接通过地址读写即可实现状态判断及输入输出控制,大大简化了ARM端驱动程序复杂度。

4.2 FPGA配置与功能模块设计

FPGA软件采用模块化设计方式,其中ZYNQ模块为处理器模块,内部通过图表方式实现对处理器芯片各个参数的配置。其他外围接口部分通过各个独立的IP核实现,每个功能的IP核为一个可视化模块。各个IP核模块地址分配按照技术要求进行。

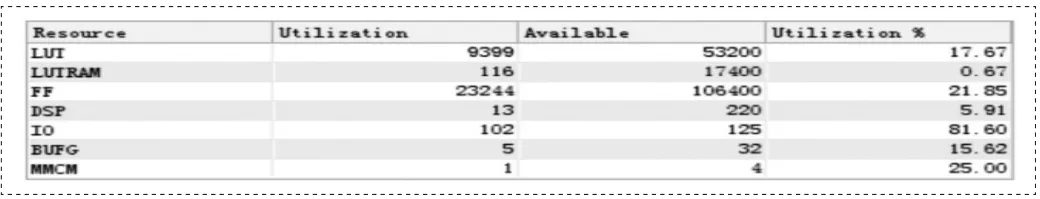

FPGA软件设计部分完成后,通过Vivado2015.4软件生成可执行文件。同时对综合后结果以及布局布线后的结果进行验证复核。FPGA占用资源见图3。

4.3 ARM驱动程序设计

Xilinx的SDK开发工具提供了针对ZYNQ平台的BSP包,BSP包含了ARM的外设接口驱动,BSP提供的ARM外设驱动代码用C编写,移植方便,FPGA部分IP核接口按照地址操作即可实现接口控制。

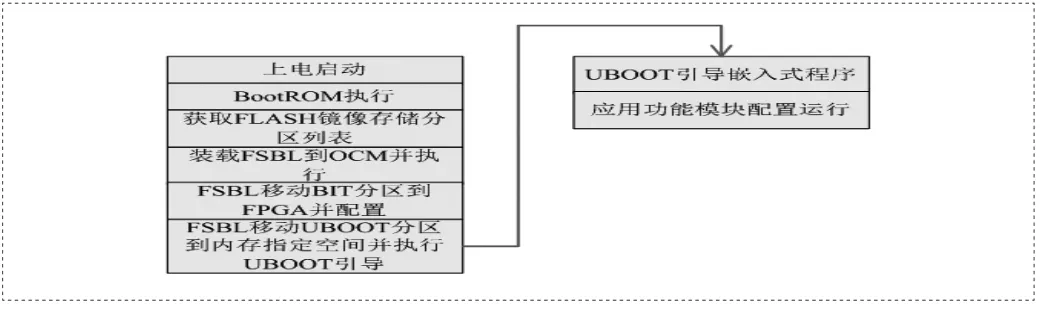

ZYNQ是以ARM为核心的FPGA,平台引导时,先引导ARM核,由ARM配置引导其他部分。引导的主要内容是引导ARM程序和FPGA的BIT配置文件。图4为引导和配置过程[2]。

图3 FPGA资源利用情况

图4 ZYNQ引导和配置过程

4.4 硬件和软件联调

软件和硬件调试分别通过后,就可在样机产品上进行软件和硬件的联调。开展硬件性能测试、软件性能测试、流程测试、系统对接等测试,完成基于ZYNQ平台的一体化控制组合。

5.结束语

本文以基于ZYNQ平台的一体化控制组合为例,以ZYNQ系列多核SoC处理器为核心开发了一体化控制组合,并进行了产品的软硬件设计,通过了地面的性能测试和流程测试。但在正式应用之前,还需经过充分的试验和测试验证(如振动试验、冲击试验、温度循环试验、系统对接试验等),同时要经过必要的工程化过程,希望能够在同类产品或其他型号产品中得到更广泛的应用。

[1]任华锋,王晋华,孙振.基于ZYNQ嵌入式小型化继电保护平台设计实现[J].工业控制.2016:70.

[2]王浩宇,漆晶,谭歆.基于 Zynq-7000 的视频采集平台设计[J].工业控制计算机,2017(12)55-56.