数字设计FPGA应用课程的挑战式实验教学设计

卢有亮,姜书艳

(电子科技大学 自动化工程学院,四川 成都 611731)

“数字设计FPGA应用”课程是在“数字逻辑设计及应用”课程的基础上,针对电子信息专业学生开设的跨专业选修课程,包含了24学时的实验和24个学时的理论课教学,共48学时。该课程通过开课初期组织学生借用口袋实验室实验板来配合课上课下实验的方式进行教学。

在以往的验证性实验和综合性实验的基础上,为进一步培养学生能力,提高综合素质,进行了挑战式学习的教学改革。

在已有实验的基础上,重新进行了实验环节教学内容的设计。针对电子科技大学学生的特点,提出了具有较强挑战性的实验题目并进行了实践,取得了比较理想的效果。

1 挑战式实验的研究

基于问题的学习(PBL)在很多年前就被提出,是一种以问题为核心的,以学生自我管理为主的教学模式,国内外对此已有一定的研究和实践经验[1-3]。使用PBL方法,学生在问题的引导下进行学习,通过解决问题来达成掌握知识及培养能力的目标。挑战性的学习更强调问题的挑战性,侧重于问题的难度、深度及与理论学习和应用的结合程度。挑战式的学习还应注重理论与实践相结合。在高校中最直接的实践就是实验。

实验的重要性毋庸置疑。南京大学的冯端院士曾经说过,实验室的作用怎么强调都不过分,甚至说实验室是现代大学的心脏。文献[4]阐明,实验室就像一个熔炉,让学生进实验室去,通过严格的训练,可以培养他的创新能力。文献[5]认为高校中重理论轻实践的传统思想仍时有反映,高校实验应注重内涵建设,介绍了哈佛大学特色实验课“回家实验”,强调了学生的自主性[5]。在实验的环节,除了已有的验证性实验和综合性实验,引入挑战性实验,将在很大程度上提高学生的综合能力。

另外,好的挑战式学习应该可以激发学生的兴趣,提高学生的求知欲望,激发学生的创造热情,即满足ARCS 模型的4个要素,即注意(attention)、贴切性(relevance)、自信心(confidence)和满足(satisfaction)[6-10]。挑战性学习应该满足这4个要素并具备足够的挑战性。从布卢姆分类教学法来看,挑战性学习的内容应是认知维度的过程序性知识及元认知过程维度的创造的交叉[11-13]。

因此,挑战性的题目不仅需要学生在综合知识应用能力的基础上,发挥主观能动性,主动查找资料,研究解决问题的办法,而且具有较强的应用性,又不能脱离教学内容太远。

因此,在“数字设计FPGA应用”课程的最后一个实验中,给出了一个“波特率可配置的异步串口设计及通信实验”,对于大学2年级下学期或3年级的学生,这个实验都具有足够的挑战性。

2 异步串行通信设计及通信实验教学设计

在进行异步串行通信设计及通信实验之前,学生已经完成了多数表决器的组合逻辑实验,序列发生器时序逻辑实验,流水灯及数码管动态显示综合实验及电子秒表实验,已经具备了一定的基础。其中,学生在做电子秒表实验时已经完成了按键消抖模块并生成了IP核,已经实现了数码管动态显示的IP核。

在给出挑战性实验题目之前,需要给学生引路,深入讲解串行通信的基本原理。

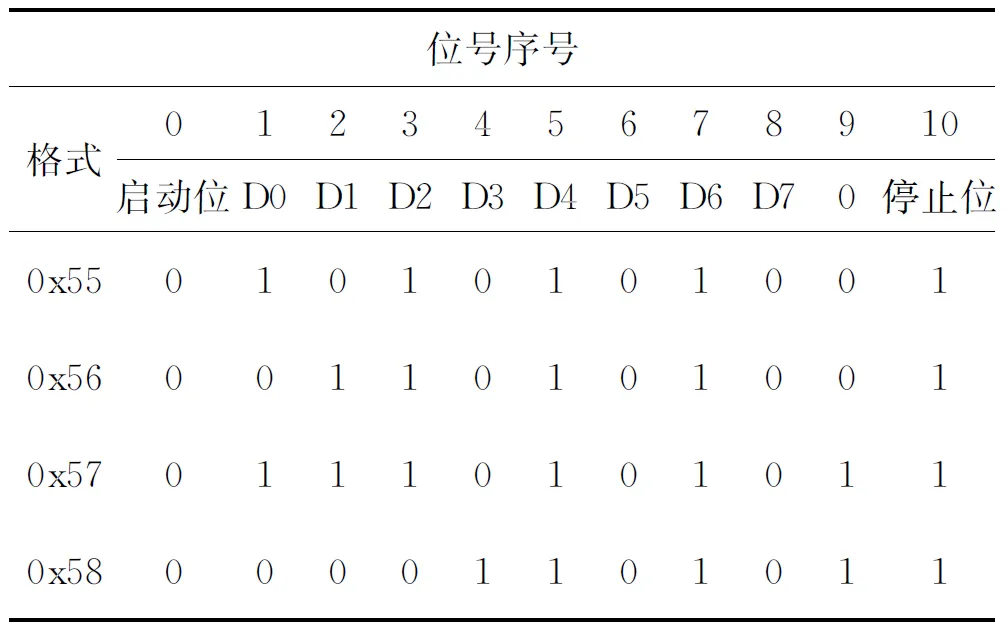

UART作为异步串口通信协议的一种,工作原理是将数据的每个字符一位接一位地传输。在向学生深入解释波特率及比特率的概念及起始位、数据位、奇偶校验位及停止位的概念后,给出表1举例说明有效的数据传输格式。

表1 有效数据传输格式示例

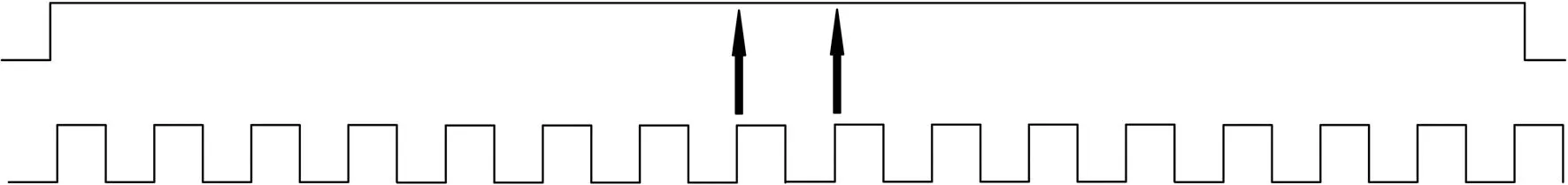

串行通信的一个重要问题就是发送方和接收方并不是在同一个时钟的作用下工作,因此非常重要的地方就是如何实现数据的安全传输。安全传输的关键就是在接收时采用数倍于波特率的频率实现在第一个数据位的中间点采样,如图1所示。

图1使用16倍比特率在数据位的中间点采样

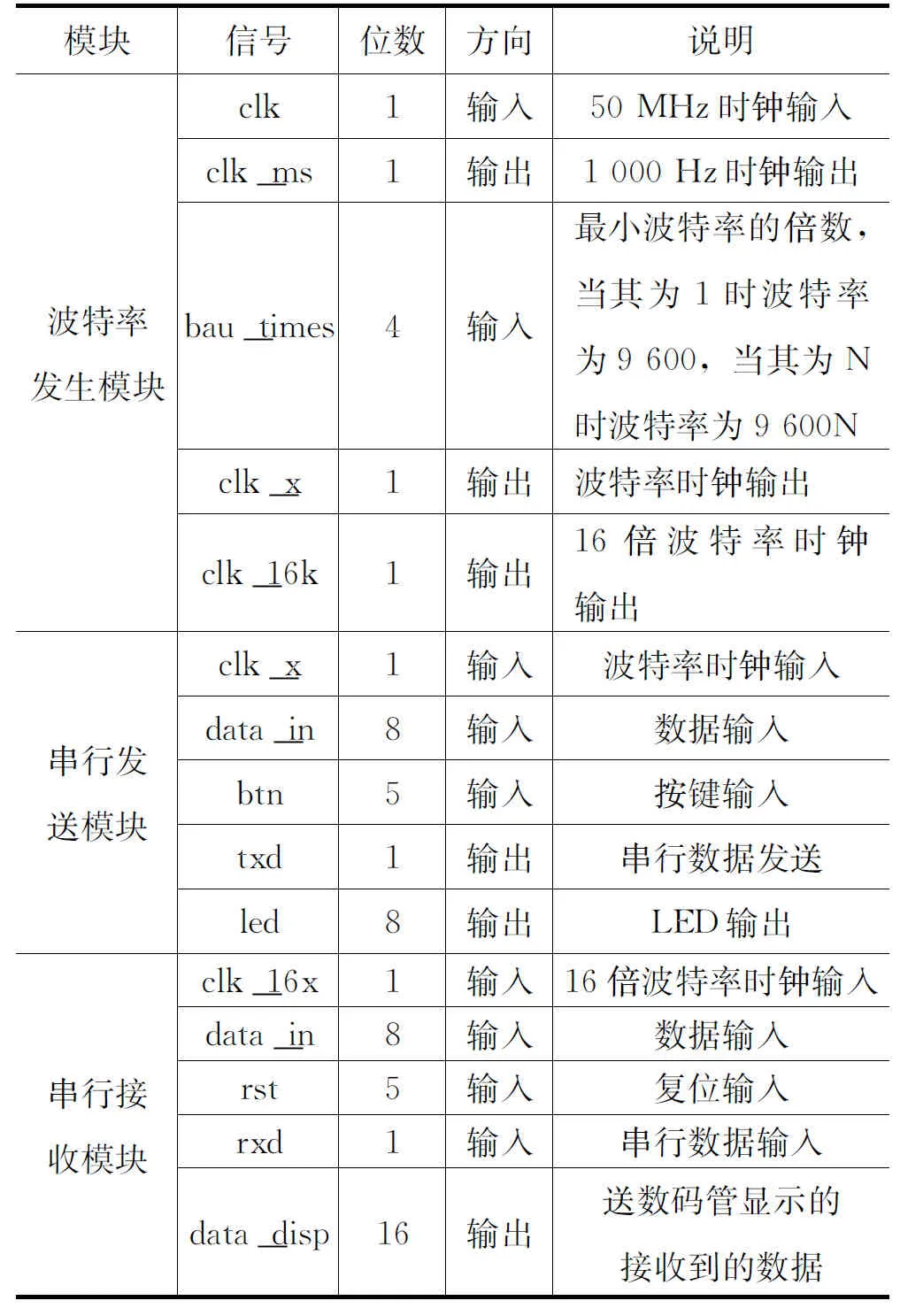

在讲解了串行通信的基本原理和注意事项之后,仍需要进一步地引导学生,可以给出一个已经完成的波特率发生模块及串行发送模块和接收模块的接口定义,而不去实现。这些模块的接口定义如表2所示。

表2 三个主要模块的定义

在这个基础上,将引导学生进行设计,波特率发生模块相对比较简单,对于串行发送模块和接收模块要求先画出状态转移图,再进行HDL代码实现。最后实现顶层模块的设计。

通过在实验课及教学班交流群的答疑和指导,有80%的学生在规定的时间内完成了挑战任务。

3 学生设计中的问题

在挑战式的实验设计过程中,学生的问题明显比验证性实验的多,主要集中在以下4个方面。

1)波特率生成模块实现不正确。

对时钟的分频是从流水灯实验就开始的,对于波特率生成模块只是修改了几个参数而已。因此出现问题的概率比较低,对于有问题的学生,可以让他们多参考已经实现的流水灯实验分频部分代码,对还解决不了的再单独指导解决。

2)IP核调用问题。

这类问题出现比较多,对于IP核的使用学生仍不够熟练,例如设计中需要显示串口接收到的数据,要调用已经实现的IP核时,因为问题比较多,就在课堂上又统一进行了讲解和举例。

3)串口数据发送不出去。

发送模块相对比较简单,数据发送不出去的情况种类比较多,需要分析学生设计的状态转移图,但除非非常容易发现学生代码的明显错误,不建议帮助学生一句一句地分析代码,因为这样就起不到挑战的作用。引导学生通过LED指示灯进行调试,以及编写仿真代码进行仿真。

4)接收不到串口数据或接收错误。

串口数据接收需要用16倍的波特率频率进行处理,这是最难的一部分,如果状态转移图是正确的,得不到结果的原因非常多,如果一个一个地去解决,学生将得不到锻炼。因此教师应鼓励学生自己解决,并引导学生新建一个工程单独调试串口接收程序。

通过教师和助教的引导,尤其是学生自己的努力,大部分问题得到了解决,大部分学生在规定的时间内完成或部分完成了实验要求。学生具备了使用Verilog HDL语言开发FPGA的综合应用项目的能力,对硬件端口的理解也得到了本质上的提升。

4 设计及实现示例

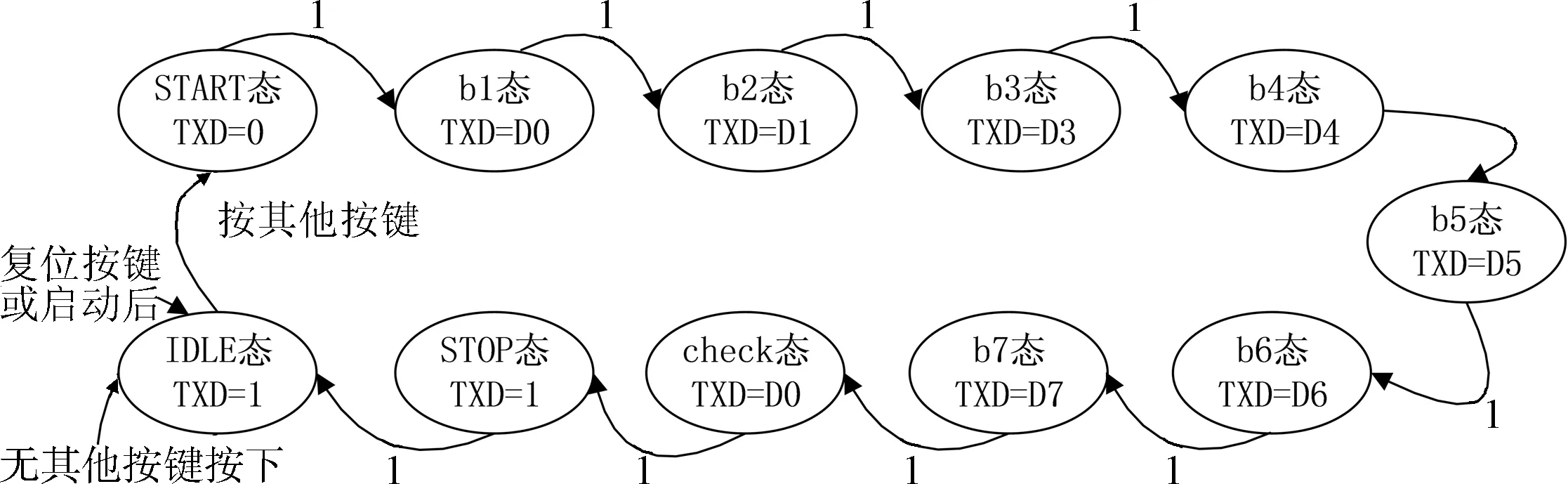

状态转移图的设计非常重要,但是并非唯一。以下是学生设计的串口发送和接收的状态转移图,都是正确的设计。

1)串口发送模块的状态图设计示例。

如图2所示,系统启动后进入空闲态IDLE,若按了复位按键也进入IDLE状态。如果有任何的其他按键按下,则开始发送数据,发送的数据值为拨码开关设置的8位数值,在时钟的有效边沿进入START状态开始发送起始位。

图2 串口发送模块状态图示例

在START状态下发送0,在下一个时钟进入状态b1,发送数据的最低位D0。之后在时钟的作用下依次发送D1~D7。接着进入check态发送校验位,校验位应为D0~D7的异或。之后进入STOP态发送1,然后回到空闲态。

2)串口接收模块的状态图设计示例。

如图3所示,接收程序简化状态图将状态划分为4个主要的状态。系统启动后进入空闲态IDLE,如果捕捉到了RXD信号的下降沿,开始接收数据启动计数。因为这里是启动信号0的开始,所以延后24个时钟,24=16+8,就大约到了数据位0的中间,在这个时间点上才转换到接收数据态ONE。

在接收数据态ONE,每隔16个时钟,就采集一次数据,分别存放到一个8位的寄存器data_out的对应位。在第136个时钟之后的16个时钟周期内,处于检查校验的状态TWO,判断校验是否有误,如果有误就置位校验出错信号,如果无误则置位数据准备好信号。

之后进入STOP状态,等待时钟计数到168,清时钟计数回到IDLE态继续检测串行输入RXD信号的到来。

最终的设计实现,很多学生使用了在计算机上运行的串口调试助手软件。

如图4所示,下载到实验板后,按键5次后电脑上运行的串口调试助手显示接收了5个A3,按串口调试助手“手动发送”按键,实验板如实地接收到并显示b5。

5 结束语

电子科技大学自动化工程学院开设了多年“数字设计FPGA应用”课程,文中介绍的挑战性实验设计是在对挑战性学习研究及多年教学经验积累的基础上形成的,并通过在多次教学实践的改进中完善的,目前取得了比较好的效果,具有一定的参考价值。