基于FPGA实现IPSec的优化研究∗

刘路遥 刘 进 周 勋 袁 涛

(武汉船舶通信研究所 武汉 430200)

1 引言

随着国际互联网的高速发展,网络应用也在不断的演变。利用互联网技术,大大提升了全球信息交流的速度,充分体现了互联网的开放性带给全世界的益处。但正是这种开放性的存在,导致互联网中潜藏着越来越大的风险,一旦有局域网接入互联网,那么局域网中用户的信息很有可能被泄露,被局域网外的用户知悉、篡改、假冒等。同时,互联网应对黑客攻击等安全方面显得十分的乏力。所以高速发展的网络使得网络安全问题愈发严峻,在面对安全威胁时,迫切需要一种行之有效的解决方法。

于是互联网工程任务组IETF(Internet Engi⁃neering Task Force)提出了IP安全(IPSecurity)体系结构,简称IPSec,目的是通过采取加密措施保护用户之间的IP通信。IPSec技术的出现大大提高了互联网环境中的信息在网络中传输的安全性。IPSec技术被用于IP层,以IP数据包为处理对象,提供数据完整性验证、数据源身份认证、抗重放攻击等各种安全性服务,能够明显降低出现安全威胁。

本论文介绍了在硬件上实现IPSec的结构体系和封包解包处理器及其工作流程;详细介绍了基于FPGA的AES加密算法和SHA-256算法实现,针对两种算法进行了硬件实现的优化设计。本文中的优化设计是在Xilinx公司的Virtex-4芯片上进行仿真。

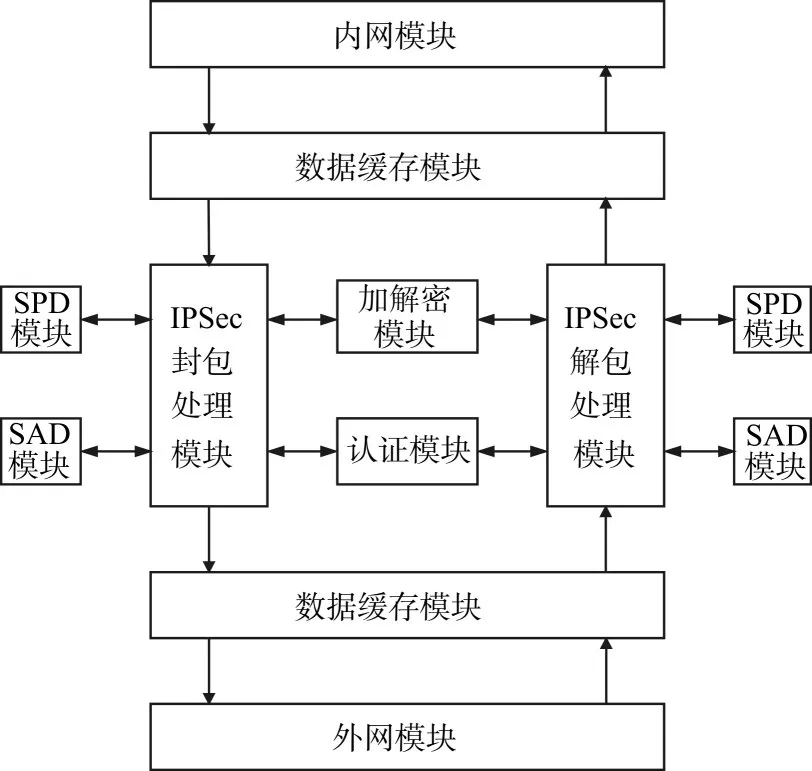

2 IPSec的硬件体系结构

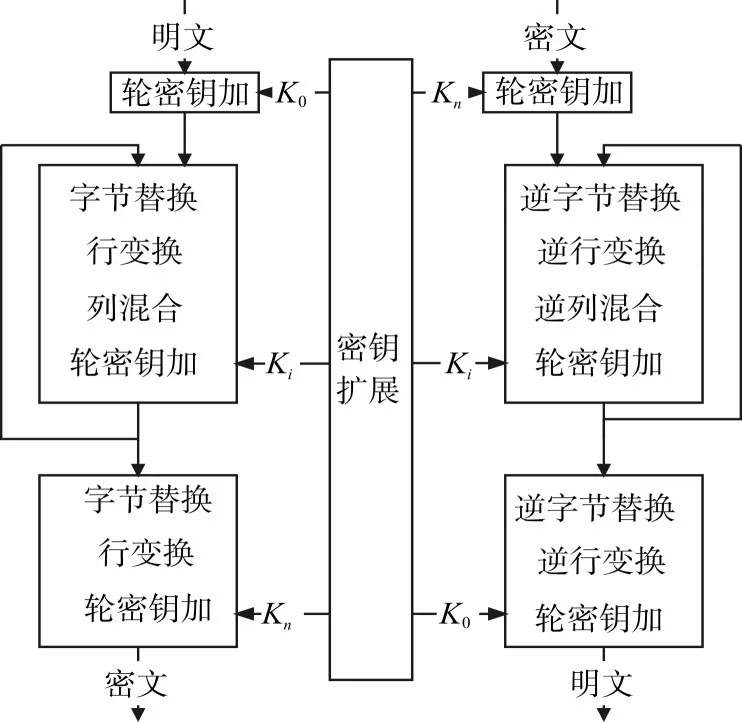

IPSec的硬件体系结构如图1所示。包含内网模块、数据缓存模块、IPSec封包处理模块、IPsec解包处理模块、加解密模块、认证模块、安全关联数据库(SAD)模块和安全策略数据库(SPD)模块。

图1 IPSec硬件体系结构

以IPSec协议的外出处理为例,内网模块在接收到一帧数据之后,检查该帧是否有效,若该帧数据有效则解封掉数据帧的头尾,变成网络IP报文,将IP报文发送至数据缓存模块。然后经过IPSec封包处理模块,将封包后的数据发送到数据缓存模块,再发送到外网模块,外网模块将此数据组成数据帧并以数据流的形式发送到下一层。

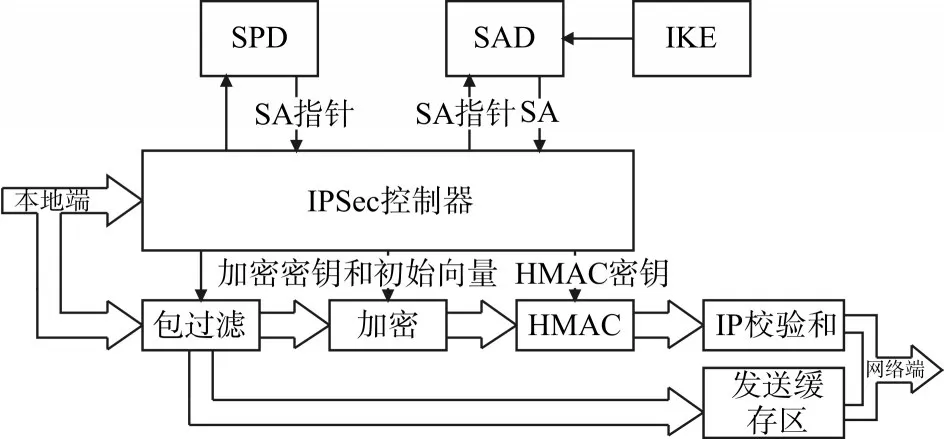

2.1 IPSec封包协处理器

IPSec的封包协处理器如图2所示。当收到的数据流进入IPSec封包协处理器时,IP头会进入IP⁃Sec控制器,通过检索安全策略数据库SPD得到安全关联(SA)指针,然后在安全关联数据库SAD中获取相应的安全关联SA,若是在SAD中没有相应的SA,则由密钥协商协议(IKE)生成相应的SA。在包过滤模块中根据SA将数据包丢弃或者直接发送到发送缓冲区或者应用IPSec处理。需要经过IPSec处理的数据先经过AES进行加密,然后经过HMAC模块进行处理,再重新计算数据包的IP校验和,最后才能发送出去。

图2 IPSec封包协处理器

2.2 IPSec解包协处理器

IPSec解包协处理器如图3所示。接收到的数据包经过IP校验,如果错误则直接将此包丢弃。通过IP校验的数据包会根据数据包中的下一协议是否为安全封装载荷(ESP)协议或者认证头(AH)协议而做出相应的处理,如果不是,则根据其他地址查找SPD,如果有相应的策略则丢弃,否则绕过。若下一个协议是ESP或者AH,则使用三元组在SAD中查找SA并对数据进行IPSec处理。然后通过将SAD和SPD相连的指针进行匹配而找到使用的SPD,验证是否与采取的IPSec处理相符,如果相符则发送到上层进行处理,若是不符则丢弃。

图3 IPSec解包协处理器

3 AES和SHA-256的优化

在IPSec体系结构中,用到的加解密算法通常是3DES或者AES,用到的哈希算法通常是SHA-1、SHA-2系列。由于SHA-1已被攻破,存在安全隐患,所以本试验采用的是更为安全的SHA-256。本论文将详述AES算法和SHA-256算法。

本论文是在Xilinx的Virtex-4系列FPGA上进行实验。此芯片运行速度快,有着并行运算的优势,在每个时钟周期内完成更多的任务,有处理复杂功能的能力。

3.1 AES的优化

AES算法是于2001年由美国国家标准技术协会发布的高级加密标准。作为一个对称分组密码算法,其分组长度可以为128位、192位和256位。本论文介绍的是分组长度为128位的,密钥长度为256位的算法。

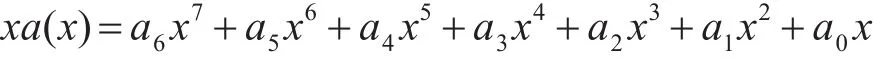

AES算法加密过程如图4所示,加密包括字节替换、行移位、列混合和轮密钥加四个过程,其中列混合是运算中最复杂的。解密过程与加密过程相近,包括逆字节替换、逆行移位、逆列混合和轮密钥加。

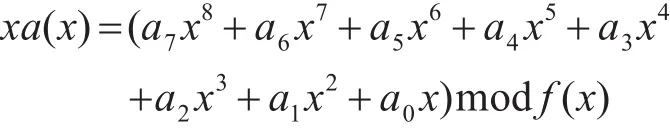

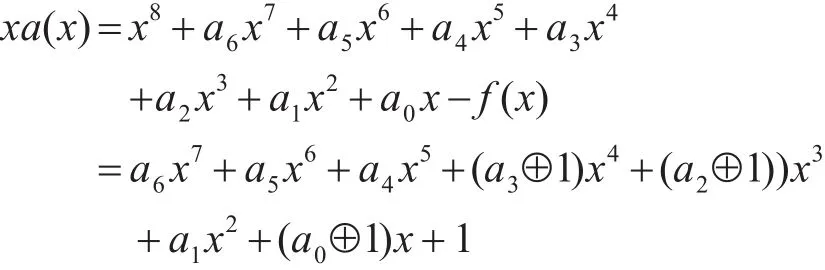

3.1.1 多项式模运算

若a∈GF(28),则a可以表示为

那么:

图4 AES加解密过程

由于:f(x)=x8+x4+x3+x+1

当a7=0时有:

当a7=1时有:

所以对于任意给定的输入数据a(7:0),当执行GF(28)上的x乘法运算时首先将a(7:0)左移一位,得到数据(a(6:0),0),其次判断数据最高位的值,所以输出的数据为

c(x)=xa(x)=(a6a5a4a3a2a1a00)+(000a7a70a7a7)

所以AES算法中GF(28)上的x乘法电路如图5所示。

图5 x乘法电路图

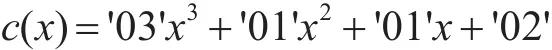

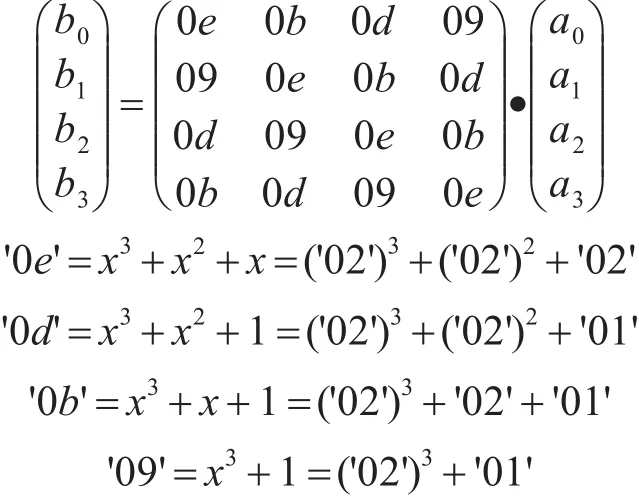

3.1.2 列混合与逆列混合运算

列混合是将状态阵列的每一列视为系数在GF(28)上,次数小于4的多项式,被同一个固定的多项式c(x)进行模x4+1乘法。AES的设计者所给出的c(x)为

列混合运算可以表示为GF(28)上的可逆线性变换:

通过上述的介绍可以将此运算改进为循环移位和异或两种简单的逻辑运算,更加适合硬件电路的设计,不需要进行多项式的模乘和模除这种复杂的运算,可以大大提高运算的效率。

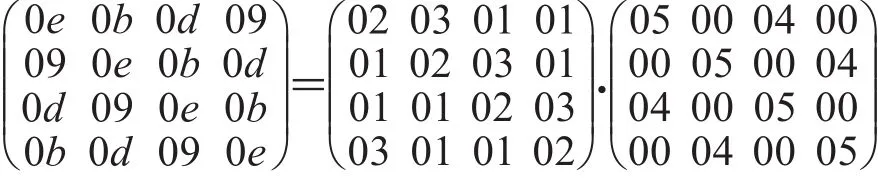

AES解密过程中的逆列混合运算与加密过程中的列混合运算不同:

由上式可知逆列混合运算的复杂度远远大于列混合运算,可以通过下列方法优化其逆列混合运算过程:

逆列混合运算可以变换成:

'05','04'的计算量明显要比变换之前的计算量小,而且变换之后逆列混合运算可以调用列混合运算中的模块,减少AES算法对资源的占用,优化前后的资源如表1所示。

表1 AES在Virtex-4上的综合报告

吞吐率=(分组长度*时钟频率)/分组运算占用时钟周期数。此算法分组长度为128bit,分组运算占用时钟周期数为16个时钟周期。

从表1中可以看到,在经过优化后,运算频率有所提高,吞吐率有了提升,面积占用有所减小,可见本论文中提到的方法有一定的效果。

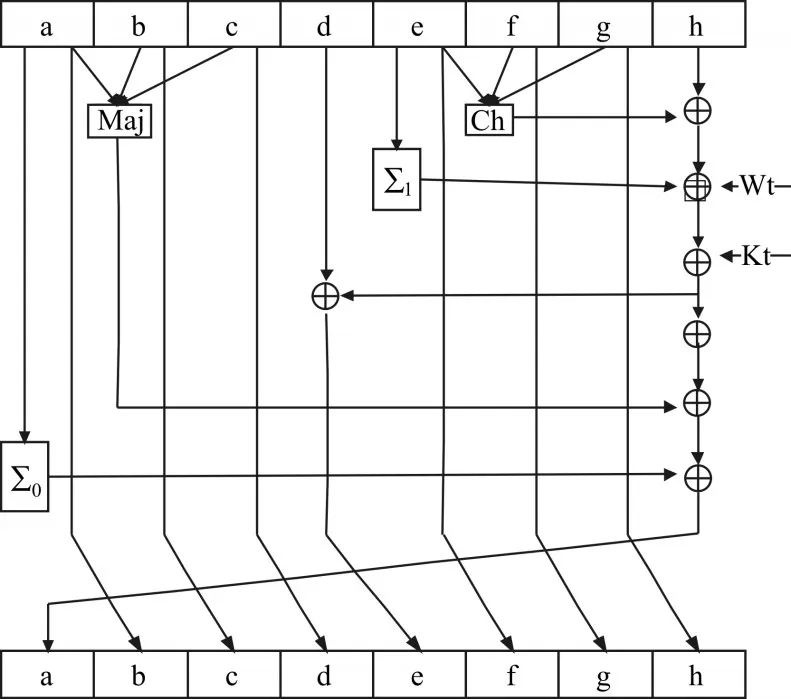

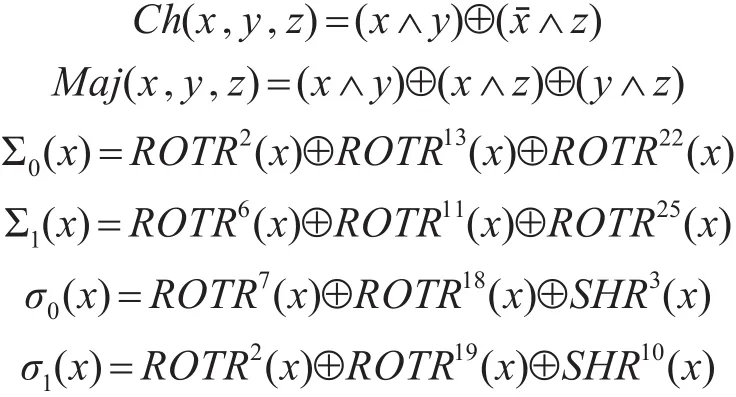

3.2 SHA-256的优化

SHA-256算法是指将长度不大于264bit的信息通过64次循环运算计算出256位的哈希值。哈希运算单元每次处理512位信息。SHA-256单次循环步骤如图6所示。

图6 SHA-256单步运算

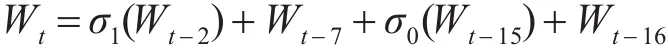

其中前16个Wt是最初的512bit消息块分成的16个32bit数据,后48个Wt由上面的公式计算所得。

SHA-256算法由64个图6中的单步运算组成,每一轮 a,b,c,d,e,f,g,h 都是当前轮的输入,也是上一轮的输出。每一轮运算里面求a的关键路径最长,也是延时最大的,可以通过流水的方式减少其最长路径。

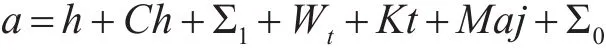

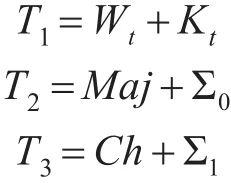

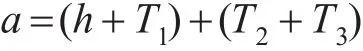

可以通过增加寄存器,减少关键路径的长度,将a的计算分解成两个时钟完成,第一个时钟计算:

第二个时钟计算:

然后采用流水的方式在计算a的同时计算下一轮的T1,T2,T3,通过这种并行计算使整个算法的时钟只增加一个,但是减少了关键路径的长度,提高了运算速度。

采用本论文中提到的方法前后资源占用、最大时钟频率和吞吐率如表2所示。

表2 SHA-256在Virtex-4上的综合报告

从表2可以看到,与文献[8],文献[9]相比,本论文优化后的最大时钟频率有了一定的提高,资源占用面积也减小了,在数据最大吞吐率上面有了明显的提高,在提升算法性能上有着显著的效果。

4 结语

本论文通过分析IPSec硬件实现的结构体系,详细介绍了基于此安全协议上的封包和解包流程,针对其中对称算法AES和哈希算法SHA-256的运算过程进行了详细的分析。并对这两个算法进行了硬件实现和优化设计,在频率、面积上有了一定的优化,使得数据吞吐率和优化之前有了明显的提高,提升了两种算法的性能。

[1]Atkinson R.Kent S.Security Architecture for the Internet Protocol[S].RFC2401,1998.

[2]田春歧,王立明,蔡勉.IPSec VPN的研究和分析[J].计算机工程与应用,2004,40(4):163-166.

[3]刘航.一种用于IPSec协议的AES算法可重配置硬件实现[J].小型微型计算机系统,2005.12(26):2083-2085.

[4] Wu Jianwu.Implementation of Virtual Private Network based on IPSec Protocol[C]//IEEE Future Computer and Communication,2009:138-141.

[5]A J.Elbirt.Accelerated AES implementations via general⁃ized instruction set extensions[J].Journal of Computer Se⁃curity,2008,16(3):265-288.

[6]梁旭,凌朝东,张丽红.基于FPGA的AES算法的实现[J].通信技术,2011,44(12):111-113.

[7]陈华锋.高速SHA-256算法硬件实现[J].浙江大学学报,2009,11(6):675-678.

[8]刘钰力.基于FPGA的SHA256高效数字加密系统[D].兰州:兰州大学,2011.

[9]汤煜,翁秀玲,王云峰.SHA_256哈希运算单元的硬件优化实现[J].中国集成电路,2016,25(5):26-31.

[10]何润民.单向Hash函数SHA-256的研究与改进[J].信息技术,2013,14(8):22-25.

[11]葛辉.一种256位hash函数算法[J].大众科技,2005,6(5):107-108.

[12]佟玉伟,陆浪如,李明等.基于FPGA先进加密算法AES的并行实现[J].交通信息与安全,2002,20(6):20-22.

[13]沈启峰,黄士坦,杨靓.基于FPGA先进加密算法AES的高速实现[J].西安理工大学学报,2006,22(2):203-206.