基于FPGA支持IEC61850通讯标准的自定义MAC的实现

(南瑞集团公司(国网电力科学研究院),南京 210003)

以太网以其结构简单、成本低廉、传输速率高和带宽易拓展的特点已经应用在工业领域当中,未来工业以太网将在工业自动化控制系统的设备之间互联和信息集成中发挥不可替代的作用[1]。

同时,IEC61850已经成功应用在智能变电站中,为变电站能够完备实现信息标准化和设备之间的互操作提供了通信标准。近年来,应国家电网的发展要求,国内传统水电厂向智能水电厂方向全面发展以适应智能电网的要求将是一个必然的趋势和全新的目标[2]。IEC61850 ED2已经将其应用领域拓展到水电厂中,成为水电厂智能化建设的通信标准。实现IEC61850通信的基础是以太网[3],而以太网技术主要集中在物理层(PHY)和介质访问控制层(MAC)的实现上[4]。MAC定义了数据帧在介质上的传输,线路控制、差错校验和流量控制等功能也由MAC实现,是以太网控制器的核心。

FPGA即现场可编程门列阵,作为专用集成电路(ASIC)领域中的一种半定制电路,既解决了定制电路的不足又克服了原有的可编程器件门电路有限的缺点。FPGA具有强大的并行计算能力,可以在一个时钟周期内完成更多的操作任务,且不使用任何操作系统,稳定性能得以提高,能够满足GOOSE/ SV等实时性和可靠性要求高的报文传输。

同时,FPGA具有丰富的硬件资源,与传统的芯片相比,FPGA可通过调用内置的IP核大大缩短设计周期。所以,对基于FPGA支持IEC61850通讯标准的工业以太网MAC的研究显得尤为重要。

1 支持IEC61850通讯标准以太网

普通以太网最初设计是用于商业用途而非工业过程领域,强调的是网络节点之间的平衡性和带宽的共享,采用的介质访问控制方法是CSMA/CD,因此标准的共享以太网存在延时不确定的问题。

标准的以太网不限定节点访问网络的时刻,即节点访问网络是事件驱动而非时间驱动,因此多点共享式以太网中,数据冲突不可避免;同时标准的以太网不支持报文或节点优先级的设定,发生冲突后所有节点都采用相同的退避机制,且时间随机。所以普通以太网难以满足IEC61850通讯实时性的要求。

工业过程控制领域中通常不会有持续的大流量的数据传输,常规以太网的10/100 Mb/s的带宽是足够的。信息的端到端时延主要包括排队时延、发送时延和传输时延3个因素,所以应从避免数据冲突和保证实时数据优先传输入手。全双工通信中信号可以同时双向传送,网络上的数据冲突彻底避免,所以本文的MAC基于全双工的基础上进行设计。

2 总体设计方案

本文在传统以太网MAC设计的基础上对其进行了改进与优化,采用全双工模式设计,通过遍历算法完成对MAC地址的过滤,模块设计通过Verilog行为级描述语言及调用IP核相结合,设计更加精简同时避免了传播过程中数据冲突等问题,使其更好地适应IEC61850通讯的特点。

基于IEC61850的MAC控制器由BUS总线接口模块、时钟管理模块、EMAC模块、中断模块、MII/ MDIO接口模块5个部分组成,如图1所示。

BUS模块负责总线接口控制以及16位至32位数据总线转换,将接收到的数据帧保存到储存器中,同时从储存器中载入需要通过以太网接口传输的数据,用于实现更高层次的以太网协议。

图1 以太网MAC控制器的主要组成部分Fig.1 Components of Ethernet MAC controller

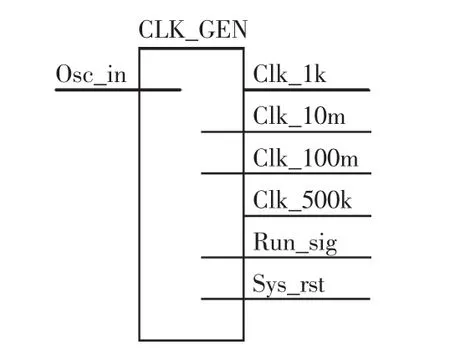

时钟模块用于产生整个系统所需的时钟信号及复位信号等。系统输入25 MHz的主时钟信号,通过PLL分频后生成500 K,10 M,100 M等时钟信号,FPGA内部各单元根据设计使用不同的时钟单元。CLK_GEN模块如图2所示。

图2 CLK_GEN模块Fig.2 CLK_GEN module

3 EMAC模块

本文设计了4个相同的EMAC模块,每个EMAC模块下又包含了数据缓存模块、数据接收模块和数据发送模块。

3.1 数据缓存模块

数据缓存模块用于发送和接收数据的缓冲,以使主机的传输速度与本模块相匹配。发送数据时,上层主机先将待发送的数据写入发送数据缓冲区,然后由发送模块将数据读出。

由于FPGA内部有丰富的块RAM资源,本文设计的数据缓存模块通过FPGA配置双端口RAM来实现,可支持2个端口读写操作的任何组合。大大简化了设计,节省了硬件资源,提高了工作效率[5]。

RAM模块设计调用IP核blk_mem_gen。IP核在嵌入式FPGA设计中,指的是已设计好的形式为逻辑单元且可用于重复设计的模块。IP核分为软核、硬核和固核。软核是由VHDL等硬件语言描述的功能块,设计周期短、投入少,灵活性和适应性方面较好。硬核则是经过完全的布线布局的网表形式提供,较软核相比,其能更好地适应产品设计。除了软核和硬核,固核也是IP核主流的形式之一,其是介于软核和硬核之间,在FPGA设计中可以看成带有布局规划的软核。

由于IP core通常已通过设计验证,因此在设计中直接调用IP核进行设计开发,大大缩短了设计周期。

3.2 数据发送模块

发送模块从发送数据缓冲区中获得要发送的数据并添加MAC层的报头和起始分隔符,再将其传输给外部PHY芯片。发送模块主要包括数据发送状态机模块、计数器模块和CRC校验模块。

图3 发送状态机转移图Fig.3 Transfer state machine

本文设计的发送状态机共有7个状态:

IDLE 空闲状态,系统复位后,此时MAC进入就绪状态,可以发送数据帧,当寄存器的发送使能位为1,且数据有效位为1时,则转入WAIT状态;

WAIT 等待状态,等待一个帧间隔计时时间,当计数器计数与帧间隔时间相等时, 转入SEND_SFD状态;

SEND_SFD 帧起始分隔符状态,该状态负责添加报文头和帧起始分隔符。当SFD计数达到7时,即SFD帧添加完毕,若此时传输数据有效则转入SEND_FPAME状态,进行数据帧的发送,否则意味着传输数据为空,进而转入SEND_ZERO状态;

SEND_FRAME 负责控制帧的有效数据的发送过程。在该状态可能发生以下几种情况:①帧太短,如果在上层的帧数据传送结束时,帧长度计数器仍小于60 B,则表明该帧是短帧则跳至SEND_ZERO,添加填充码;②帧长度超过 60 B则跳至SEND_CRC状态,添加CRC字段;

SEND_ZERO 发送模块发送填充字段,直到帧长度达到最小帧长度为止转入SEND_CRC状态;

SEND_CRC CRC校验码发送状态,待32位CRC校验码发送完毕后转至IPG状态;

IPG 帧间隔计时状态,当间隔时间到则转至空闲状态IDLE。

计数器模块又包含等待计数、传输计数、SFD计数、CRC计数和IPG计数等。计数器模块和发送状态机模块相互配合,共同完成数据帧的发送过程。

CRC校验模块采用CRC-32校验算法,在SEND_ CRC状态之前的SEND_FRAME或SEND_ZERO状态期间完成32位CRC校验值的生成,提高了传输效率。

3.3 数据接收模块

数据接收模块负责接收数据的整个过程,并判断接收到的数据帧是否受损,若受损则舍弃该报文。

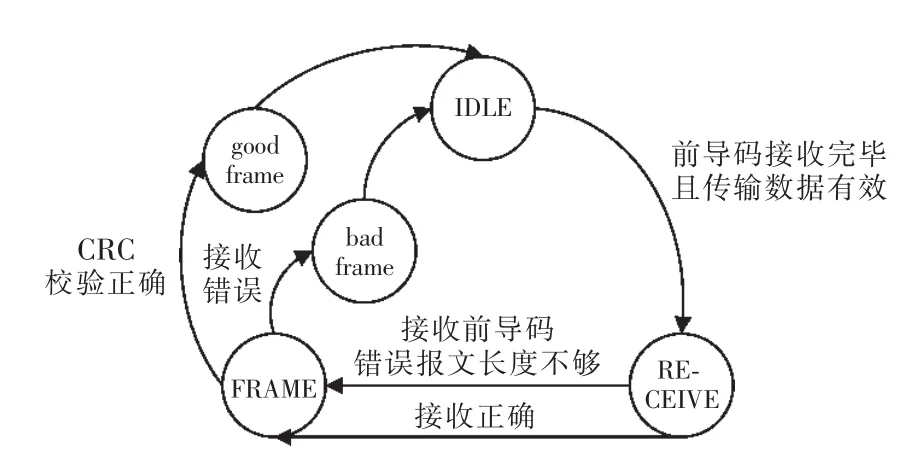

接收模块主要组成跟发送模块大致相同,主要包括数据接收状态机模块、计数器模块和CRC校验模块。数据接收状态机如图4所示,共有3个状态:

IDLE 空闲状态,系统复位后首先进入IDLE状态,完成数据的初始化设置。当检测到以太网帧的前导码接收完毕并且接收的数据有效时,进入RECEIVE状态;

RECEIVE 接收状态,当报文接收完毕、前导码接收出错或者报文长度不足则进入FRAME状态;

图4 接收状态机转移图Fig.4 Receive state machine

FRAME 当检测到错误报文时输出badframe,丢弃该报文并进入IDLE状态;当报文接收无误且CRC校验正确后输出goodframe,进入IDLE状态继续接收下一帧报文。

3.4 地址过滤模块

IEC61850通讯中,MMS通讯采用客户端/服务器模式,报文通过单播“一对一”发送,而GOOSE通讯为了提高报文的实时性,采用发布者/订阅者通信模式,通过组播的方式传输报文。为了防止接收到不需要的报文,因此加入了MAC地址组播过滤模块。预先在EMAC地址过滤寄存器中配置好相应的MAC地址,在报文接收过程中,通过遍历算法检测该报文的MAC地址是否已被订阅。通过对MAC地址组播过滤,使其既能一次将数据传送给多个订阅的IED(智能电子设备),又能保证不影响其他未订阅的IED的正常通讯。

4 MII/MDIO模块

本文采用了TI公司的DP83630SQ以太网PHY芯片,此芯片能适应10 M和100 M的以太网通讯速率,支持RMII接口(精简独立接口)。以太网MAC支持MII接口,在设计中Mii to Rmii模块采用了soft IP core在FPGA内部实现。

MDIO接口为数据管理输入输出接口,是一种简单的双线串行接口,主要实现MAC层和PHY层之间数据的传输控制和状态信息的管理。MDIO接口包括2根信号线MDC和MDIO。MAC层芯片通过MDIO接口访问PHY层芯片的寄存器,并通过这些寄存器完成对PHY层的控制和管理。MDC则为MDIO提供时钟信号。

5 验证与仿真

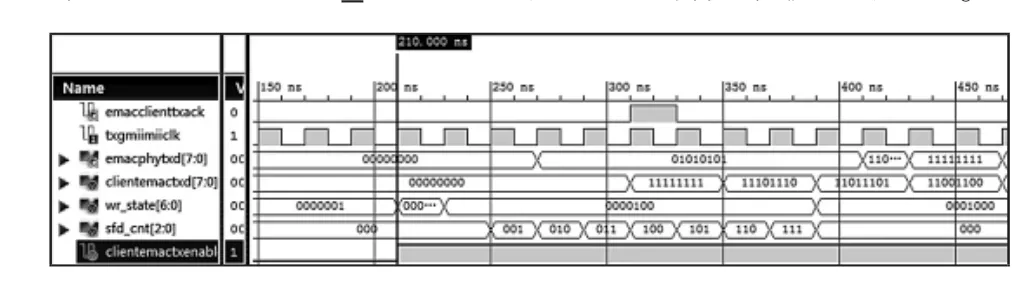

本文设计的MAC控制器采用XILINX Spartan6系列的FPGA实现,并在Modelsim上对MAC控制器进行了仿真验证。图5、图6为发送和接收状态仿真波形图。

从图5中可以看出传输使能信号为高电平时,在下个时钟上升沿,状态机从 WAIT状态进入SEND_SFD状态,开始发送前导码。当前导码发送完毕后进入SEND_FRAME状态进行数据帧的发送。

图5 发送模块波形图Fig.5 Send module waveform

从图6中可以看出当数据帧接收完毕时,接收数据有效信号为低电平,进入FRAME状态,进行CRC校验。CRC校验正确,且CRC计数器达到4时,校验完毕,输出goodframe,并进入IDLE状态。

图6 接收模块波形图Fig.6 Receive module waveform

6 结语

本文介绍了一种基于FPGA且支持IEC61850通讯标准的自定义MAC的设计方法,通过仿真验证能够有效的实现IEC61850报文MAC层的通讯,完善了IEC61850标准的在智能变电站中的应用以及为其在智能水电厂中的应用与发展起到了积极作用。

[1] XIONG Jian-qiao,XIONG Xiao-song.The research of CNC communication based on industrial Ethernet[J].Electrical Engineering and Control,2011,98:689-694.

[2] 冯汉夫,石爽,马琴,等.智能水电厂建设的思考[J].水电自动化与大坝监测,2010,34(6):1-5.

[3] 黄智宇.基于IEC61850的变电站网络通信及装置的研究[D].大连:大连理工大学,2008.

[4] 丁世勇,谭文文,李桂英.基于FPGA的以太网MAC控制器的设计与实现[J].电子设计工程,2011,19(21):163-165.

[5] 徐洪波,俞承芳.基于FPGA的以太网MAC子层协议设计实现[J].复旦学报,2004,43(1):50-52.