Tri-Designer:一种面向片内云架构的IC设计平台

陈 越,刘彦隆,张 刚

(太原理工大学信息工程学院,太原 030024)

0 引言

提高信息系统性能,摩尔定律通过提高工艺水平缩小器件尺寸,而云计算则是通过资源虚拟化扩大体系规模[1],片内云将二者结合在一起[2]。片内云是基于虚拟化资源的片内并行网络计算,片内网络、虚拟化资源和并行处理是片内云架构的3个基本要素[3]。传统的总线都是点对点总线,难以组成片内网络。以太网的特征是一个独立的传输通道的主动性功能只能是发送数据,基于此特征,本项目抽象出只写总线WoB(Write-only Bus),并将其拓展成片内网络[4]。然后将芯片内部电路连接的IP核封装成消息连接的构件,挂载到片内WoB网络,成为片内虚拟化资源[5];进一步引入流程引擎[6],管理调度片上虚拟资源的并行处理,形成片内云架构并用于集成电路IC(Integrated Circuit)设计。该项目得到2011年国家科技型中小企业创新基金资助并获得2014年山西省技术发明二等奖,其中关键技术“ASIC的片内云模型”发明专利已经获得授权[7]。

1987年,中国工程院许居衍院士提出了半导体产品总是围绕“通用”与“专用”特征循环、每10年波动一次的“半导体产品特征循环”规律[8]。此后又提出主流半导体产品将进入用户可重构系统级芯片阶段,其特征是仅通过对“毛坯芯片”的配置编程就可得到用户自定义的芯片,从而引导半导体产业结构演变,促进不做芯片设计而专事芯片应用创新的无设计商业模式的兴起[9]。本文认为,许院士提出的可重构系统级芯片,是一种“领域通用(Domain General)”的集成电路产品,记作DGIC。DGIC采用本项目的片内云解决方案,一方面具有ASIC(Application Specific Integrated Circuit,专用集成电路)的语法元素的可定制性,同时又可以像通用CPU那样重构语义流程,是许氏循环“通用-专用”转换过程的一个中间环节。

传统IC开发平台设计DGIC芯片多有不便,本文研制开发了一种面向片内云架构的IC设计平台Tri-Designer,专门用于领域通用的DGIC芯片设计,以遗传算法为具体应用领域,设计开发了一款片内云架构的DGIC芯片,加速比超过了104,验证了开发平台Tri-Designer的有效性。

1 Tri-Designer框架

Tri-Designer开发平台将一个DGIC设计过程划分成“概念建模”,“逻辑建模”和“物理建摸”3个阶段。现有各种IC设计平台如ISE或Vivado都可以胜任物理建摸平台的任务,所不同的是,Tri-Designer逻辑建模平台的主要目标是对IC内部资源虚拟化,将电路互连的IP核封装成消息互连的构件。构件是一个功能电路模块,定义一组接口且只能以消息的方式通过接口进行访问。构件是片内虚拟化资源,拥有多个引脚的IP核封装成构件后释放出大量布线资源,可以用来扩展片内WoB总线的宽度,提升片内网络的传输带宽。

Tri-Designer概念建模相当于软件开发的UML阶段,是用接近自然语言的方式描述一个应用,特别赋予Tri-Designer概念建模平台一些特殊属性以便适应DGIC的片内云架构,其中包括CTGS和BDE两个部分。CTGS是概念树生成系统(Concept Tree Generation System),帮助设计人员定义一个应用的外延和内涵,并表示成集合隶属关系的概念树。概念树的叶子结点是具体的业务用例场景,它是以业务步骤为节点的业务流程,计入相应的业务文档。业务文档编辑器(Business Document Editor)BDE支持设计人员定义业务步骤,编辑业务流程,生成业务文档。

业务文档描述的业务用例场景,或其中的一个业务步骤,可以映射为DGIC芯片的一个基本构件BC(Basic Component)。Tri-Designer逻辑建模主要功能是将一个基本构件BC分解成以基本构件BC和原子构件AC(Atom Component)为步骤的语义流程,其中AC是无需继续分解的构件。本文定义了一种应用层语言LL7(Language Level 7),逻辑建模将DGIC芯片的语义流程自动转换成LL7描述,经编译生成相应的FPGA代码。

对于简单的或稳定不变的语义,DGIC流程引擎可以是状态机。另外定义了一种定序器流程引擎,用来驱动执行DGIC中复杂的或可由用户重构的语义。

2 概念建模

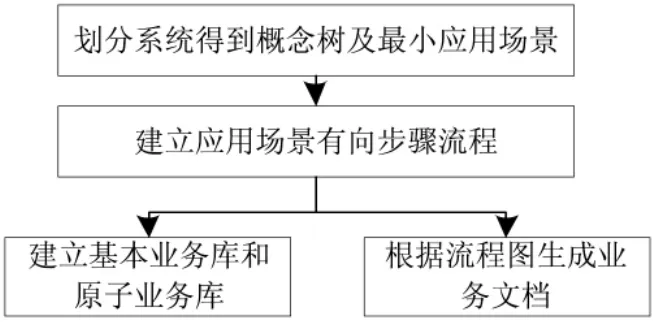

概念建模主要功能如图1所示。

图1 概念建模

图2 树型菜单

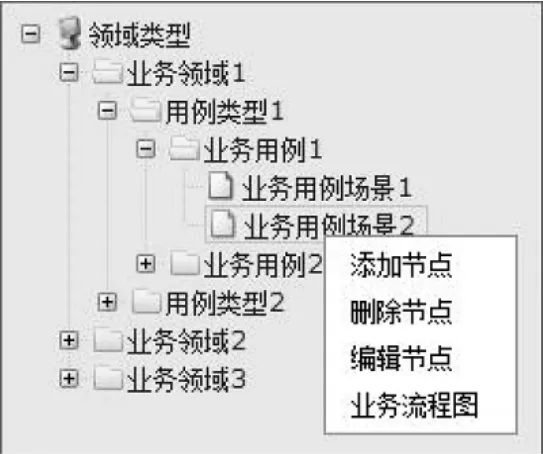

CTGS从概念上将一个应用系统(外延)多层次地细化分解成若干子系统(内涵)的集合,自动生成一个层数可控的树型菜单,用来描述应用系统外延与内涵的隶属关系,如图2所示,叶子节点是系统划分的最小粒度,即业务用例场景。

该树型菜单基于JQuery中的zTree插件开发实现,其节点数据存储于MySQL数据库中,通过设置nodeId和parentId约束了节点间的隶属关系。右键菜单通过Javascript实现了节点数据的动态添加、删除和编辑,并利用AJAX技术与服务器异步交互,达到节点数据局部刷新的效果。

zTree加载数据库数据的部分js代码如下:

概念树的叶子结点是最小粒度概念,即业务用例场景。业务用例场景作为概念的外延,其内涵是业务步骤的集合。与其他概念节点的重要区别是,业务步骤之间定义了“顺序”和“选择”两种有向关系,形成业务用例场景的语义流程。BDE针对务用例场景建立业务步骤流程图,以有向的业务步骤关系确定业务步骤的语义流程,描述业务用例场景。

BDE通过矢量图形库(Raphael.js)创建业务步骤,以矩形框代表步骤间的“顺序”关系,以菱形框代表步骤间的“选择”关系,通过右键菜单为业务步骤添加业务描述、分配执行角色,从而建立业务步骤的有向流程图,如图3所示。

图3 业务步骤流程图

BDE还建立应用系统的业务库,每个业务步骤可通过右键操作保存到基本业务库或原子业务库中,业务步骤语义流程和业务库有利于系统业务的更新和重构。

根据业务流程图,BDE利用Java的文件操作技术生成业务文档(word文档),以备查找修改。由步骤流程图通过createDoc函数可以生成业务文档。该函数依次读取每个业务步骤,将业务描述逐一写入一个word文件中,写入主要代码如下:

3 逻辑建模

DGIC与一种应用层语言LL7等价,就像通用CPU与一种机器语言等价。其中DGIC的流程引擎LL7.PI(Part Independent of any application) 相当于CPU机器语言的控制器指令集,可用于任何应用领域;DGIC 的领域指令集 LL7.PS(Part of a Specific)相当于CPU机器语言的运算器指令集。通用CPU的控制器通过总线物理地连接运算器,但是DGIC的LL7.PI通过片内网络虚拟地连接LL7.PS。逻辑建模的主要任务是将业务文档的用例场景映射到DGIC芯片中,为每一个业务步骤建立一个以DGIC基本构件为步骤的语义流程,自动地生成语义流程的LL7描述并编译链接生成可执行代码,如图4所示。

图4 逻辑建模

3.1 业务步骤映射为语义流程

概念建模输出的最小粒度节点是业务步骤,需要映射成为DGIC芯片的一个基本构件BC。在DGIC芯片内部,一个基本构件BC对应着一个语义流程,其步骤代表一个DGIC机器操作,该操作被封装为一个基本构件或一个原子构件,如图5所示。

图5 一个BC的步骤序列

逻辑建模定义步骤的类型和属性,标记步骤间的前后件关系,即“顺序”或“选择”,然后自动输出语义流程的LL7描述。原子业务的逻辑模型和组成它的操作步骤以“一对多”的关系存储于数据库中,通过Hibernate框架方便操作流程的创建以及重构。

逻辑建模通过创建或检索为每个操作步骤绑定一个构件,该构件映射为LL7的语法元素,LL7语义流程的控制包括确立“顺序”或“选择”关系、选择前后件并创建符号地址等。图6是把操作步骤序列自动转换成LL7语义流程的过程。

图6 生成LL7算法

3.2 DGIC引擎LL7.PI

DGIC引擎主要部件是定序器,实现应用层语言的控制LL7.PI,它由构件队列、构件指针、构件译码器和结果寄存器组成,如图7所示。

图7 DGIC定序器

构件指针指向构件指令队列中的每个单元,并可在构件指令队列上移动,引擎根据其指向决定即将要执行的构件指令。构件译码器解析构件指针所指向的构件指令,将解析结果封装为消息并通过消息总线传递给构件实体,实现构件功能。结果寄存器用来存储构件实体的执行结果,其值可影响构件指针的下一步动作以及引擎的状态。除了流程控制操作之外,LL7.PI还包括一些其他的公共指令模块,比如存储器搬移指令,比较器,随机数发生器,必要的数据缓冲区,等等。表1列出几个典型的流程控制指令的例子。

表1 流程控制指令例子

4 遗传算法的例子

领域指令集LL7.PS是专为遗传算法GA(Genetic Algorithm)应用开发的构件库,包括适应度计算,父代-子代缓存管理,遗传计算(选择、交叉、变异),计算终止等。

在65nm工艺Xilinx XV5VLX110T-1FF1136 FPGA开发平台上,已经实现了一个遗传算法的DGIC芯片[12]。在片内云架构的WoB网络上部署4个遗传算法模块作为从节点,一个定序器作为主节点。其种群尺寸为512个体,个体数据长度是16 bits,其中高字节是x1,低字节是x2,适应度函数为f(x1,x2)=x12+x22,适应度值17 bits。随机选取个体二进制第5位作单点交叉,交叉概率为0.85。随机选取个体二进制第7位作变异,变异概率为0.05。初始化时,4个从节点同时接收到来自WoB的第一代种群的512个个体数据,分别进化计算并各自输出128个子代个体数据,总计512个个体数据提交到WoB总线。主节点再依次将这512个子代个体通过WoB总线发送到每一个从节点,继续下一代进化计算。实验时WoB总线位宽161位,其中1个下行WoB和4个上行WoB各32位,另外1位是FLAG。经ISE综合仿真,其资源分配如图8所示,占用FPGA V5 110T总资源的14%,其最高时钟频率为212.125 MHz,每时钟周期t=4.714 ns。DGIC模块进化计算一代耗时,约431 t,进化计算100代总计耗时0.203 ms。

图8 DGIC资源消耗

在1台PC计算机(CPU主频2.79 GHz,运行内存1.99 GB)上用Matlab软件计算完全相同的进化算法计算100代,tic-toc计时为不低于3 s,DGIC模块加速比为 3 000/0.203=1.477 8×104,优于CPU+GPU方案[11],尤其适合作为车载设备。

5 结论

源于生物进化的GA算法容易处理成一个并行算法,由于其庞大的计算集中在以种群为基础的算法,而种群中的个体相互没有依赖,特别适合ASIC的并行处理架构。但是GA算法的许多重要特征是无法参数化的,比如适应度函数、子种群数量、每个子种群大小、分析评价每一代计算结果的算法结构,及其终止计算策略,等等,都涉及到ASIC的结构改变,必须重新修改它的语义流程,传统的FPGA解决方案难以胜任。一种新的DGIC解决方案将冯诺依曼的顺序处理能力与ASIC的并行处理能力有机结合,使系统的可重构性拓展到语义流程和语法元素两个维度。本文提出的三层架构的建模开发平台Tri-Designer是DGIC设计领域的一种全新工具,其目标试图实现第七波集成电路产品特征:即“仅通过对配置编程就可得到用户自定义的芯片,从而引导半导体产业结构演变,促进不做芯片设计而专事芯片应用创新的Designless商业模式的兴起”,有着光明和广阔的应用前景。

[1]樊颖.基于SOA的云计算框架研究[J].中国新通信,2015(6):30-30.

[2]IOANNOU N,KAUSCHKE M.Phase-based applicationdriven hierarchical power management on the single-chip cloud computer[C]//Parallel Architectures and Compilation Techniques-Conference Proceedings,PACT,2011:131-142.

[3]张博.可重构ASIC片内云架构及其应用研究[D].太原:太原理工大学,2013.

[4]张刚,裴科,张中杰.一种多元资源节点的非对称架构[P].ZL200910265900.8,2011.

[5]WANG Y L,ZHANG G,CHANG Q,et al.Component-based functional integrated circuit system design and its straight implementation[C]//Networked Computing(INC 2011),2011:42-47.

[6]王悦.片内云架构的流程引擎设计实现[D].太原:太原理工大学,2014.

[7]张刚,张博,张陌.ASIC片内云架构和基于该架构的设计[P].ZL201310074630.9,2013.

[8]MAKIMOTO T.Makimoto’s Wave-a market model established in 1991[DB/OL].available on line.http://direct.xilinx-china.com/prs_rls/xil_corp/0392pw03_japan.htm.,2003-07-25/2004-09-10.

[9]许居衍,尹勇生.半导体特征循环与可重构芯片[DB/OL].2008,07,06,available on line.http://www.eeword.com.cn/news/eda/200807/article_21642.html.

[10]王帆.片内云架构及应用实例研究[D].太原:太原理工大学,2015.

[11]高卓.基于岛的遗传算法在CUDA上的优化实现[D].吉林:吉林大学,2011.