变电站实时监控系统中的千兆以太网传输设计

李文辉,简献忠,肖儿良

(上海理工大学 光电信息与计算机工程学院,上海 200093)

变电站实时监控系统中的千兆以太网传输设计

李文辉,简献忠,肖儿良

(上海理工大学 光电信息与计算机工程学院,上海 200093)

针对变电站实时监控系统需要传输的数据量大和传统的百兆网络已无法满足传输总带宽需求的问题,文中设计了嵌入式千兆以太网视频传输系统。该系统选用Xilinx公司Artix-7系列的FPGA芯片为主控制器,完成数据的采集、处理和传输控制。使用UDP/IP协议帧通过千兆以太网向远程监控系统传输图像数据时,丢包率仅为0.001 25%。在对变电站高压设备进行监控传输测试时,稳定传输视频图像的最高帧频可达150 frame·s-1。

变电站;千兆以太网;FPGA; UDP/IP

为了保证电力系统的安全稳定地运行,建设和推行智能变电站越来越受到了重视。变电站作为供电系统的中心环节,是电网中的监控重点,所以保证变电站的安全运行对供电系统的稳定性具有重要作用。而变电站中故障的发生多由站内高压设备的热效应引起的,因此必须实时地对变电站内高压设备的温度进行远程在线监控,以及时发现和维护出现故障的高压设备,保证电力系统的正常运行。而变电站中高压设备众多,导致实时在线监控系统需要传输大量的视频图像数据,并且传统的百兆网络带宽已经满足不了多个变电站对总的传输带宽的需求,因此有必要使用千兆以太网提高网络传输带宽[1-4]。

近年来,由于FPGA运行速度快,容易实现大规模系统,使得其在通信领域中的应用越来越广泛,并且随着电子技术的发展,高速数据传输系统在现代电子系统中起着重要的作用[5]。计算机与FPGA之间,主要通过以太网接口、UART和USB等通用接口相连接。由于传统的串口(UART或USB等)传输速度慢,难以实现高速数据传输,而且不能进行远程数据传输,需要FPGA和计算机必需在同一地点,这就限制了高速数据传输系统在使用时的灵活性以及在特殊场合(比如无人监控变电站)中的应用。千兆以太网相比百兆以太网,其传输速率更高、传输距离更远,满足智能变电站对网络传输带宽的需求[6-9]。

千兆以太网技术属于以太技术,兼容10/100 M的以太网系统。将10/100 M以太网升级到千兆以太网,不必改变PC端的网络应用程序和操作系统,这对原有的电力监控的网络建设来说节约了成本。

1 系统总体设计

视频数据传输平台中关于千兆以太网部分的实现,是基于Xilinx的Tri-Mode Ethernet MAC IP实现的[10]。FPGA与远端PC之间的通讯以ARP协议和UDP/IP协议为主,使用ARP协议和UDP/IP协议是为了使FPGA动态地获得访问它的PC的IP地址、MAC地址和PC应用程序的端口号,并将其存储在设定的寄存器数组中,用在向PC传输的UDP/IP协议视频数据帧的相关字段中。实现视频传输平台与监控中心之间的千兆以太网络通信的详细设计如图1所示。

(1)发送过程:接收的图像数据经过视频传输平台接收并转换成UDP/IP帧格式,转换后的数据通过TEMAC IP封装成标准的Ethernet II以太网帧,接着通过物理层芯片88E1111和网线传至千兆交换机,最后通过千兆交换机的级联将监控图像数据传至远端监控PC;

(2)接收过程:远端PC传至视频传输平台的指令帧,经过PHY芯片和TEMAC IP封装模块处理后由接收模块解析出指令数据;

图1 千兆以太网络的实现框图

2 UDP/IP硬件协议栈设计

在能够使用常用的网络通信协议(比如UDP协议、ARP协议)的前提下,参照TCP/IP参考协议,并对OSI参考模型进行精简,设计本系统千兆以太网使用的UDP/IP硬件协议栈结构[11-12],简化方式如图2所示。

图2 简化协议模型

在设计的简化模型中:应用层负责图像数据的相关处理,包括图像数据的读取与存储;传输层使用UDP协议实现,主要负责UDP报头的添加、验证和解析;网络层使用IP协议实现,用于实现IP报头的添加、解析,以及校验和的发送计算和接收验证功能;数据链路层使用ARP和MAC协议实现,负责地址解析、帧检查序列的添加与验证、滤除错误帧等;物理层则使用88E1111芯片实现,可以兼容十兆、百兆和千兆的以太网络[13-14]。

UDP协议位于简化的协议模型中的传输层。使用UDP协议传输数据时,无需像TCP协议一样先建立连接才能传输数据,同时不保留数据备份,因此具有不可靠性,允许一定的丢包率。但是UDP协议具有TCP协议望尘莫及的速度优势,提供了基本低延时的高效数据报传输和面向非链接的传输特性,可以有效解决网络中数据的实时传输问题。千兆以太网的数据传输速度快,而且是全双工传输。通过环路测试,在千兆以太网环境下测试,使用UDP通信的数据速度可达900 Mbit·s-1以上。因此,UDP协议适合高速数据传输的场合,比如视频图像传输、高速数据采集和网络监控数据交换等对数据传输速度要求比较高的场合[15]。

3 千兆以太网传输设计

3.1 GMII硬件接口设计

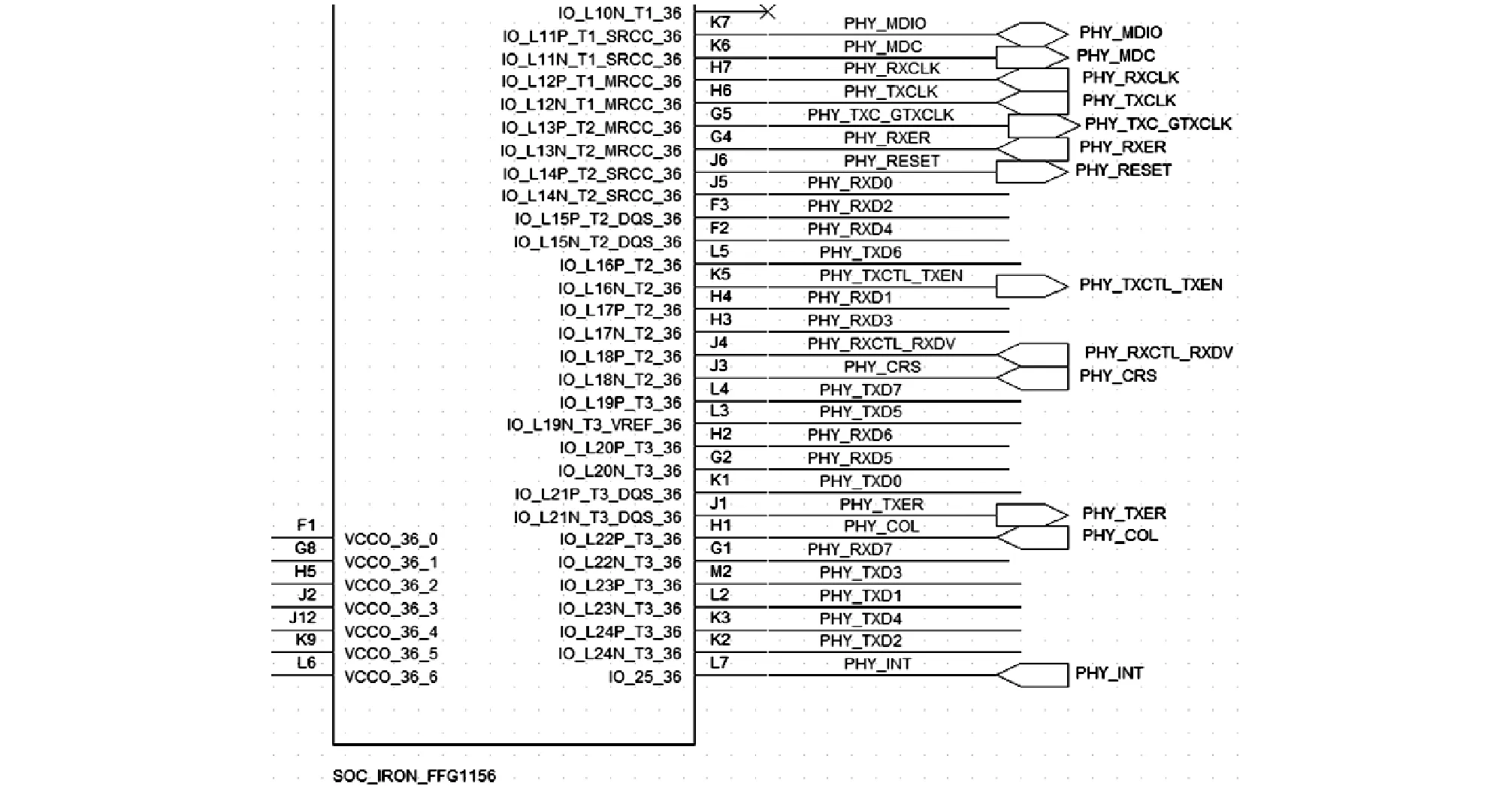

在硬件选择上,FPGA芯片已定,PHY层芯片选择Marvell公司的88E1111(128-Pin PQFP Package)作为千兆以太网物理层芯片,支持10/100/1 000 Mbit·s-13种速率的以太网传输。设计采用GMII(Gigabit Medium Independent Interface,千兆媒体独立接口)作为FPGA与88E1111之间的接口,电路设计如图3所示。

图3 以太网GMII接口电路

3.2 TEMAC IP定制

使用ISE14.4组件下的Core Generate tool来实现对TEMAC IP相关属性的配置,在生成IP后,相应的ip_core目录下生成了以VHDL描述的IP内部功能模块文件以及Xilinx提供的实现例程。该示例设计包括的功能有:TEMAC实现方案;时钟管理,包括MMCM和全局时钟缓冲器模块;GMII接口逻辑,包括IOB模块和DDR寄存器模块;统计向量解码逻辑部分;使用AXI4-Stream接口的用户传输和接收FIFO模块;用户基本模拟帧产生模块,包括一个帧产生模块和一个帧接收校验模块,同时提供回环测试逻辑;使用一个简单的状态机复位和配置PHY层芯片,准备MAC用于以太网帧的收发;以太网包收发缓存FIFO模块。

然而在进行应用设计时,必须对示例进行如下修改才能用于用户设计实现:修改Clock Generation模块,将差分时钟缓冲器模块移到TEMAC封装模块外部实现;移除基本模拟帧发生器模块;添加顶层封装所需的IO接口(AXI4-Stream接口)。修改后的TEMAC IP封装模块的原理图符号如图4所示。

图4 TEMAC IP封装模块原理图符号

在TMEAC IP工作于1 000 Mbit·s-1波特率时,与用户逻辑相关的重要时钟信号有:发送时钟GTXCLK,该时钟是由FPGA芯片外部差分晶振产生的差分时钟经过FPGA内部的差分时钟缓冲模块后产生,频率为125 MHz;接收时钟RXCLK,该时钟由PHY芯片从接收的以太网帧解析出来后经FPGA内的时钟缓冲模块获得,频率同样为125 MHz。由于TEMAC封装中使用了收发FIFO模块,发送FIFO模块的写时钟和接收数据FIFO的读时钟使用了同一个时钟信号,将其定义为USER_SIDE_CLK,频率为125 MHz,将其用于TEMAC封装的数据收发控制时钟。

3.3 基于TEMAC的收发模块设计

在FPGA向网络中传输监控视频数据时,由发送模块完成,其逻辑实现由以下两部分组成。

(1)ARP响应部分。当远端PC访问FPGA,使用UDP/IP协议帧发出指令要求FPGA向其传输视频数据时,首先会检查本机ARP缓存表,如果缓存表内没有该FPGA相应的IP-MAC地址映射信息,就会向网络中发送ARP广播请求,用以获知FPGA所处网络节点的MAC地址(MAC地址信息在FPGA内部配置,其信息固定)。FPGA收到ARP请求后,如果目的IP地址(即FPGA处IP地址)信息正确,则由ARP响应负责向PC回复一个ARP应答包;

ARP响应逻辑中,传给TEMAC封装模块的ARP应答信息分组内容如表1所示。其中Destination内容为FC-AA-14-A4-A6-D9,即测试时使用的PC的MAC地址;Sender MAC Address为00-0A-35-01-02-03,即FPGA网络节点的MAC地址,其中00-0A-35为网络设备号,代表Xilinx公司,后3个Byte由设计者自定义;Sender IP Address为设计者自定义的IP地址,一般与PC设置在同一网关内。TEMAC封装模块会在ARP应答信息前面加上8个Byte的帧前导字符,在其后面加上18个Byte的PAD字符和4个Byte的FCS字符,最后通过GMII接口传给PHY芯片;

表1 ARP应答信息分组

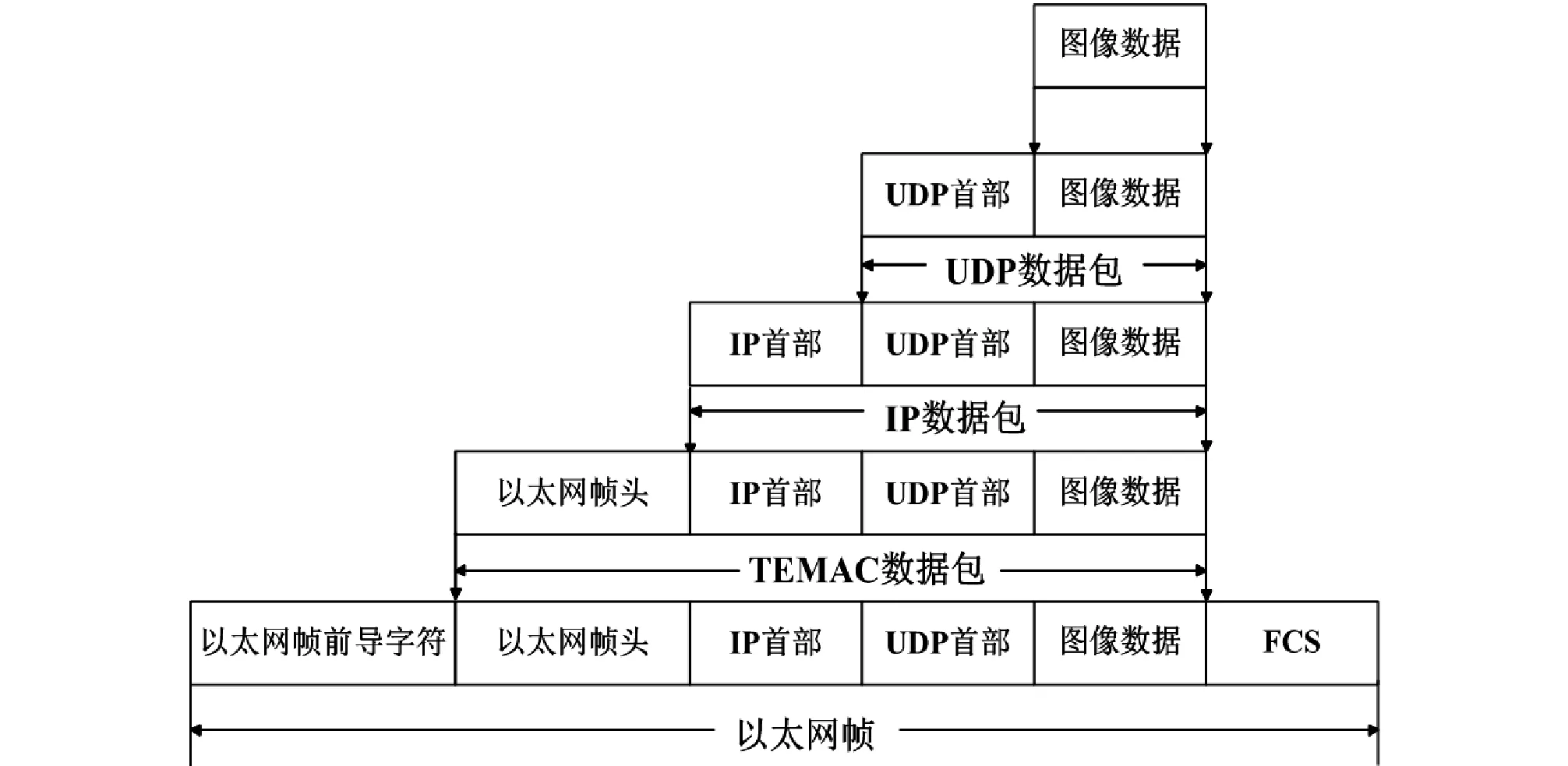

(2)UDP封装部分。该部分逻辑是将缓存在两块FIFO中的图像数据以乒乓的形式读出,并且将其封装,即在一行图像数据的前面依次加上以太网帧头信息字段(14 Byte,由目的MAC地址、源MAC地址、IP类型字段组成)、IP报头首部字段(20 Byte)和UDP报头首部字段(8 Byte),然后将封装的TEMAC数据包传给TEMAC封装模块进行最后的封装传至PHY芯片。UDP/IP协议的数据传输实现可以分为两个部分:一是从上层到下层的封装过程;二是由下层至上层的拆分过程。UDP/IP以太网帧数据封装流程如图5所示。

图5 UDP/IP以太网帧数据封装流程框图

在PC通过网络向FPGA传输指令时,FPGA内接收和解析协议帧的功能由TEMAC接收模块完成。TEMAC接收硬件功能模块实现流程如图6所示。其逻辑实现分为两部分:一是解析帧,判断数据包是否是ARP请求包,如果是,则将数据包中的PC的MAC地址、IP地址信息存储在设定的寄存器数组中,如果不是,则返回起始状态继续等待;二是判断数据包是否是UDP包,如果是,则接收保存PC应用程序的端口号和用户数据部分,否则返回起始状态继续等待下一帧的到来。

图6 TEMAC接收模块实现流程图

4 设计验证

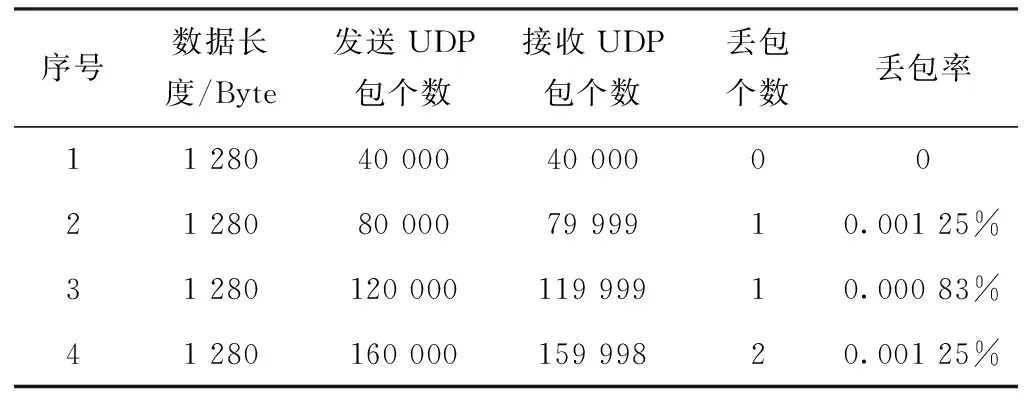

UDP帧的测试可以通过FPGA向PC发送一定量的数据包,在PC端查看接收到的UDP包的个数以及UDP包内数据部分是否正确。试验中对不同数量的数据包进行测试,其统计结果如表2所示,丢包率极低,对高帧频的监控视频图像来说,几乎没有影响。使用千兆以太网和UPD协议传输视频图像数据,既满足了高速传输的需求,又保证了传输的正确率。

表2 UDP包测试结果统计

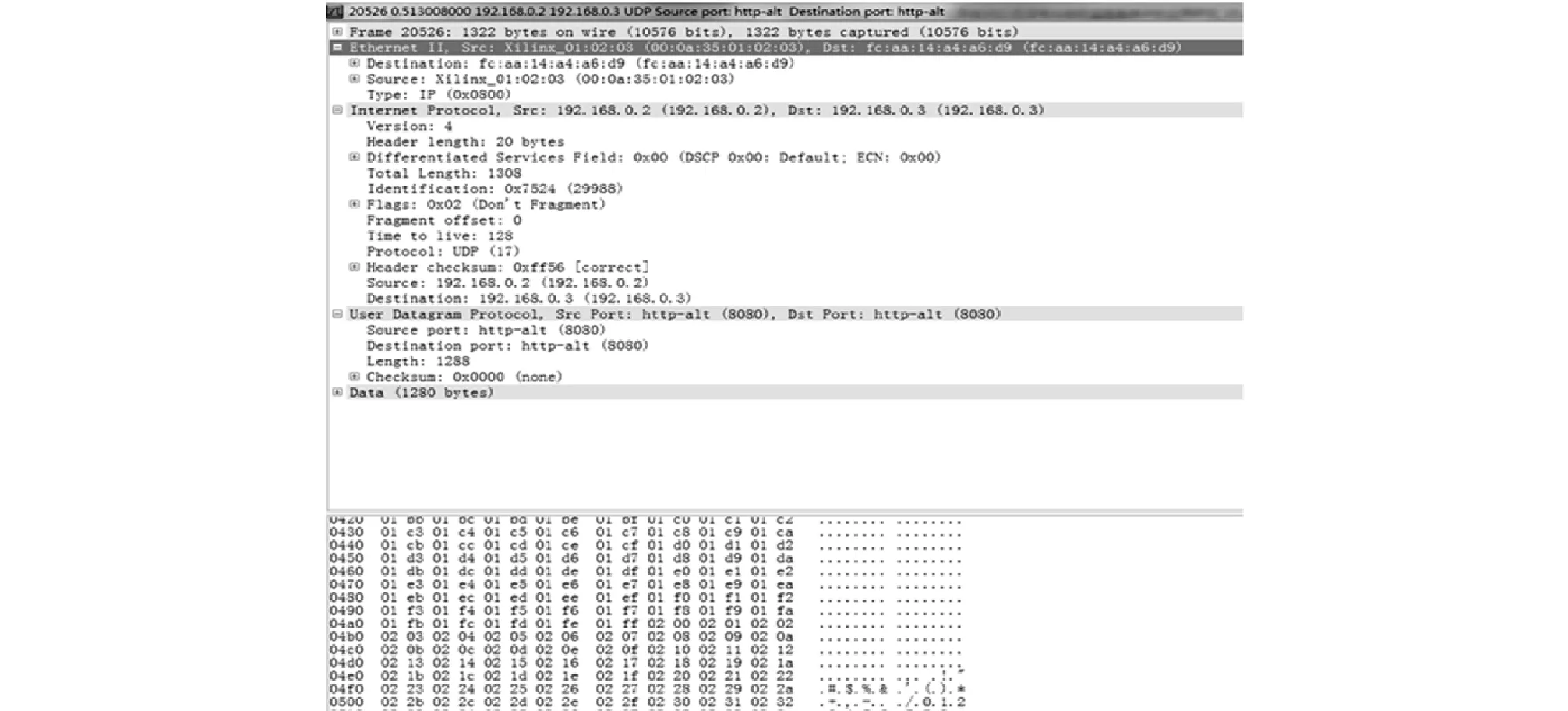

使用Wireshark查看其中一个UDP/IP协议以太网帧,如图7所示。其协议字段如下:Ethernet II字段共14 Byte,包括目标MAC地址、源MAC地址和帧类型;Internet Protocol字段共20 Byte,其中IP报头检查和校验正确,说明PC接收的包正确,没有出现错位的现象;User Datagram Protocol字段为8 Byte,可以看到源端口号和目标端口号以及长度字段;Data字段为传输的一行图像数据,共有1 280 Byte。通过分析各个字段内容,可以看到各个字段与所设计的FPGA内的发送帧完全符合。

图7 Wireshark查看一帧数据包

将红外摄像头采集到的变电站三相高压接触头的监控数据经视频传输平台传输至PC机端进行显示。PC端测试程序使用VC++实现,发送指令表示向FPGA端发送短的UDP报文数据包,清除FIFO中缓存数据;显示红外视频图像如图8所示。

图8 高压三相电触头温度监控显示

5 结束语

本文采用单片高性能FPGA实现了基于TEMAC IP的千兆以太网图像传输系统,实现了变电站内图像传输平台与远端监控主机之间的高速、连续、稳定、可靠的数据传输。测试证明,千兆网系统的逻辑设计思想正确,并且传输速率完全达到要求。该系统在实时监控和高速网络通信等领域,有着良好的应用前景。

[1] 龙俊飞.红外热成像技术及其在智能视频监控中的应用[J].企业技术开发,2015(2):48-48.

[2] 赵振兵,高强,李然,等.红外测温在变电站远程图像监控系统中的实现[J].电力系统通信,2005,26(4):27-28.

[3] 胡俊.基于以太网的变电站智能监视监控系统研究[D].西安:西安石油大学,2014.

[4] 陈伟,郝晓弘,张帆.变电站嵌入式以太网通信平台的设计与实现[J].电气自动化,2010,32(3):60-63.

[5] 何宇航,黄鹏,井实.基于FPGA的智能变电站网络报文处理装置设计[J].工业控制计算机,2016,29(5):1-3.

[6] 杨贵,王文龙,熊慕文,等.千兆交换机在智能变电站的应用探讨[J].电气技术,2010(8):129-132.

[7] 陈喆,顾国华.基于千兆以太网的红外热像仪数据传输[J].激光与红外,2012,42(1):41-44.

[8] 丁绍峰.千兆交换机在智能变电站中的应用[J]. 南方农机,2015,46(12):83-84.

[9] 石金成,张小辉,黄玉刚,等.基于FPGA的两路千兆以太网光纤传输系统[J].光通信技术,2013,37(7):15-17.

[10] Xilinx Inc.LogiCORE IP tri-mode ethernet MAC V5.5 porduct guide[M].USA:Xilinx Inc,2012.

[11] 崔鹤,刘云清,盛家进.基于FPGA的UDP/IP协议栈的研究与实现[J].长春理工大学学报:自然科学版,2014(2):133-137.

[12] 史鹏腾.基于千兆网的FPGA多通道数据采集系统设计[J].电子科技,2015,28(2):123-126.

[13] 韦宏,付友涛,孔凡鹏,等.基于FPGA的千兆以太网设计[J].现代电子技术,2012,35(18):56-59.

[14] 赵文达,赵建,曲锋,等.嵌入式千兆网高清视频传输系统设计[J].液晶与显示,2014,29(3):383-388.

[15] 张诚,罗丰.基于千兆以太网的高速数据传输系统设计[J].电子科技,2011,24(1):44-46.

The Design of Gigabit Ethernet Transmission System Based on FPGA in Real Time Monitoring System of Substation

LI Wenhui,JIAN Xianzhong,XIAO Erliang

(School of Optical-Electrical and Computer Engineering,University of Shanghai for Science and Technology,Shanghai 200093,China)

For the problem of large amount of transmitting data in substation real-time monitoring system and the traditional transmission network has been unable to meet the demand of the total transmission bandwidth, the embedded Gigabit Ethernet video transmission system has been designed. The system uses the Artix-7 series FPGA chip of Xilinx company as the main controller to complete the data acquisition, processing and transmission control. When using the UDP/IP protocol frame to transmit the image data to remote monitoring system through the gigabit Ethernet, the packet loss rate is only 0.00125%. In the monitoring transmission test on high voltage equipment in substation, the maximum frame rate of stable video image transmission is up to 150 frames per second.

substation; gigabit ethernet; FPGA; UDP/IP

2017- 03- 09

中国科学院项目(30133020001)

李文辉(1990-),男,硕士研究生。研究方向:嵌入式系统。简献忠(1969-),男,博士。研究方向:新能源、嵌入式技术应用等。肖儿良(1969-),男,博士。研究方向:嵌入式系统等。

TN911

A

1007-7820(2018)01-016-04