基于BIST方法的新型FPGA芯片CLB功能测试方法

石 超,王 健,来金梅

(复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

基于BIST方法的新型FPGA芯片CLB功能测试方法

石 超,王 健,来金梅

(复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

新型FPGA普遍使用了6输入查找表以实现可编程逻辑,如Xilinx公司的Virtex 5系列、Ultrascale系列等.由于I/O数量有限,针对这些芯片的CLB功能测试,可选择ILA级联测试法并利用位流回读进行故障定位,但由于CLB存在路径互斥,覆盖所有故障所需配置较多,而位流回读较为缓慢,限制了定位速度.BIST测试法通过直接检测CLB的输出来发现故障,所需配置数量少于ILA级联法,但需要将测试激励传递到所有BUT导致端口负载大,布线存在困难.本文提出了一种将ORA中闲置资源配置为锁存器链,以便传递测试激励的方法.该方法降低了端口负载.同时利用剩余的逻辑资源建立扫描链,大幅加快了故障定位速度.在Xilinx 7系列FPGA上的实验结果表明,与其他文献所用测试方案比较,测试所需配置次数由30次降低到26次,故障定位所需时间在2.4MHz时钟驱动下可达61.35ns.

现场可编程门阵列; 可编程逻辑块; 功能测试; 内建自测试

随着电子技术的发展,现场可编程门阵列(Field Programmable Gate Arrays, FPGA)芯片已经被广泛应用于通信、互联网、航空航天等诸多领域.对其进行功能进行测试的需求也水涨船高.可编程逻辑块(Configurable Logic Block, CLB)是FPGA芯片中最基本的可编程结构,被用于实现各种组合与时序逻辑功能,十分重要.其与互连资源、可编程输入/输出块(Input/Output Block, IOB)共同组成了FPGA的可编程功能.以较低的成本对CLB中功能进行测试,自然成为了FPGA测试的一项重点.

CLB的测试主要难点在于CLB阵列规模庞大,而IOB数量不足,以Xilinx 7系列芯片为例,其CLB数量最大可达102700个,而IOB仅960个[1].为了用有限的IOB输入测试激励并获取其响应,测试中一般采用重复逻辑阵列(Iterative Logic Array, ILA)级联法或内建自测试(Built-In Self-Test, BIST)法进行.

ILA级联[2]测试法通过构建输入与输出完全相同的ILA单元,并将其以链状级联.若1个ILA单元出现故障,故障响应会被后续ILA单元传递出来.文献[3]采用ILA级联法对Xilinx 7系列芯片的CLB1进行了功能测试.通过在ILA链输入输出端分别设置了测试激励生成和结果分析电路.解决了传统ILA级联测试法输出结果不直观的缺陷,自动化程度高,便于布线.但ILA级联测试法由于需要构成数据通路,而CLB内数据路径存在互斥,测试所需配置数量较多.而当ILA链上存在多个故障时,前级的故障可能导致后级无法接受到完整的测试激励,导致故障被掩盖.另外,文献[3]采用基于JTAG的部分位流回读进行故障定位,无法使用高速时钟,定位速度较慢.

BIST测试法将FPGA内的逻辑资源配置为测试激励生成器(Test Pattern Generators, TPG)、输出响应分析(Output Response Analyzers, ORA)和被测单元(Blocks Under Test, BUT)3部分,由TPG向BUT输入测试激励.以ORA单元分析BUT的响应.完成1组测试后,交换BUT、ORA、TPG的功能,即可覆盖FPGA中所有CLB资源.BIST测试法不需要形成数据通路,只需要保证被测模块能接收测试激励,同时其响应可以被ORA所分析即可,故BIST测试法所需配置数量较少.而BIST测试法直接输出测试结果,具有IOB占用少,不易发生故障互相掩盖的情况,测试结果直观,测试设备简单等优点.在XC-4000与Spartan1时代BIST测试法就被应用于CLB测试中[4].但传统BIST测试法需要将测试激励传输到每个BUT单元,布局密度高,测试激励信号负载大,布线成功率低.

为了减少测试配置数量,加快故障定位,本文提出了一种基于数据比较的BIST测试法的测试方法,该方法将ORA中闲置的可配置触发器配置为锁存器链进行测试激励传递,大幅减少信号负载,解决了BIST测试法布线上的困难.同时利用片内逻辑资源构成扫描链,能够采用高频时钟驱动,大幅提高了故障定位速度.

1 测试方法

Xilinx 7系列FPGA是Xilinx公司推出的新一代FPGA产品,涵盖了低功耗,高性能,SOC等多种应用场合,正越来越多的应用到各种电子设备中.本文选择了Xilinx 7系列FPGA作为研究对象,开发适用于新型FPGA芯片的功能测试方案.

1.1 新型FPGA芯片CLB模块的结构

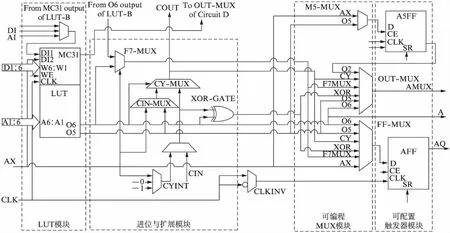

Xilinx公司新型FPGA的CLB模块由2个Slice组成,其结构如图1所示,每个Slice都通过开关矩阵接入全局与局部互连资源中,大量CLB以阵列形式分布于FPGA芯片内,与互连资源配合行使多种逻辑功能.

图1 CLB的基本逻辑单元AFig.1 Logic circuit A of CLB

图2 CLB的结构[5]Fig.2 Structure of CLB[5]

每个Slice可以分为A,B,C,D 4个相似的基本逻辑模块,其中模块A如图2所示,主要由6输入LUT,可配置触发器(可以配置为2个触发器或1个锁存器使用),进位逻辑和扩展逻辑模块,以及可编程MUX和其他控制电路组成.针对CLB的功能测试,即可以进一步细化为对上述4大模块中每1个电路元件的功能测试,关于元件的具体测试细节,将在下文详述.

另外,Xilinx 7系列FPGA中的CLB可以分为Slice L与Slice M 2种.Slice M中的LUT还可配置为分布式存储器(RAM)和移位寄存器(Shift Register),其相关逻辑如图2中灰色部分所示.

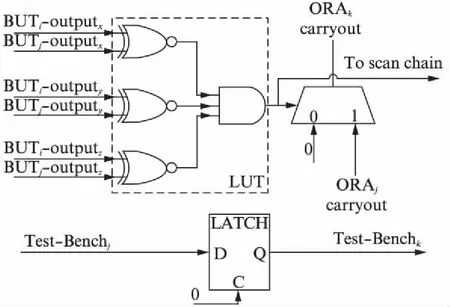

图3 ORA单元基本结构Fig.3 Diagram of ORA circuit

1.2 BIST测试电路基本结构

ORA单元的基本结构如图3(见第490页)所示.其中LUT通过配置组成3个同或门并将其结果相与,最多能够比较2个BUT的3组输入.恰能覆盖A,AQ,AMUX这3个信号.若被测的2个BUT均无故障,则每组的2个输入相同,LUT输出为1,反之,其中1个BUT存在故障导致2个BUT各组输入不相同,则LUT输出为0.该结果通过CLB中的进位链向外传递,最终输出.ORA单元同时也对进位链功能进行测试.

在FPGA中,由于内部互连的扇出能力有限,难以将测试激励传递到每一个BUT.本文将ORA中闲置的可配置触发器资源配置为锁存器链,如图3所示,将测试激励传递到BUT中,由于每个锁存器只需驱动10个BUT,激励信号的负载大大缩小,布线成功率明显提高.

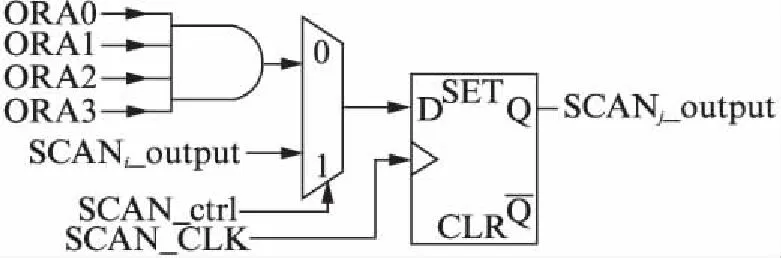

为了方便故障定位,本文使用了扫描链方法以获取每一个ORA单元的具体输出,其结构如图4所示.当SCAN_ctrl=0时,扫描链接受并汇总一个Slice的4个ORA单元输出.当SCAN_ctrl=1时,即可通过1个时钟将扫描链的结果扫出加以分析.

传统BIST测试法通常一次将CLB阵列中1/2的CLB配置为BUT,资源消耗大,测试激励负载高,布线成功率低,也无法在CLB中实现TPG模块与定位.由于新型FPGA芯片多采用6输入LUT,测试效率很高.即使一次只将1/3的CLB配置为BUT,重复3次.虽然总配置数量有所增加,但仍少于ILA级联法,却能使布局布线成功率大幅提升.同时阵列中剩余的逻辑资源可配置为扫描链与TPG模块,有利于测试覆盖和故障定位.

1.3 故障定位

故障定位的主要目的在于定位FPGA芯片中故障所处的位置,对于FPGA来说,如果故障的CLB可以被定位,则可通过约束禁止对该CLB进行布局.芯片仍可正常使用.本文使用了扫描链方案进行故障定位.正常测试时,扫描链会检测每一个ORA单元的输出.而TPG、BUT与ORA模块的阵列连接关系如图5所示.采用这种连接方式,除非一行中所有BUT发生了相同故障,否则该故障都能被ORA所检测到[4].但同一行BUT发生相同故障概率极低,故障之间很难互相掩盖,解决了ILA级联法后级不能接到完整测试激励可能有故障被掩盖的问题.

图4 扫描链单元基本结构Fig.4 Diagram of scan chain

图5 BIST测试法点路关系Fig.5 Structure of BIST circuit

当采用图5所示的布局方式时,若一个BUT中发生了故障,则应有2个ORA的输出结果为0,找出这2个ORA所共同检测的BUT即为故障的BUT.由于3组配置中所有CLB必然会被配置为BUT和ORA一次,3组配置测试完毕后总能定位到故障的CLB.

1.4 CLB各模块故障模型与测试原理

如1.1节所述,一个Slice主要包括LUT、可配置触发器、进位逻辑与扩展逻辑和可编程MUX与数据通路组成,部分Slice M还可以将LUT配置为分布式RAM和移位寄存器.这些模块结构各异,其故障模型与测试原理需要逐一讨论.

1) LUT模块: LUT本质上是一个只读的RAM,通常存在固定故障、断开故障、转换故障、译码故障[6].其中断开故障可视为固定型故障进行分析[7].转换故障可视为特殊的固定故障利用测试激励覆盖.文献[8]提出了一种采用K+1种配置即可覆盖K输入LUT所有固定故障和移码器故障的测试方案.针对6输入LUT,采用最少7个配置即可覆盖所有上述故障.

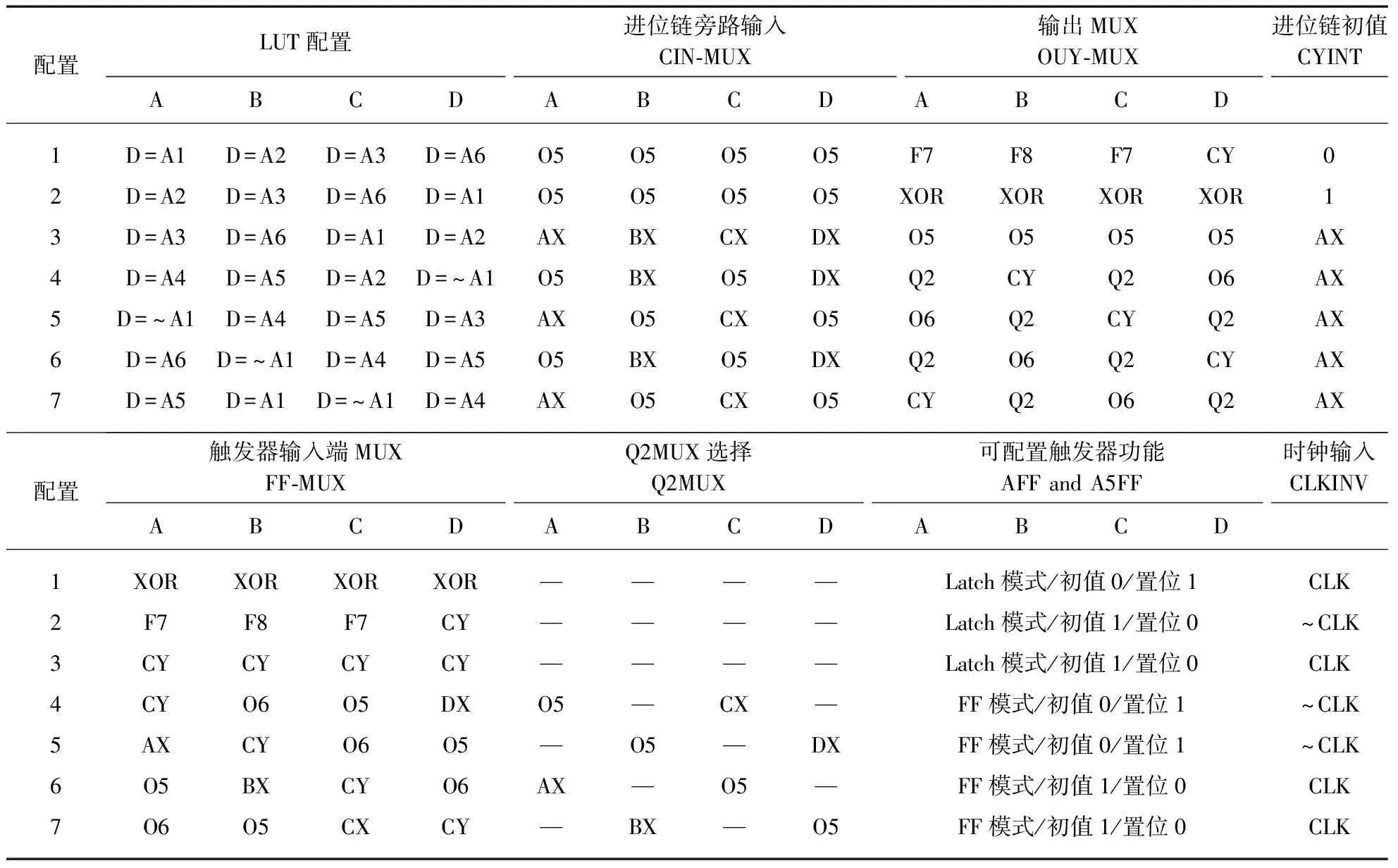

实际测试中,每个Slice的4个LUT输入相同测试激励,因此采用不同配置以产生不同的输出.各LUT所需具体配置如表1所示,符合文献[8]的要求.

2) 可配置触发器模块: Xilinx 7系列FPGA的可配置触发器模块既可以作为一个锁存器,也可以配置为2个触发器.对该模块测试主要考虑其能否正确存储与接受数据,是否被正确的时钟边缘触发,能否被正确的置位、使能,是否拥有正确的初值等.该模块测试的关键在于覆盖可所有功能组合并保证A5FF输出能正确被ORA检测.

表1 Slice L功能测试配置Tab.1 Configurations for test of Slice L

3) 数据通路与可编程MUX模块: 数据通路,主要指CLB内部互联和外部端口,一般只考虑固定故障.可编程MUX的故障与LUT译码器类似,有未选、选错、多选等故障,结合文献[8]的思想,在多个配置遍历MUX取址,保证所有配置下必有一个测试激励使得MUX未选中端输入与选中端不同,即可覆盖MUX的故障.

4) 进位链与扩展逻辑模块: 进位链与扩展逻辑由大量可编程MUX、不可编程MUX和XOR门组成.对于不可编程MUX和XOR门等简单的逻辑门,只需要对其输入端遍历所有输入,再将输出与该逻辑门的真值表进行比较,即可检测其是否存在故障.

5) 分布式RAM与移位寄存器: Xilinx 7系列FPGA中,约有1/3至1/2的Slice中可以将LUT配置为分布式RAM和移位寄存器,称为Slice M.只需将其他Slice L配置为ORA、TPG和扫描链,即可通过各类测试算法完成对分布式RAM和移位寄存器的测试

1.5 BUT模块的具体配置

对于BIST测试法来说,由于其采用直接向BUT模块输入测试激励,并检测输出响应的方法,因此BUT单元设计的关键在于保证被测电路的输入可以遍历所需测试响应,而输出信号可以被ORA检测到.在此基础上,针对不同电路模块的测试应尽可能整合起来以减少配置总数.通过统筹规划,测试单个Slice L的故障需要至少7个配置,如表1所示.采用上述7个配置后,Slice L中的逻辑资源除进位链输入与输出外,均得到了覆盖.而进位链输入与输出的功能在ORA模块中进行测试.

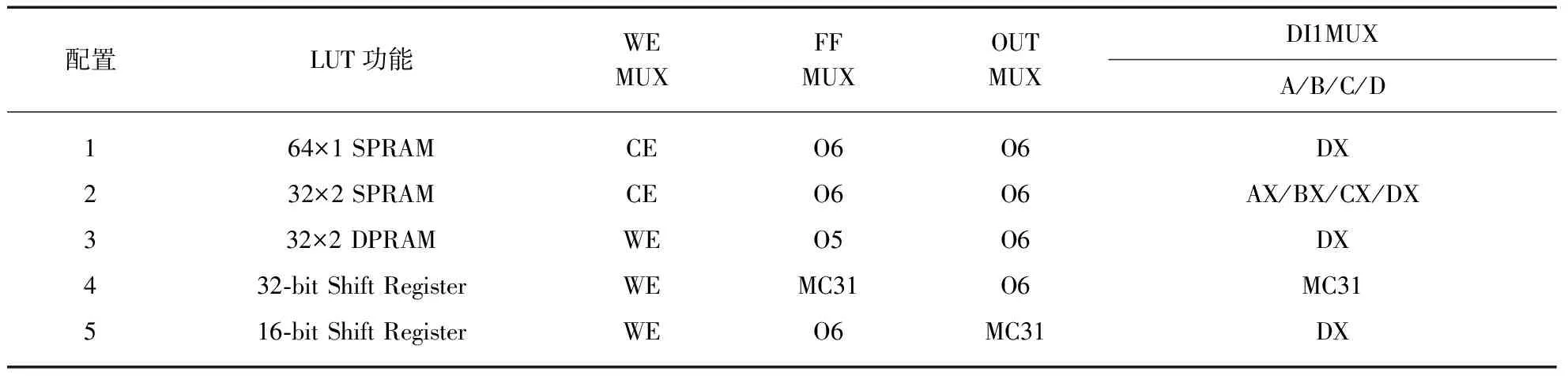

分布式RAM有多种配置模式,但大多由多个LUT与CLB资源组合构成,对于单个LUT只需测试3种配置即可.Slice M中的LUT还可以被配置为32-bit或16-bit移位寄存器.若分布式RAM和移位寄存器的存储单元或读译码器存在故障,则LUT测试阶段即可测出,因此对分布式RAM的故障测试集中在写入阶段,包括写入故障和写译码器故障,采用March C算法能够做到有效覆盖[6].而分布式RAM实际上共享同一个写译码器,因此完成一次March C测试后,其他配置只需采用MATS+算法测试其写入能力即可.分布式RAM和移位寄存器测试需要5个配置,如表2所示.

表2 分布式RAM与移位寄存器功能测试配置表Tab.2 Configuration of distributed RAM and Shift Register

2 测 试

2.1 故障覆盖率

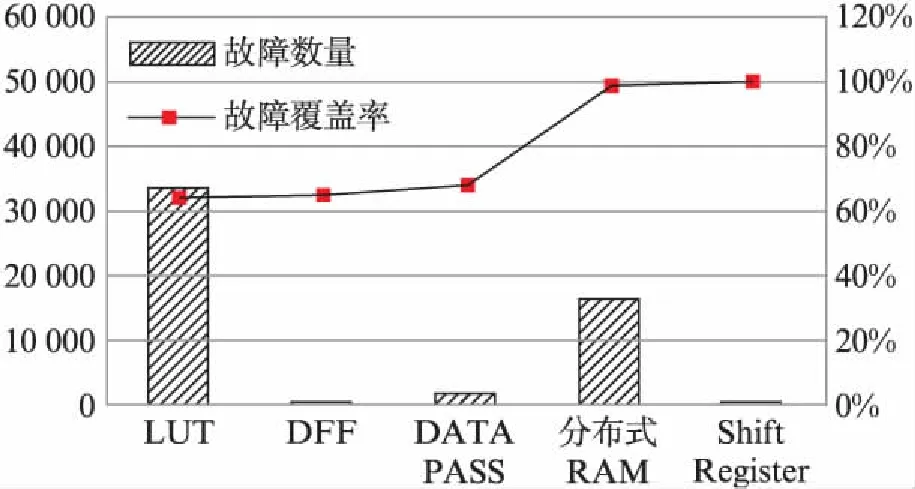

对Xilinx 7系列CLB中的所有功能进行了测试.测试配置的开发基于Xilinx官方提供的门级模型[5],对其功能配置和数据通路进行了故障模拟[9],同时在LUT等模块采用行为级故障模型.在各模块中逐一注入故障并进行功能仿真,将仿真后将结果与无故障模型的结果进行比较,即可判断注入的故障是否可以被检测出,便于统计,进位链、扩展逻辑、数据通路和可编程MUX归类一并归类为DATA PASS类故障.仿真结果如图6所示.可见遍历所有12个配置后,单个CLB的功能故障被完全覆盖.

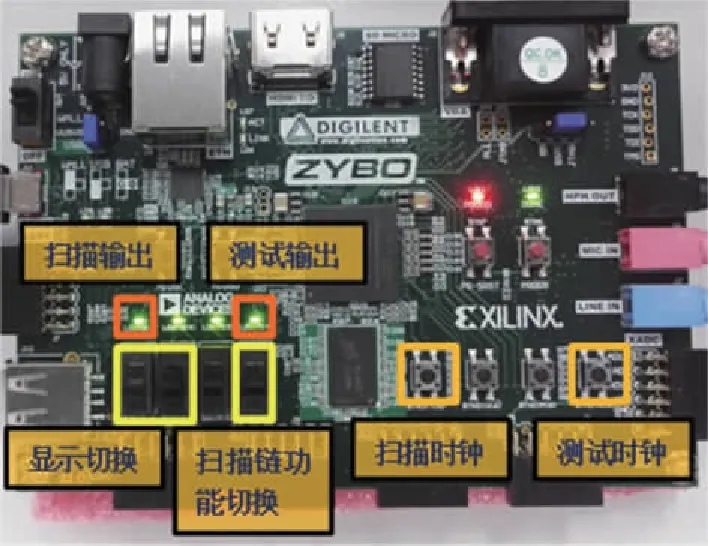

2.2 测试验证平台

本文采用了xc7z010芯片与ZYBO开发版构筑了模拟测试平台并进行了测试验证,模拟测试平台如图7所示,上电后,将所有开关拨下,并持续按动测试时钟按钮,若芯片在当前配置下无故障,则LED0维持亮起,遍历整个测试激励,若期间测LED0没有熄灭,说明芯片无故障.反之若LED0熄灭,说明发现故障.此时开关0拨上,并反复按动扫描链时钟按钮扫出各ORA的结果进行分析,结合测试配置即可进行故障定位.

图6 CLB测试故障覆盖率Fig.6 Fault coverage of CLB test

图7 基于ZYBO的测试验证平台Fig.7 Test platform based on ZYBO

2.3 结 果

使用2.2节介绍的ZYBO开发板为载体,将全部26个配置下载并测试后,测试结果均成功通过.

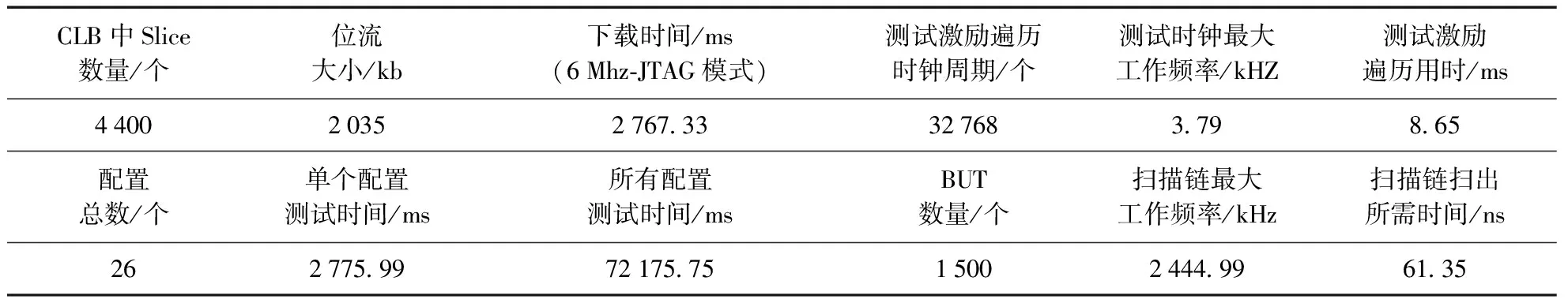

衡量FPGA功能测试成本的主要因素为测试时间.基于xc7z010芯片的单个测试配置测试用时如表3所示.其中,测试位流为实际生成的位流文件大小,测试激励遍历所需时钟周期和配置为BUT的Slice数量由实际测试配置得到,测试时钟最大工作频率与扫描链时钟最大工作频率通过Vivado工具的STA分析功能得到(该频率实际上仍较为保守,是电路维持时序正确的最大频率).根据上述数据即可计算出下载用时、测试激励遍历用时与扫描链扫出用时.3者相加即为一个配置测试所需时间.

表3 xc7z010芯片实际测试数据统计Tab.3 Summary of the test on chip xc7z010

观察表3可以发现,FPGA测试时间主要由下载时间决定,而下载时间受下载方式、位流数量与位流大小的影响.因此,若下载方式与位流大小相同,减少测试位流数量能够有效降低测试的时间成本.

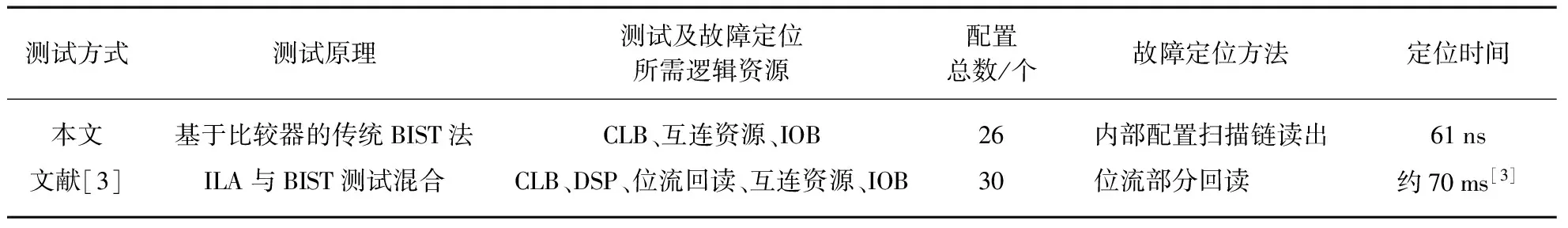

与文献[3]所用ILA级联测试法的对比如表4所示,可以看到,本方案配置次数由30个减少到了26个,定位所需时间由毫秒级大幅缩减到61ns,无论用于FPGA的出厂测试,还是高可靠性FPGA的部分测试,都有一定的实用意义.

表4 本文测试方法与ILA级连测试方法对比Tab.4 The comparison between ILA and BIST method

3 结 语

本文研究了一种采用BIST测试方法对于新型FPGA芯片CLB模块进行功能测试的方案.通过将CLB阵列划分为3等分,一次将CLB总数的1/3配置为BUT的方式,减少了布线难度,提高了布线的成功率,充分发挥了BIST测试法的高效率.同时通过内置扫描链进行故障定位,定位速度高于位流回读方法,并且不依赖特定电路结构,通用性较高.该方法在Xilinx公司7系列FPGA芯片上进行了实践,将测试所需配置数量由30个减少到26个.

该测试方法主要适用于采用高输入LUT的的FPGA芯片.Xilinx公司自Virtex5系列以上的新型FPGA芯片(如7系列、UltraScale系列)均采用6输入LUT,本文使用的测试方法对这种由高输入查找表组成的新型FPGA芯片测试中有广阔的应用前景.

[1] XILINX INC. 7 Series FPGAs Data Sheet: Overview[EB/OL]. 2016, http:∥www.xilinx.com.

[2] HUANG V K, LOMBARDI F. An Approach to Testing Programmable/Configurable Field Programmable Gate Arrays [J].VLSITestSymposium, 1996,14: 450-455.

[3] MODI H, ATHANAS P. In-System Testing of Xilinx 7-Series FPGAs: Part 1-logic [C]∥Proceedings-IEEE Military Communications Conference MILCOM. Tampa, FL, USA: IEEE Press, 2015: 477-482.

[4] STROUD C, LEACH K, SLAUGHTER T. BIST for Xilinx 4000 and Spartan series FPGAs: a case study [C]∥Proceedings: International Test Conference 2003. Charlotte, NC, USA: IEEE Press, 2003: 1258-1267.

[5] XILINX INC. 7 Series FPGAs Configurable Logic Block[EB/OL]. 2016, http:∥www.xilinx.com.

[6] 冯军宏,简维廷,刘云海.SRAM故障模型的检测方法与应用 [J].中国集成电路,2008(11): 65-68+94.

[7] FAN X, MOORE W, HORA C,etal. Stuck-open fault diagnosis with stuck-at model [C]∥Proceedings: European Test Symposium, 2005. Tallin, Estonia: IEEE Press, 2005: 182-187.

[8] LU S K, WU C W. A novel approach to testing LUT-based FPGAs [C]∥Proceedings: International Symposium on Circuits and Systems, 1999. Orlando, Florida, USA: IEEE Press, 1999: 173-177.

[9] TOUTOUNCHI S, LAI A. FPGA test and coverage [C]∥Proceedings: International Test Conference 2002. Baltimore, MD, USA: IEEE Press, 2002: 599-607.

ANewBuilt-InSelf-TestMethodforFunctionalTestofConfigurableLogicBlocksinModernFPGAs

SHIChao,WANGJian,LAIJinmei

(StateKeyLaboratoryofASICamp;Systems,FudanUniversity,Shanghai201203,China)

The modern FPGAs have begun to use 6-input look-up tables to perform configurable logic, such as Xilinx’s Virtex-5 series, Ultrascale series and so on. Due to the limited number of IOB ports, most approaches choose the ILA based method for the functional test of these chips’ CLB module, and use read-back techniques for fault isolation. Unfortunately some of the data-paths are exclusive in CLB; So ILA methods usually cost more configurations, while read-back is quite slow. The Built-In Self-Test(BIST) methods directorially check the output pins of CLBs, which reduce the number of configurations. But BIST methods should transfer test benches signals to ever BUT, which leads to massive fan-out and make it difficult to route the design. This paper presents a new BIST method which use the free resource in ORAs to form latch chains to transfer test benches. This method is able to decrease the fan-out of I/O ports. And the remaining logic resources are configured to form a scan-chain for faster fault isolation. The BIST method is tested on a Xilinx 7 series FPGA chips. Compared with the former works, the number of configurations is reduced from 30 to 26, and the cost of fault isolation is reduced to 61.35 ns with a 2.4 MHz clock.

field programmable gate arrays(FPGA); configurable logic block(CLB); functional test; built-in self-test

0427-7104(2017)04-0488-07

2017-03-15

石 超(1990—),男,硕士研究生;王 健,男,工程师,通信联系人,E-mail: wjian@fudan.edu.cn.

TN407

A