基于FPGA的目标边缘提取硬件加速系统的设计

张庭亮,甄倩倩,胡明明

(1.安阳工学院电子信息与电气工程学院,河南安阳455000;2.安阳师范学院软件学院,河南安阳455000)

基于FPGA的目标边缘提取硬件加速系统的设计

张庭亮1,甄倩倩2,胡明明1

(1.安阳工学院电子信息与电气工程学院,河南安阳455000;2.安阳师范学院软件学院,河南安阳455000)

传统的视频图像处理实时性不高,数据端与主机联动性差。为了提高目标边缘提取的实时性与实用性,设计了基于FPGA的目标边缘提取硬件加速系统。系统通过IIC总线配置摄像头参数采集视频数据,硬件滤波后由FPGA边缘检测模块提取边缘数据存入SDRAM。VGA控制模块将存储的数据输出至显示器显示。设计实现了对视频图像边缘实时提取,并在分辨率为640x480在显示器实时显示。经过测试,系统提取目标边缘清晰,实时性与实用性较高。

FPGA;边缘检测;硬件加速;实时显示

图像处理技术在监控、医疗、工业等领域得到广泛应用的同时,人们对于图像处理技术在具体应用中的要求也在不断提高,图像边缘是图像的最基本的特征之一[1-2]。图像的边缘检测是一般基于特定的研究领域,应用中的后续处理必须依赖于边缘检测时所提供的信息。图像边缘的实时提取系统应用于许多领域,例如交通监控、医疗、航天技术、卫星监控技术等[3-7]。动态目标追踪是图像处理以及机器视觉中的重要组成部分,难点在于边缘特征的提取,对动态目标图像边缘提取的准确度和实时性提出了较高的要求[8-9]。

1 硬件加速原理

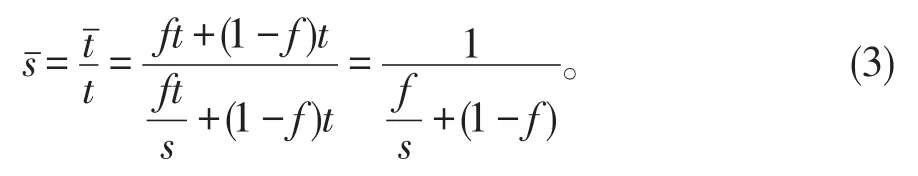

提高硬件电路对数据的并行处理能力是硬件加速的本质。在实际应用中,经常使用硬件复制和流水线方法。流水线处理方式中各子模块对数据的处理由FPGA内部的逻辑单元来完成,数据沿着一定方向依次通过各个逻辑单元时实现了对所有数据的处理,并且将经过处理操作的数据输出至存储器中[10-11]。在一个算法运行时,设定算法的核心部分运行时间占整个运行时间的比例为f,非算法核心部分的运行时间所占比例为1-f,所以消耗时间为:

如果通过硬件加速,那么加速器能够使运行算法核心所消耗的时间缩短为原来的s倍,这样一来整个过程的运行时间就为:

系统的整体性能就会得到有效的提高,其提高的效率为:

通过硬件来实现对系统的加速很大程度上依赖于算法的核心部分所占整个算法的比例。

2 Sobel算子边缘提取原理

边缘检测一般通过检测灰度值的不连续性实现,不连续性在图像导数中的表现为:一阶导数产生波峰或波谷,二阶导数产生零交叉。

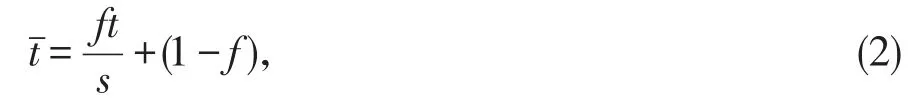

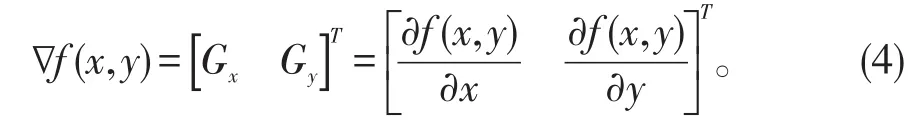

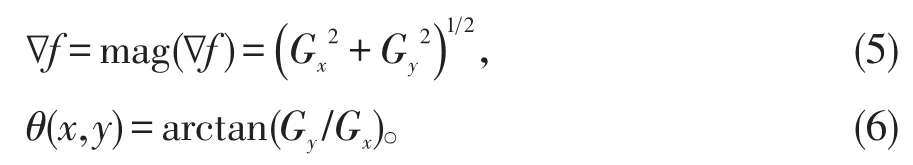

一阶导数通常用梯度来表示,对于图像函数f(x,y),梯度定义为:

幅度值和幅角为:

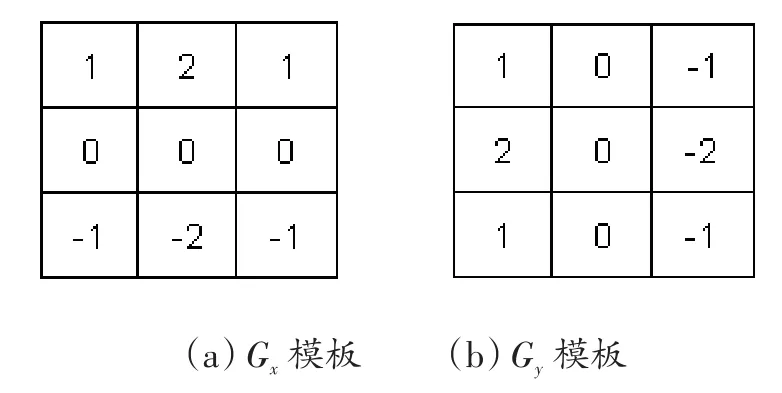

为了避免偏导数对每个像素进行位置计算,实际常采用区域模板代替Gx和Gy,不同的模板产生不同的边缘算子。Sobel算子是基础的梯度算子,其算法结构简单,通过对邻域像素点赋予不同权值计算梯度,因此Sobel算子能够较好的抑制噪声[1-3]。Sobel算子是加权平均,Gx,Gy模板如图1所示。

图1 Sobel算子模板

其表达式为:

3 实时图像边缘检测硬件加速系统设计

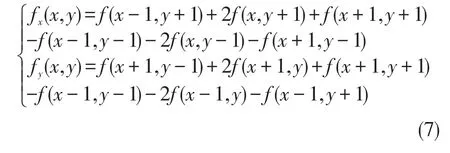

系统主要由两部分构成:FPGA内部的逻辑功能模块和外围硬件模块。FPGA的内部逻辑功能模块负责对图像数据进行相应的数据处理,主要包括对数据编码和位宽控制、图像数据的边缘检测;而外围硬件模块则由数据采集模块∕显示模块组成。系统设计具体结构如图2所示。

图2 系统设计框图

3.1 图像采集模块设计

系统采用的图像采集模块基于OV7725,属于CMOS摄像头系列,CMOS摄像头工艺简单,成本较低,功耗小。OV7725首先进行初始化,然后接收图像信号以及进行同步化设计;在模块设计时要求在寄存器修改后进行10帧延时,因此修改完成后需要进行场计数延时等待,当摄像头稳点后进行采样、拼接8bit输入数据,最终输出处理后的数据。图像采集模块设计流程如图3所示。

图3 采集流程图

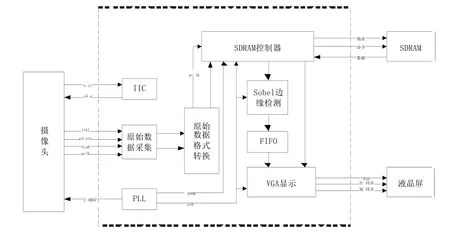

3.2 IIC模块设计

IIC是飞利浦公司提出的一种低速串行通信协议,由串行参考时钟(SCL)和串行数据(SDA)组成。系统中IIC模块的串行时钟(SCL)为12 Mhz,则iic_clk=2SCLK=24 Mhz。在执行写操作过程中,wr_req、addr、wr_data同步产生,需保持一个时钟等到busy的下降沿出现时即完成写操作;在执行读操作过程中,rd_req、addr同步产生,也需保持一个时钟等到busy的下降沿出现时即完成读操作,此时rd_data数据有效生成。在设计IIC模块时,为了使器件成功匹配应该在IIC接口处上拉电阻。IIC顶层设计如图4所示。

图4 IIC顶层设计图

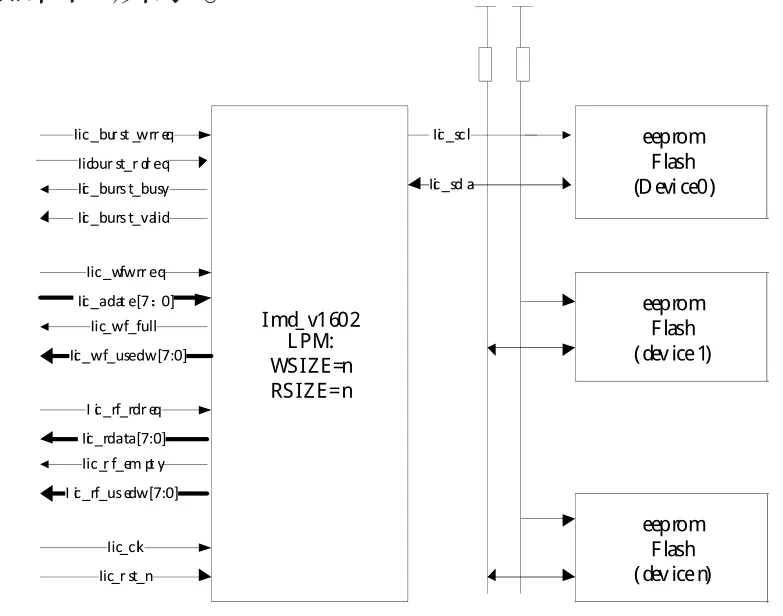

3.3 SDRAM模块设计

(1)SDRAM顶层设计

SDRAM控制器系统时钟为100 Mhz,图像数据采集模块的时钟为24 Mhz,其输出数据的频率为12 Mhz,后端VGA控制模块的时钟为25 Mhz,由于在一个时钟下系统只能对SDRAM中的一个地址进行读∕写操作,来协调前后模块的冲突,因此对SDRAM的读∕写控制是设计的核心部分,当控制模块和端口设置完成以后,对于顶层而言,系统对SDRAM和FIFO的操作过程基本一样。读∕写操作的控制通过读∕写控制模块根据读∕写端口存储的数据量多少来判断。SDRAM控制模块如图5所示。

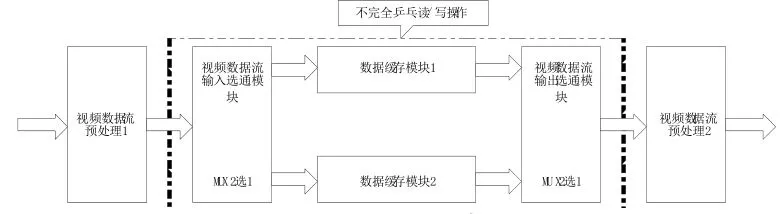

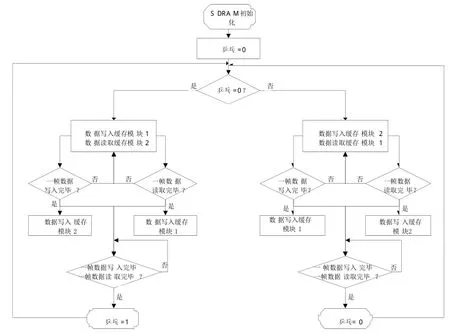

(2)乒乓操作

设计中的难点就是跨时钟域数据的实时传输问题,因此在图像缓存模块中调用FIFO模块,其与SDRAM连接来作为数据的缓存模块能够便于系统整体功能的实现。系统通过调用异步FIFO和乒乓操作来实现跨时钟域的数据传输以及图像的实时传输问题。其中乒乓操作的结构框图如图6所示,程序流程图如图7所示。

图5 SDRAM控制器顶层框图

图6 乒乓操作框图

图7 乒乓操作程序设计流程图

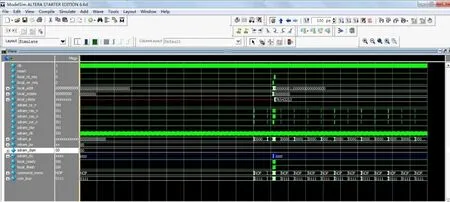

(3)SDRAM模块仿真

SDRAM模块的仿真图如图8所示,由仿真结果可知,在给定读∕写请求信号以及相应地址时,SDRAM就会进行相应的读∕写操作。

图8 SDRAM仿真图

3.4 边缘检测模块设计

通过图像缓存、卷积计算以及门限处理模块的应用完成Sobel算子对图像数据的边缘检测操作。图像数据在水平和垂直方向上梯度的具体运算是通过Sobel算子来实现的,然后再对这两个值进行均方根运算,最后把最终的数据通过门限处理即可得到边缘图像数据。其具体结构如图9所示。

图9 边缘检测硬件实现框图

卷积运算模块在边缘检测模块中肩负重大任务,其要通过Sobel算子计算图像数据水平、垂直两个方向上的梯度值。在边缘判断上需要设计一个门限处理模块,该模块通过比较接收的图像中心像素的梯度值与设定的阈值来判断图像的边缘。当梯度值比设定的阈值大时将其置1,比设定的阈值小时置0,此时即可得到图像的边缘。

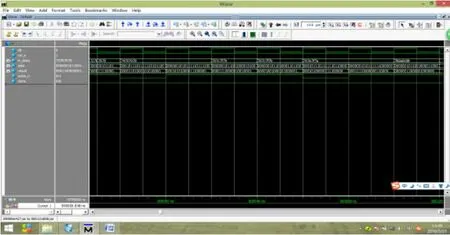

Sobel算子的仿真波形如图10所示。

图10 Sobel算子模块仿真图

3.5 VGA显示模块设计

VGA视频图像阵列,是一种被业界广泛使用的图像显示标准。采用ADV7123芯片来实现数∕模转换,通过FPGA内部的VGA控制模块来完成正确的信号传输工作。显示器是通过从左到右、从上到下的顺序在显示屏上进行逐点的扫描,当一行扫描完成后就产生同步负脉冲并且进行行消隐,然后再扫描下一行直至整个屏幕扫描完成。

4 实验结果

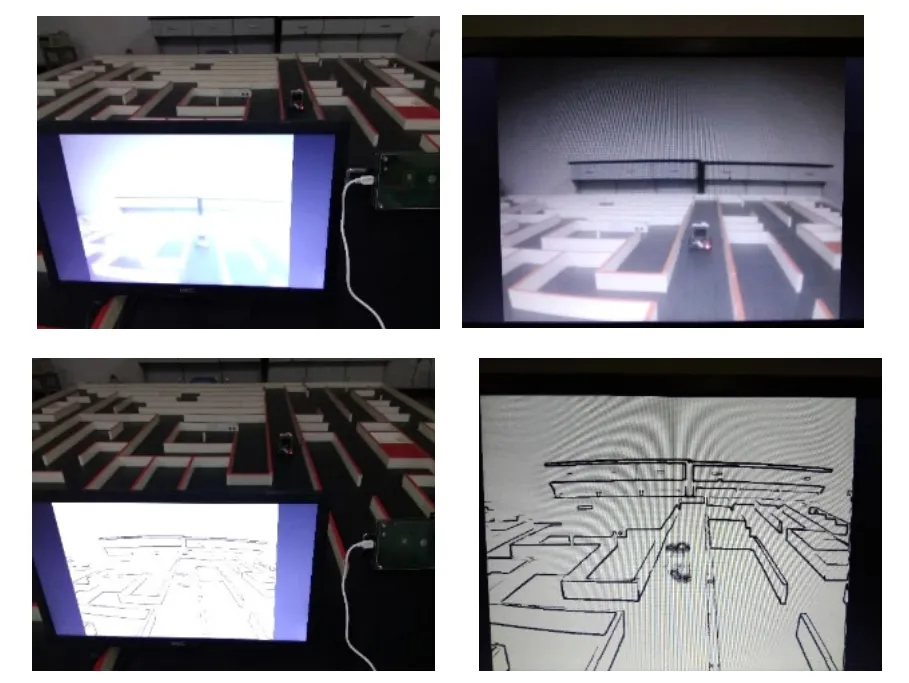

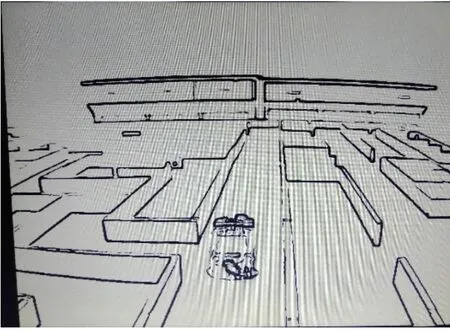

系统FPGA采用EP4CE6E22C8N为主控芯片,测试动态迷宫机器人的边缘实时提取。视频动态目标采集与边缘检测图像如图11所示。视频实时检测结果如图12所示。

图11 视频采集与边缘检测

图12 目标边缘提取图像

5 总结

利用FPGA对数据的并行高速处理来保证系统传输的实时性,实时对动态目标的边缘进行提取显示,显示分辨率为640x480。本系统具有高速、实时等优点,而且移植性很强,对于大多数的实时图像处理系统都可被应用。

[1]赵尧,董恩增,于晓.基于改进Sobel算子的实时边缘检测系统设计与FPGA实现[J].天津理工大学学报,2017,33(1):1-5.

[2]王晓娟,翟成瑞.基于FPGA联合Sobel算法的实时图像边沿检测系统的设计与实现[J].计算机测量与控制,2017,25(1):34-37.

[3]李阔,刘苗,林枫,等.基于FPGA的Sobel边沿检测研究[J].信息通信,2017(1):57-58.

[4]仝海峰,蔡俊,范静静.基于FPGA实时Sobel边缘检测形态学优化设计[J].微电子学,2015,45(6):781-784.

[5]谢周标,周毅,龙斌.二维椭圆硬件加速算法研究及其FPGA实现[J].计算机工程与应用,2015,51(3):45-49.

[6]周光宇,刘慧忠.边缘检测算法的FPGA实现[J].计算机系统应用,2015,24(10):271-275.

[7]宁赛男,朱明,孙宏海,等.一种改进的Sobel自适应边缘检测的FPGA实现[J].液晶与显示,2014,29(3):395-402.

[8]刘速,孙伟峰,王洪君.目标跟踪系统在FPGA上的实时实现[J].西安电子科技大学学报,2012,39(5):168-173.

[9]廖传柱.一种基于FPGA的Sobel边缘检测算法与仿真研究[J].长江大学学报(自科版),2015,12(7):37-40.

[10]李涛.基于FPGA的Sobel算子实时图像边缘检测系统的设计[D].北京:北京交通大学,2013.

[11]冯亮,刘紫燕,祁佳.基于FPGA的视频跟踪系统目标检测方法研究[J].微型机与应用,2014,(12):34-36.

〔责任编辑 高彩云〕

Design of Target Edge Extraction Hardware Acceleration System Based on FPGA

ZHANG Ting-liang1,ZHEN Qian-qian2,HU Ming-ming1

(1.School of Electronic Information and Electrical Engineering,Anyang Institute of Technology,Anyang Henan,455000;2.School of Software Engineering,Anyang Normal University,Anyang Henan,455000)

The traditional video image processing real-time is not high,the data side and the host linkage is poor.In order to im⁃prove the real-time and practicality of target edge extraction,an FPGA-based target edge extraction hardware acceleration system is designed.System through the IIC bus configuration camera can collect video data,filter hardware by the edge detection module to ex⁃tract the edge data into the SDRAM.The VGA control module outputs the stored data to the display.The design can to achieve realtime extraction of video image edges,and real-time display at a resolution of 640x480 on the display.After testing,the system can ex⁃tract the target edge clear,which is real-time and practical.

FPGA;edge detection;hardware acceleration;real-time display

TP391

A

1674-0874(2017)05-0027-04

2017-04-30

张庭亮(1989-),男,山西临汾人,硕士,助教,研究方向:模式识别与智能控制。