面向无线通信收发系统的锁相环设计

齐文军

(91550部队,辽宁 大连 116023)

面向无线通信收发系统的锁相环设计

齐文军

(91550部队,辽宁 大连 116023)

为缩短无线通信收发系统中锁相环(PLL)的锁定时间,文中研究了锁相环中的鉴频鉴相器(PFD)和电荷泵(CP)电路模块,通过引入全新的动态PFD和推入式电荷泵,消除了盲区的同时,缩短了锁定时间。基于上述研究,设计并实现了一种基于电荷泵的快速锁定锁相环(CP-PLL)。经过测试,该CP-PLL能够快速锁定203.4~286.6 MHz范围内的信号频率,具有锁定时间短、相位噪声小、功耗较低等优点。设计可提高中高速无线通信收发系统的信道切换速度,具有良好的应用价值。

无线通信收发系统;锁相环(PLL);锁定时间;鉴频鉴相器(PFD);电荷泵(CP)

锁定时间作为锁相环频率合成器的重要指标,其时间长短决定了锁相环(Phase-Locked Loop,PLL)所处通信收发系统的信道切换速度[1]。利用鉴频鉴相器(Phase Frequency Detector,PFD)在锁相环中添加延时单元可有效消除死区,但会引起复位时间的增加甚至是时钟边沿的丢失(盲区时间范围内),对锁相环的锁定速度造成较大的影响[2-3]。而使用前馈补偿法和分数分频法来缩短锁定时间,又会带来电路结构与操作复杂等问题[4-6]。就目前来看,唯有动态调整带宽方法能有效降低相位毛刺和噪声,并缩短系统的锁定时间[7-15]。

因此,本文重点研究了PLL结构中的鉴频鉴相器PFD和电荷泵(Charge Pump,CP)电路模块,提出并引入一种全新的动态PFD;结合动态调整带宽方法,配合推入式电荷泵的使用,加速PLL锁定,缩短锁定时间,有效消除运行过程中的盲区和死区。

1 电路设计

如图1所示,为本文所设计并改良的PLL结构示意框图。与传统PLL电路相比,新增了一条电荷泵回路,在PLL锁定前电荷泵CP2会保持运行状态,至PLL锁定前的某一设定时刻停止并退出该回路。该操作能有效降低电荷泵的锁定时间,且不会对环路功耗以及相位噪声造成不利影响。

图1 本文设计的PLL结构示意框图

1.1 PFD

如图2所示,即为本文提出并引入的全新动态PFD。初始时刻时,FEB=REF=DN=UP=0,且A=B=1,可推断出此时传输门T1(T2)导通,E=F=0,继而可知C=D=1。此时,若REF的上升沿优先于FEB,M11进入导通状态,B点开始放电,并逐步降低至低电平,之后UP=1;当FEB的上升沿到达,此时SW2=0,T2进入关断状态,而F依旧保持在低电平状态。此时DN=UP=1,PFD执行复位,M3(M9)导通,而M2(M8)截止,C(D)点开始放电并降低为低电平。之后M4(M10)导通,A(B)点开始充电并上升为高电平,DN=UP=0,经由与门,使M2(M8)导通,M3(M9)截止,至此复位完成。当DN=UP=0,此时G=1,使T1导通,信号FEB可传输到E,可知复位信号和SW1同时进行跳变,如此能够确保复位执行过程中到来的高电平信号能在复位过程结束后传送到E(F)点。此外,通过在复位电路中添加延时单元(由反相器构成)可对死区进行有效消除。当FEB(REF)信号恰好出现同频同相时,DN(UP)存在有窄脉冲,相应的PFD输出可见下图3。此时,即便反馈(输入)信号相位<Δθ,由于DN(UP)的脉冲宽度仍存在,电荷泵可继续正常运行,从而解决了盲区问题。

图2 本文提出并引入的全新动态PFD

图3 PFD输出情况

1.2 电荷泵

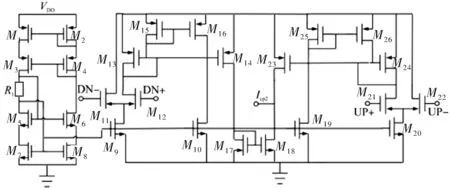

本文设计的电荷泵为保持锁定电荷泵CP1(在锁定和未锁定状态下工作)和推入式电荷泵CP2(在未锁定状态工作)。图4为本文设计的电荷泵CP1,其与传统电路结构不同,该电荷泵添加了两对电流镜(M15、M16以及M25、M26),用于开关的快速切换。

图4 本文设计的保持锁定电荷泵CP1

如图5所示,为本文引入的推入式电荷泵CP2。工作过程中,电荷泵充放电流(ICP1+ICP2)会在锁定后变为ICP1,可知引入CP2并不会对PLL环路带宽造成影响。

图5 本文设计的推入式电荷泵CP2

1.3 环路滤波器和压控振荡器

本文使用结构较为简单的二阶无源滤波器,避免了一阶滤波器所带来的PLL输出信号抖动问题。压控振荡器(VCO)方面,如图6所示,其包括了运放、偏振、复制偏振、延迟单元、起振电路、整形电路共6个模块。其中,整形电路用于提高带负载能力,并将正弦波信号转化成方波信号(占空比50%),去除输出信号的抖动;添加放大器电路构成一个负反馈系统,用于稳定压控振荡器的输出。

图6 压控振荡器(VCO)示意框图

2 电路性能

本文设计的CP-PLL芯片成品,如图7所示(台积电0.35 μm工艺),芯片面积经测量为0.44 mm2。整个MPW芯片含6个子芯片,共40个引脚,图中显示的8个引脚为测试引脚。

图7 本文的CP-PLL芯片照片

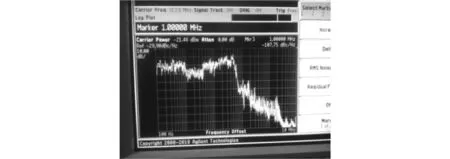

本文对设计的PLL进行了相位噪声、功耗、锁定时间和VCO压频等特性的测试和研究。如图8所示,为PLL的相位噪声结果图。从中可知,1 MHz位置处相位噪声为-107.8 dBc/Hz。将参考频率设定为6~9 MHz,拟合锁相环输出信号频率和压控振荡器输入电压,可得到VCO压频特性曲线(灵敏度为83.2 MHz/V),见图9。从图中可以看出,设计的PLL能锁定203.40~286.60 MHz范围内的信号频率,且锁定时间能够低于60个时钟周期,整体功耗也较低(约为13.2 mW)。

图8 本文PLL测试的相位噪声结果图

图9 VCO压频特性曲线图

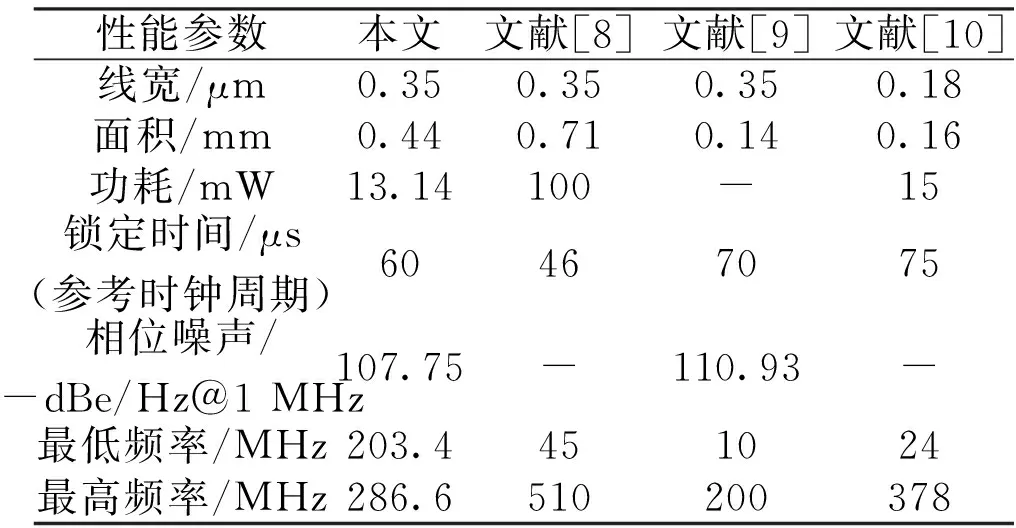

本文统计了部分已发表论文中的快速锁定PLL的性能参数,并与文中设计的快速锁定电荷泵PLL性能进行了对比,结果如表1所示[8-10]。本文设计的PLL虽面积稍大,但锁定速度较快,且功耗最低。

表1 与各文献性能比较

3 结束语

本文基于传统的快速锁定锁相环电路,优化了各模块电路。引入全新的动态PFD,消除了盲区的同时,缩短了锁定时间;引入含两对电流镜的保持锁定电荷泵,使开关实现快速切换;引入推入式电荷泵,并结合动态带宽调整方法,促进PLL快速入锁,并维持功耗和相位噪声稳定;调整并改良了压控振荡器以满足本文PLL的设计需求。经测试发现,本文设计的快速锁定锁相环能够迅速锁定处于203.40~286.60 MHz范围内的信号频率,并具有锁定时间较短、功耗较低等优势。可用于提高中高速无线通信收发系统的信道切换速度,具有良好的应用价值。

[1] 安娜.基于锁相环分频器的研究[D].西安:西北大学,2014.

[2] Lee K S,Park B H,Lee H I,et al.Phase frequency detectors for fast frequency acquisition in zero-dead-zone CPPLLs for mobile communication systems[C] .Paris:Proceedings of the Solid-State Circuits Conference,2003.

[3] 但慧明,柴旭朝,于宗光,等.一种用于锁相环快速锁定的动态鉴频鉴相器[J].微电子学,2010,40(5):653-656.

[4] Hsieh P H,Maxey J,Yang C K K.A phase-selecting digital phase-locked loop with bandwidth tracking in 65-nm CMOS technology[J].IEEE Journal of Solid-State Circuits,2010,45(4):781-792.

[5] Sidiropoulos S,Liu D,Kim J,et al.Adaptive bandwidth DLLs and PLLs using regulated supply CMOS buffers[C].MA,USA:Symposium on VLSI Circuits,2000.

[6] Zhang B,Allen P.Feed-forward compensated high switching speed digital phase-locked loop frequency synthesizer[C].Taipei:IEEE International Symposium on Circuits and Systems,2002.

[7] 陈希,张锐.基于可变带宽数字锁相环的快速载波同步[J].遥测遥控,2010,31(2):47-50.

[8] 杜敏.频率合成器中延时线锁频环的研究与实现[D].成都:电子科技大学,2013.

[9] Chung C C,Lee C Y.An all-digital phase-locked loop for high-speed clock generation[C].CA,USA:IEEE International Symposium on Circuits and Systems,2002.

[10] 徐江,刘元,于奇.宽范围快锁定CMOS电荷泵锁相环的设计[J].电子元器件应用,2010(1):72-74.

[11] 谭茗.基于40 nm CMOS工艺电荷泵锁相环前级电路的设计[D].长沙:长沙理工大学,2013.

[12] 李容容.一种集成在DC-DC芯片中的电荷泵锁相环设计[J].电子科技,2016,29(8):25-27.

[13] 孟海舟.一种通信用低噪声电荷泵锁相环的研究与设计[D].上海:上海交通大学,2013.

[14] 陶长亚.宽带高性能频率合成器设计[J].电子科技,2016,29(6):65-67.

[15] 付钱华,易淼.DDS激励PLL高性能频率合成器设计[J].电子器件,2016(1):62-66.

Design of Phase-locked Loop Applied for the Wireless Communication Transceiver System

QI Wenjun

(91550 Unit,PLA,Dalian 116023,China)

Aiming to shorten the locked time of the phase-locked loop(PLL) in the wireless communication transceiver system,the phase frequency detector(PFD) and charge pump(CP) circuit modules in the PLL are mainly researched in this paper. By introducing a new dynamic PFD and push charge pump,the blind area is eliminated and the locked time is shortened,respectively. Based on the above research,a fast locking CP-PLL is designed and implemented. It is tested that this CP-PLL can quickly lock the signal frequency in the range of 203.4-286.6MHz with the advantages of low locking time,small phase noise as well as the low power consumption,which can improve the channel switching speed of the high-speed wireless communication transceiver system and have a good application value.

wireless communication transceiver system; phase-locked loop; locked time; phase frequency detector; charge pump

TP393

A

1007-7820(2017)11-117-03

2017- 01- 07

齐文军(1966-),男,高级工程师。研究方向:飞行器试验测控和通信技术。

10.16180/j.cnki.issn1007-7820.2017.11.032