板间高速数据传输接口的设计与实现

滑 莎,李 锋,武磊磊

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

板间高速数据传输接口的设计与实现

滑 莎,李 锋,武磊磊

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

为了解决板级间并行接口无法满足高速率数据传输的问题,提出了基于FPGA的高速串行光纤数据传输的设计方案。采用Virtex-7系列FPGA作为主控芯片,通过芯片内部集成的高速串行收发器GTX连接SFP+光模块,进行了高速串行接口设计,并介绍了Aurora串行传输协议的设计。通过分析Xilinx专用调试工具集成比特误码率测试仪IBERT对光纤链路的测试以及Chipscope抓取板卡上的实际测试结果,在硬件上实现了串行传输速率为10 Gbps的光纤数据传输。

高速串行;SFP+光模块;光纤通信;Aurora协议

AbstractIn order to solve the problem that parallel interface between boards can’t meet the requirement of high-speed data transmission,a design scheme of high-speed serial optical fiber data transmission based on FPGA is proposed.This design uses Xilinx Virtex-7series FPGA as the main control chip.And the high-speed serial interface design was carried out through the chip internal integration of GTX transceiver link SFP+ optical module.The hardware circuit is designed.And the design of Aurora serial transmission protocol is introduced.Xilinx special debugging tools IBERT to test fiber link is analyzed and the actual test results on the board captured by Chipscope is presented.Finally the serial data transfer rate of 10 Gbps optical fiber transmission is achieved with hardware implementation.

Keywordshigh-speed serial;SFP+optical module;optical fiber communication;Aurora protocol

0 引言

随着通信技术的发展,对通信数据的存储容量以及传输速率提出了更高的要求[1],传统的并行总线传输方式在线路开销、接口复杂度、相互干扰及传输距离等方面面临极大的困难。应用于电路板间或设备间的高速数据传输,采用并行传输方式在线路干扰等方面无法满足高频大容量数据的及时传输。此时,高速串行传输方式则逐渐显露出其在远距离、高速率和大容量数据传输方面的优势[2]。尤其是使用光纤进行数据传输,满足了高速率和大容量等需求。

在光纤通信领域,文献[3-4]论述了SFP+光模块作为光纤通信常用的核心器件之一,具有自己独特的优势:可热插拔特性和数字诊断的功能。目前的光模块速率已经达到10 Gbps及以上。在SFP+光电模块数据传输链路中高速串行数据传输是其关键支撑技术[5]。

本文基于实际需求,设计了基于FPGA的高速串行光纤数据传输板卡,该板卡能够满足高速率数据传输的要求,使设备轻便、小型化,从而减小设备的体积和功耗。

1 硬件设计

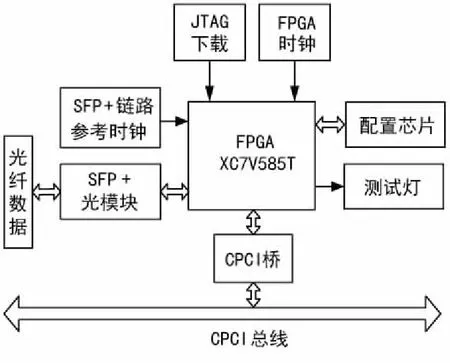

1.1 板卡设计

本文设计的光纤数据传输板卡实现了与其他设备进行通信的功能,其串行传输速率可达10 Gbps。板卡原理框图如图1所示。尺寸为6U CPCI板卡,FPGA作为整个通信系统的核心完成对整个板卡的逻辑控制,SFP+光模块完成板卡与其他设备之间的光信号分合路功能。CPCI接口完成对板卡的取电,并完成与上位机之间的数据交互。配置芯片完成动态快速加载的功能。

图1 光纤传输板卡原理

器件的选型对整个板卡的性能至关重要。本文设计选取了Xilinx公司的XC7V585T-2FFG1761C作为主控芯片,选用的FPGA芯片采用FF1761 BGA封装,包含91 050个Slices和6 938 KB的分布式RAM,850个用户I/O,可以满足FPGA外围电路设计和后期VHDL程序设计[6]。XC7V585T总共有36个GTX高速串行收发器[7],能提供500 Mbps~12.5 Gbps的数据线路速率。满足设计指标中数据传输速率10 Gbps的要求。

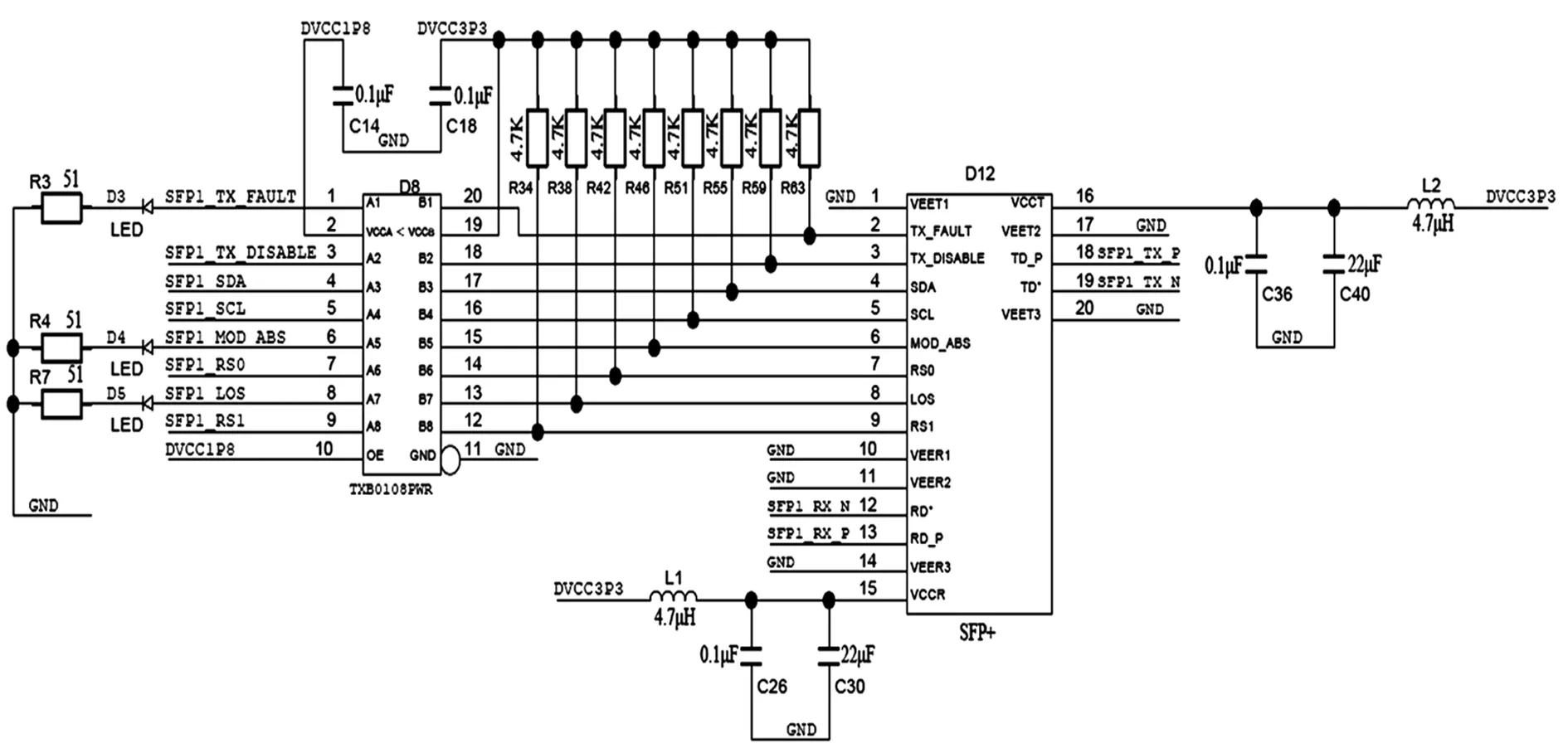

1.2 SFP+光模块接口电路设计

本设计选取型号为FTCS-151X-80DI,波长1 550 nm,传输速率可达到10.3 Gbps,收发一体SFP+光模块进行光电转换。并且具有自诊断功能,支持热插拔,使用起来非常方便。

SFP+光模块接口电路图如图2所示,本板卡设计了10路光模块接口,分布在FPGA内部集成的高速串行收发器的3个BANK中。Tx_Fault引脚是发送错误指示,当光模块检测到发送数据错误时,引脚电平被拉高,为便于检测光模块工作状态,在设计电路时,将此引脚连接到测试灯上,灯亮则表示发送错误;Tx_Disable引脚是屏蔽发射模块指示,此引脚为高电平或开集表示关断发射模块,程序设计时将此引脚置低;MOD_ABS是光模块检测引脚,测试灯亮表示模块未接到电路板上;LOS引脚是信号接收丢失指示,此引脚为低电表示接收的光功率在正常工作范围内,高电平灯亮则表示接收的光功率的灵敏度小于设定的最小值[8];SDA和SCL引脚组成了I2C总线,分别定义为串行数据线和时钟线;RS0和RS1引脚定义为速率选择。为增强引脚的驱动能力,上述引脚都需连接4.7~10 K电阻上拉到VCC。在FPGA芯片和光模块之间加入电平转换芯片TXS0108EPWR,实现+3.3 V和+1.8 V的转换。引脚RD+与RD-为差分信号输入引脚,TD+与TD-为差分信号输出引脚。在PCB布线时,信号线需要走内层,不允许有过孔,并保证控制差分阻抗为100 Ω[9]。

图2 SFP+光模块接口电路

VCCT引脚和VCCR引脚分别为光模块的发送部分和接收部分提供电源,供电电压要求3.3 V±5%,供电电流需在300 mA以上,用于滤波的电感的直流等效阻抗应该小于1 Ω,电源使用专有的滤波网络,可以保证光模块热插拔时的浪涌电流小于30 mA[10]。

1.3 GTX电源和时钟设计

设计要求10个GTX同时工作,所以对电源质量的要求非常严格。GTX都有独立的电源供电引脚。并且V7系列的GTX划分了3种供电电压,为了减少电源之间的干扰,不同的供电电压都有独立的供电模块,其供电电压的精度在±3%以内,来保证GTX的稳定工作。为了使供电电路稳定,在靠近电源的引脚处加入滤波电容和电感磁珠进行电源滤波设计,减少干扰[11]。

对于高速率数据传输来说,GTX要求低抖动、高质量的参考时钟。参考时钟的频率选择是根据GTX收发数据的速率和使用哪种数据协议来决定的。在设计的时候采用精度为±50 ppm的差分时钟芯片LVDS-156.25 MHz为光模块提供时钟。为了降低时钟线上的高频干扰,差分传输线上采用交流耦合的方式,所以电路设计中选用0.1 μF的电容作为耦合电容。布线时,耦合电容尽可能靠近差分时钟输出引脚。

2 协议制定与实现

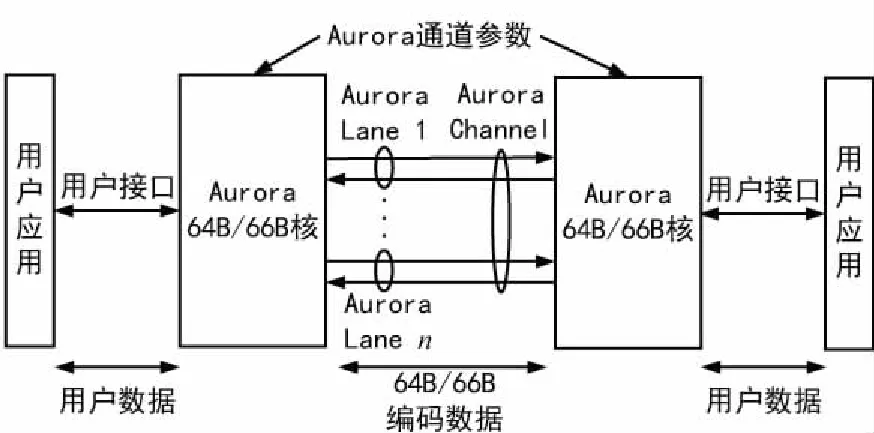

GTX是内嵌在FPGA中的高速串行收发器,具有8B/10B、64B/66B编解码、时钟生成和恢复等功能,适用于背板、电路板间和芯片间的高速串行数据传输。它的链路层协议为Aurora协议[12]。

Aurora协议是一款高带宽、低成本、可扩展、框架简洁且适合点对点串行数据传输的协议。该协议是为专有的上层协议或行业标准的上层协议提供透明接口的一款串行互连协议[13]。它可以通过增加通道数,扩展系统带宽。当一路信道不能满足传输速率要求时,可以使用2个或多个通道进行数据传输,提供的用户接口不变,方便系统升级[14]。Aurora协议可以配置每个通路中的GTX工作在全双工或半双工的模式下[15]。Aurora链路结构图如图3所示。

图3 Aurora链路结构

设计中Aurora协议采用全双工模式,帧控形式进行数据传输,参考时钟为200 MHz,用户时钟为156.25 MHz,发送和接收数据位宽均为64 bits,通道线速率为10.312 5 Gbps。由于光纤数据传输经过GTX高速串行收发器采用64B/66B数据编码,因此通道串行数据传输有效线性速率为10 Gbps。

3 链路测试

3.1 物理层测试

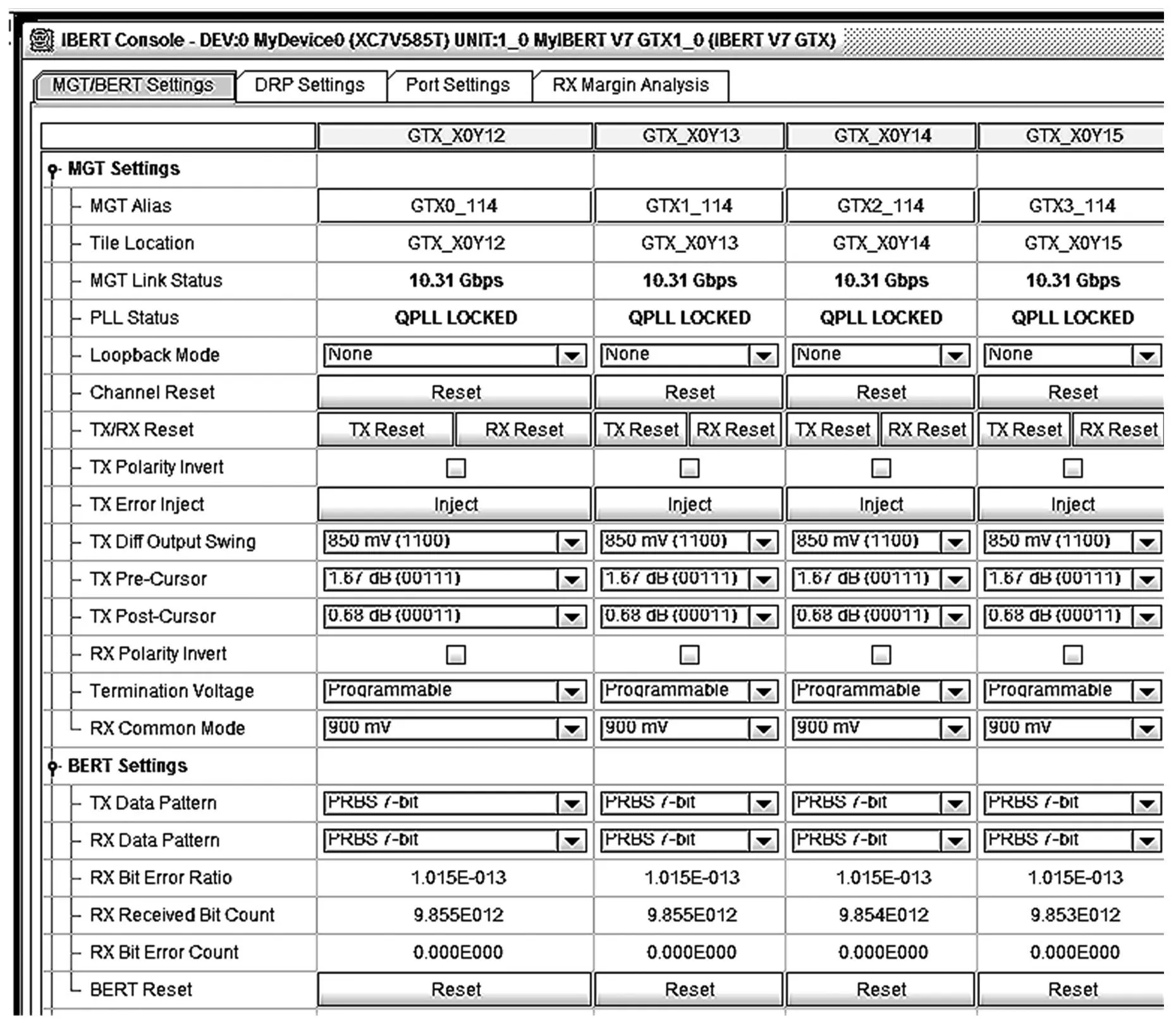

本文利用集成比特误码率测试仪(Integrated Bit Error Ratio Tester,IBERT)对数据链路进行测试,利用IBERT核即可生成bit文件[16],通过JTAG口下载到FPGA中,将ChipScope Analyzer连接到FPGA上,出现IBERT Console界面如图4所示。此测试工具可以实时调整每个GTX的参数,GTX接口均有一个动态重配置端口,所以每个GTX的属性都可以通过软件在线进行重新配置,可以直接修改预加重级别、输出电压摆幅和均衡[17]等参数测试误比特率。

图4 IBERT Console界面

在利用IBERT测试时,首先需要观察PLL Status的状态,如:状态为QPLL LOCKED,表示时钟锁定,GTX可以正常工作;状态是QPLL NOT LOCKED,表示未锁定,要检查GTX供电电压和参考时钟是否正常输入。本设计的参考时钟为200 MHz,设置的线速率10.312 5 Gbps和图4MGT Link Status界面显示一致。每个GTX可以产生多种伪随机二进制序列作为GTX的数据源。数据通过接收通道与发送通道发出的数据进行比较计算出比特误码率。在这里,测试时选用随机序列PRBS7,RX Received Bit Count栏显示为接收到的总比特数,RX Bit Error Count栏显示错误的比特数,当前显示为0。该测试是实时、动态的,误比特率一直维持在10-13量级。

在图4所示的RX Margin Analysis扫描界面,整个UI范围内进行采样点扫描测试时,信号眼图的眼睛张得越大,信道质量也就越好[18]。观察其中一个GTX的2D眼图如图5所示,它是通过色温的方式来显示眼图的[19],图中比特误码率达到10-9量级时的深色区域占了整个图形较大面积即眼睛张开较大。因此对于GTX,数据可以进行可靠传输。

图5 GTX的2D眼图

3.2 协议测试

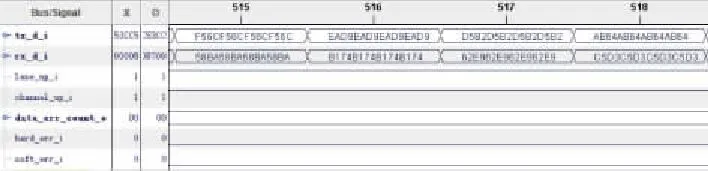

数据链路工作正常后,按照制定好的协议,测试2个板卡之间高速串行数据传输时的误比特率。系统主要包括数据成帧模块、帧数据发送模块、帧数据接收校验模块和时钟补偿模块[20]。发送端发送Aurora 64B/66B核内部产生的数据源,接收端接收相同机制的数据。

仿真结果如图6所示,系统初始化完成后状态信号channel_up_i和lane_up_i被拉高。错误指示信号hard_err_i和soft_err_i均为0,接收到数据的错误个数统计信号data_err_count_o显示为0,说明数据通道收发数据正确无误。该方案验证了板级间能够进行高速率串行传输。

图6 仿真结果

4 结束语

针对采用并行接口传输数据的速率较慢的问题,提出利用FPGA实时性强等特点,设计了SFP+光模块的硬件接口电路,实现了光纤通信这种高速串行传输方式。通过对FPGA内部Aurora 64B/66B核的配置和例化,实现了2个板卡之间高速串行通信,通过对板卡进行调试实现了两板间串行数据传输速率可达10 Gbps的无误传输。经过多次测试,板卡性能稳定,达到了设计要求,目前已应用于某型号的高速数传设备中。

该板卡通用性强,可移植性强,应用灵活,可以兼容低速率数据传输,节约了生产成本,缩短了研发周期。

[1] 陈平,杨建,王炬城.基于FPGA的高速光纤数据传输板卡的设计[J].信息通信,2015,145(1):79-80.

[2] 白月胜.基于FPGA的光纤传输系统的设计与实现[J].电子质量,2012(2):29-37.

[3] 秦艳召.基于Aurora协议的光传输方案验证[J].科学技术与工程,2012,30(12):8038-8041.

[4] 汪颖,王飚,辛华强,等.10 Gbit/s SFP+光收发模块[J].光电器件研究与应用,2009(3):35-37.

[5] 杜东海.基于SFP光电模块的高速数据存储器的设计和研究[D].山西:中北大学,2015.

[6] Xilinx.7 Series FPGAs Overview,America:Xilinx Inc[S],2012.

[7] Xilinx.7 Series FPGAs GTX/GTH Transceivers User Guide V1.11,America:Xilinx Inc[S],2015.

[8] 聂嵩.基于10 Gbps的SFP光通信系统模块的设计与实现[D].北京:北京工业大学,2014.

[9] 雷声振.基于FPGA的数字视频光纤传输系设计与实现[J].电子世界,2016(6):93-94.

[10] 王丽娟,李锦明,杜东海.基于FPGA的SFP光纤通信控制器的研究与设计[J].电子器件,2016,39(3):605-609.

[11] 于争.信号完整性揭秘[M].北京:机械工业出版社,2013.

[12] Xilinx.LogiCORE IP Aurora 64B/66B Product Guide V7.3,America:Xilinx Inc[S],2012.

[13] 王长清,冀映辉,王维,等.基于PCI-Express和Aurora协议高速光纤通信板卡的实现[J].微计算机应用,2010,31(1):64-68.

[14] 韩俊波,李和平.基于FPGA的前向纠错并行光纤传输系统设计与实现[J].科学技术与工程,2012,2(13):3121-3125.

[15] 赵英潇,张月,戴华骅,等.Virtex-6 FPGA的三种串行通信协议测试及对比[J].单片机与嵌入式系统应用,2014(10):53-56.

[16] 苏秀妮.基于RocketIO高速串行通信接口的研究与实现[D].西安:西安电子科技大学,2013.

[17] 余鑫,李跃忠.基于IBERT在Vritex-7 GTX的测试实验研究[J].电子科技,2015,28(3):91-93.

[18] 徐妍,马丽珍,张丽.IBERT在FPGA中的应用[J].电子科技,2012,25(7):103-105.

[19] 王仲蔚,刁节涛,李楠.一种板级高速串行传输接口设计[J].通信技术,2015(1):22-24.

[20] 何少恒.基于SFP光纤通信接口的高速IQ数据传输系统设计与实现[D].山西:中北大学,2016.

TheDesignandImplementationofHigh-speedDataTransmissionInterfacebetweenBoards

HUA Sha,LI Feng,WU Lei-lei

(The54thResearchInstituteofCETC,ShijiazhuangHebei050081,China)

TN911

A

1003-3106(2017)11-0079-04

滑莎女,(1984—),硕士,工程师。主要研究方向:高速调制解调器设计。

10.3969/j.issn.1003-3106.2017.11.17

滑莎,李锋,武磊磊.板间高速数据传输接口的设计与实现[J].无线电工程,2017,47(11):79-82.[HUA Sha,LI Feng,WU Leilei.The Design and Implementation of High-speed Data Transmission Interface between Boards[J].Radio Engineering,2017,47(11):79-82.]

2017-02-28

国家部委基金资助项目。

李锋男,(1986—),硕士,助理工程师。主要研究方向:高速调制解调器设计。